VDMOS (Vertical Double-diffusion Metal Oxide Semiconductor Structure) device and manufacturing method thereof

A device manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of low theoretical value of electrical properties of VDMOS devices, and achieve improved electrical properties, reduced occupied area, and improved The effect of utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

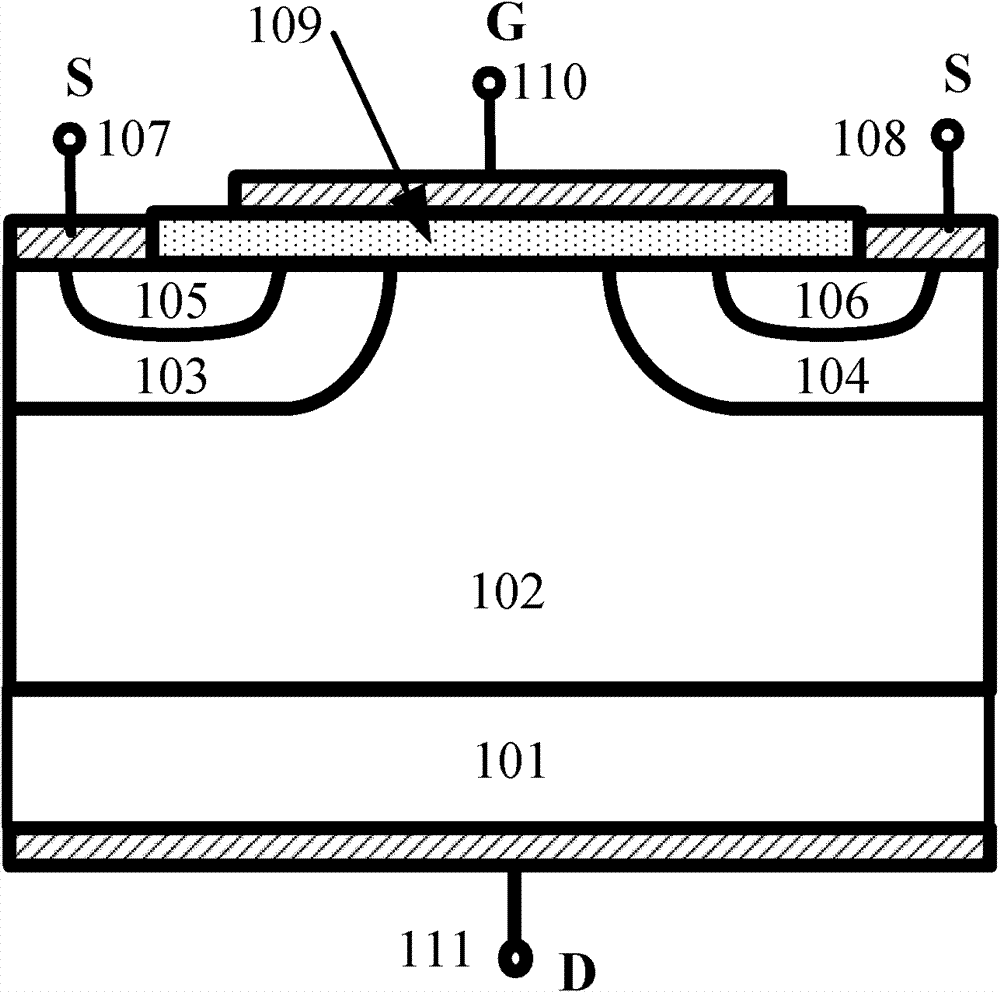

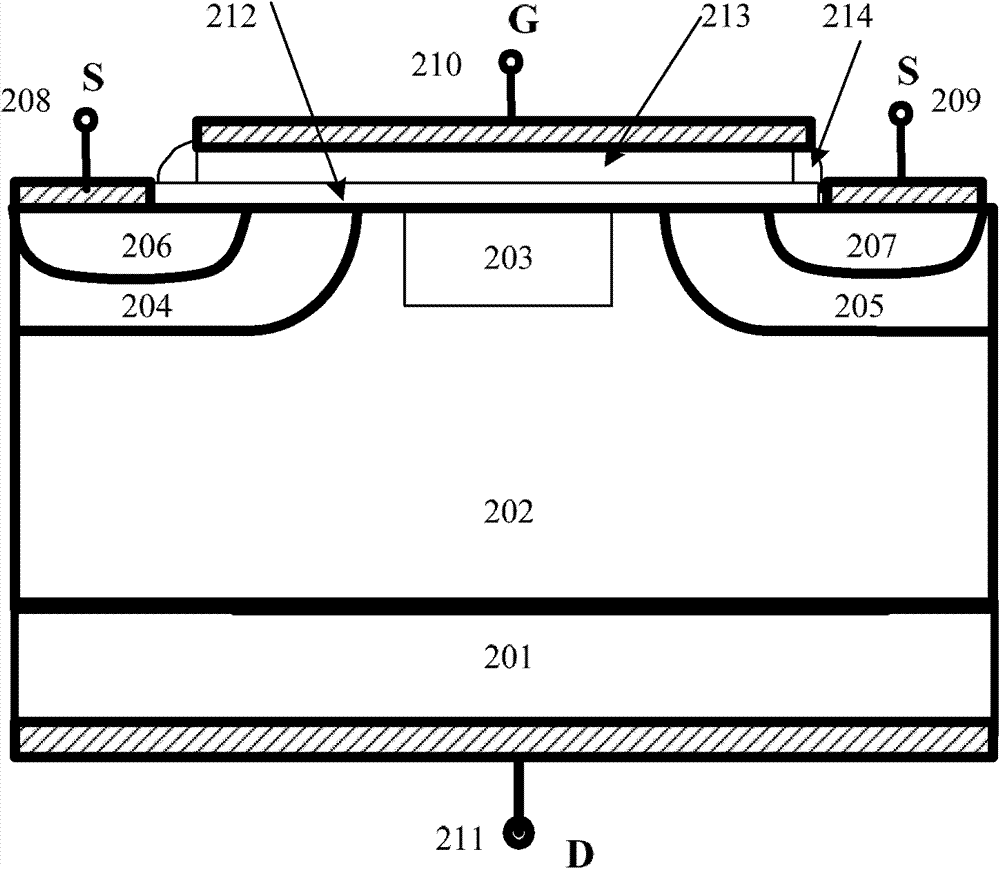

[0046] Based on this, Embodiment 1 of the present invention provides a VDMOS device, the structure of which is as follows figure 2 shown, including:

[0047] a substrate, the substrate includes a body layer 201 and an epitaxial layer 202 located on the body layer, the body layer includes a drain region;

[0048] The isolation region 203 located in the epitaxial layer 202, generally, the isolation region 203 is located in the surface of the epitaxial layer 202, and there is no isolation region material on the surface of the epitaxial layer 202;

[0049] The first body region 204 and the second body region 205 in the epitaxial layer located on both sides of the isolation region 203 have the same doping state as the epitaxial layer. The conductivity type of doping ions is opposite;

[0050] The first source region 206 located in the first body region 204, the second source region 207 located in the second body region 205, the doping states of the first source region 206 and th...

Embodiment 2

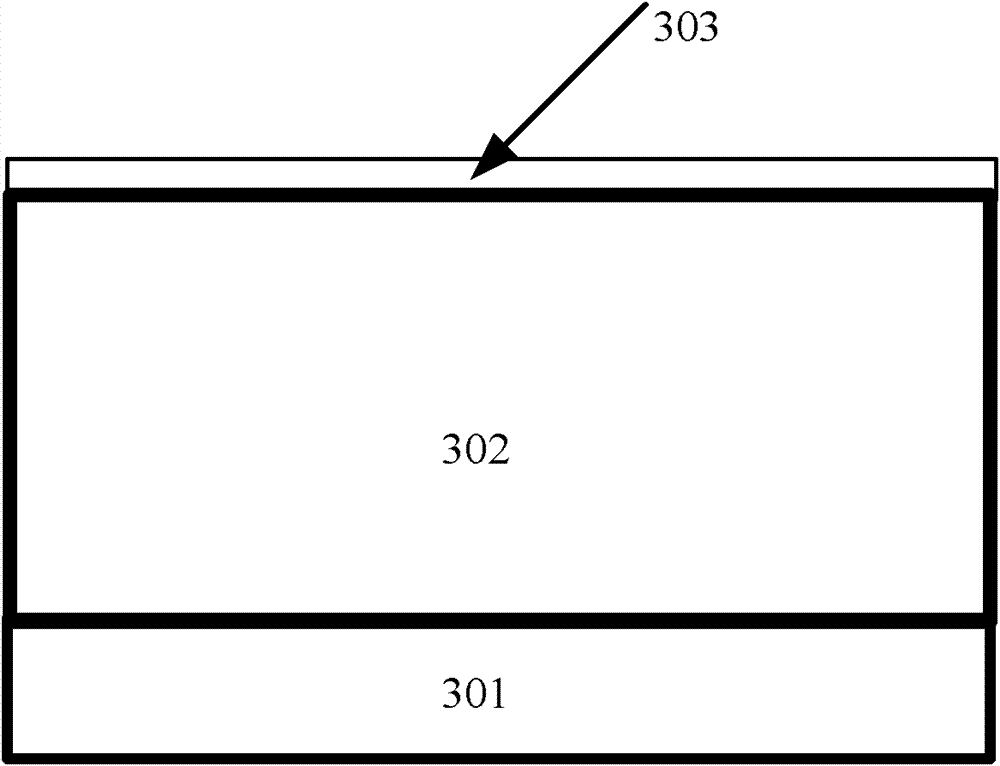

[0064] This embodiment discloses the manufacturing method of the VDMOS device described in the previous embodiment, Figure 3 to Figure 12 It is a sectional view of each step of the method, and the present embodiment only takes an N-type VDMOS device as an example for illustration, and the method includes the following steps:

[0065] Such as image 3 As shown, a substrate is provided, the substrate includes a bulk layer 301 and an epitaxial layer 302 above the bulk layer 301, the bulk layer 301 includes a drain region, and the bulk layer 301 and the epitaxial layer 302 in this embodiment are N-type doped ;

[0066] It should be noted that the substrate in this embodiment may include semiconductor elements, such as silicon or silicon germanium (SiGe) in single crystal, polycrystalline or amorphous structure, and may also include mixed semiconductor structures, such as silicon carbide, indium antimonide , lead telluride, indium arsenide, indium phosphide, gallium arsenide or ...

Embodiment 3

[0092] The VDMOS device manufacturing method disclosed in this embodiment is different from the method for forming an isolation region in the previous embodiment. In this embodiment, the step of forming the isolation region in the surface of the epitaxial layer includes:

[0093] Step 1: forming an opening in the surface of the epitaxial layer;

[0094] In this embodiment, a photolithography process can be used to form an opening pattern on the surface of the epitaxial layer, and then the photoresist layer with the opening is used as a mask to etch away the epitaxial layer material at the opening, so that Form the opening.

[0095] Step 2: covering the surface of the epitaxial layer with an isolation layer to fill the opening with an isolation layer material;

[0096] In this embodiment, chemical vapor deposition or physical vapor deposition can be used to cover the surface of the epitaxial layer with an isolation layer, and HDP (high density plasma chemical vapor deposition)...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com