Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30results about How to "Resistant to noise" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

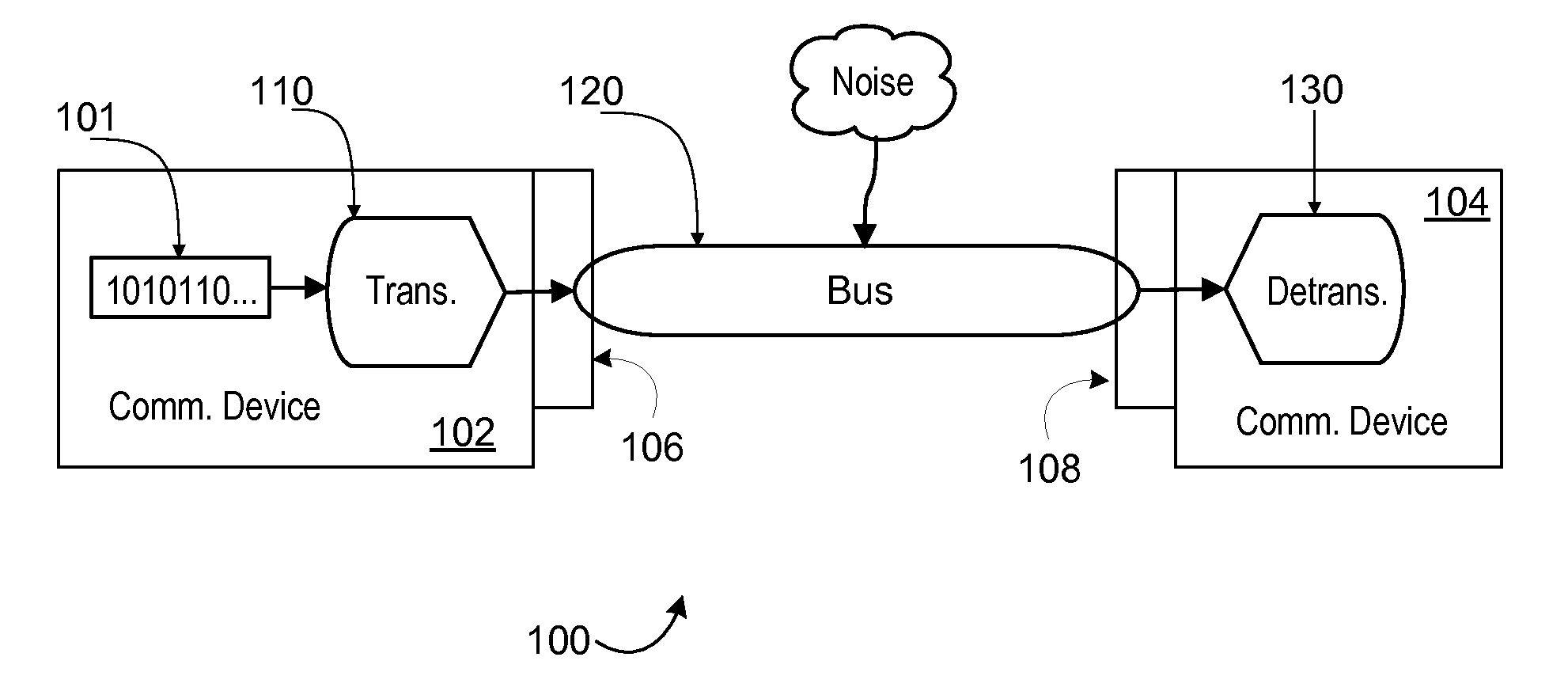

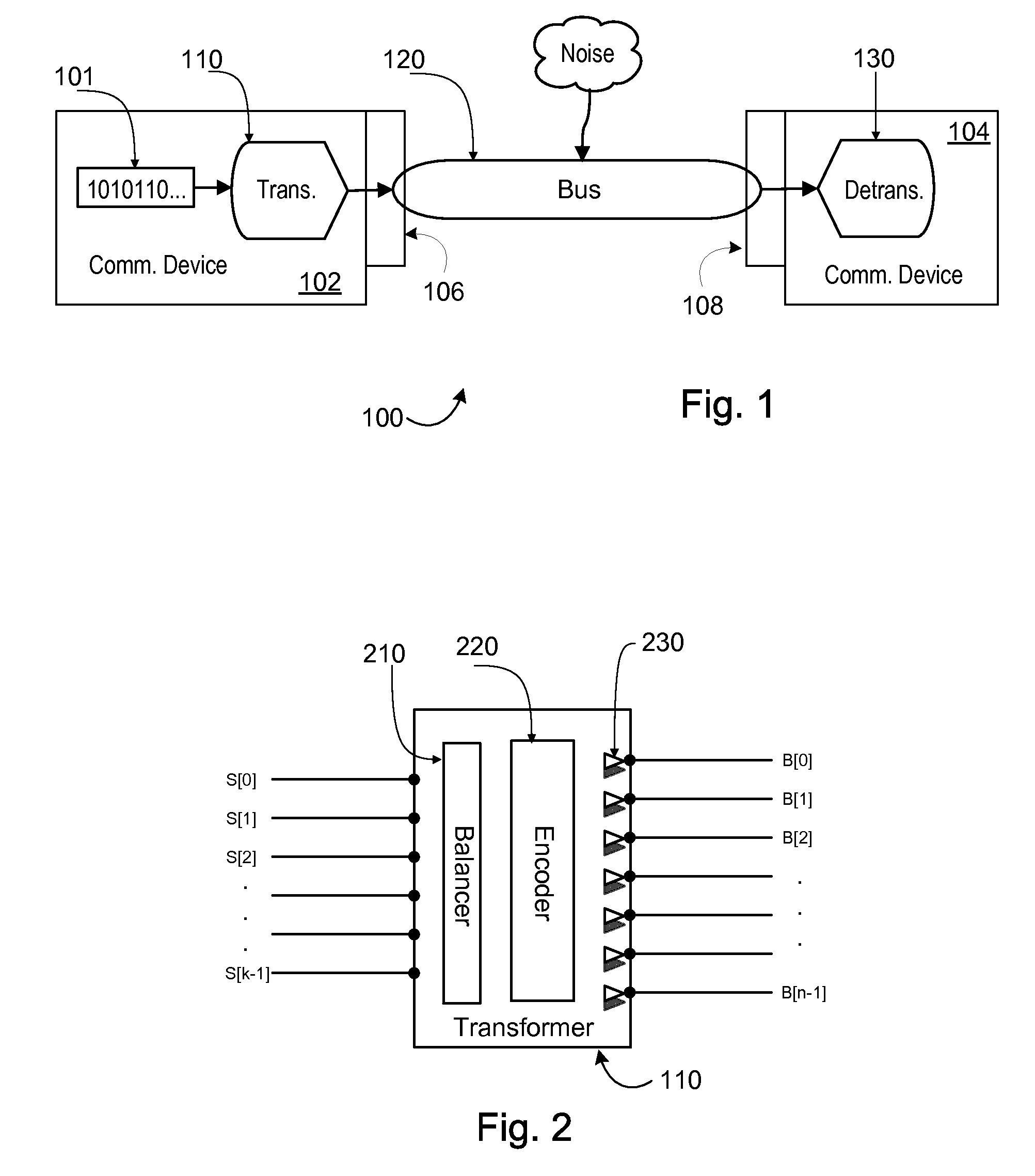

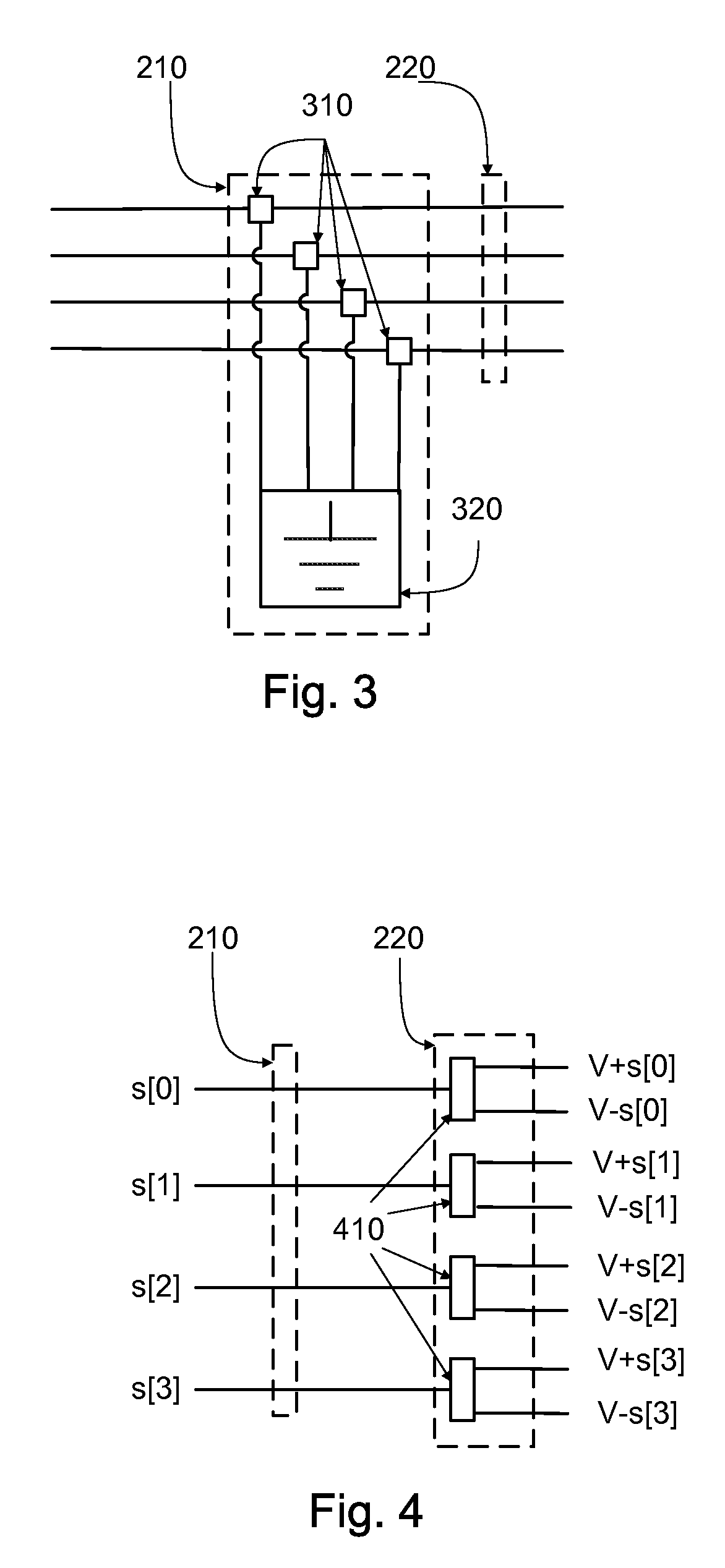

Orthogonal differential vector signaling

ActiveUS9288089B2Increase valueImprove energy consumptionBaseband system detailsTransmission path divisionPhysical spaceAlgorithm

Using a transformation based at least in part on a non-simple orthogonal or unitary matrix, data may be transmitted over a data bus in a manner that is resilient to one or more types of signal noise, that does not require a common reference at the transmission and acquisition points, and / or that has a pin-efficiency that is greater than 50% and may approach that of single-ended signaling. Such transformations may be implemented in hardware in an efficient manner. Hybrid transformers that apply such transformations to selected subsets of signals to be transmitted may be used to adapt to various signal set sizes and / or transmission environment properties including noise and physical space requirements of given transmission environments.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

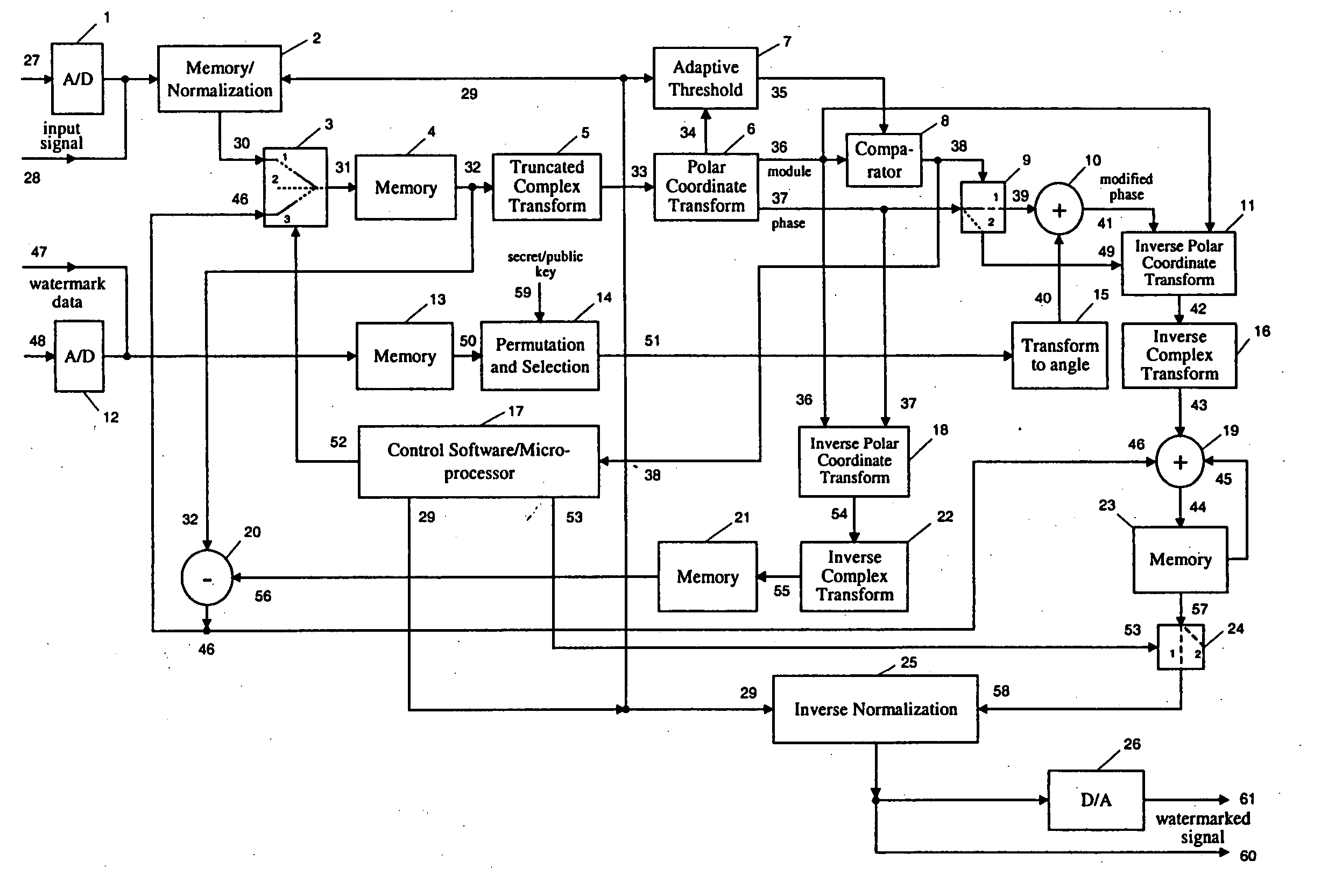

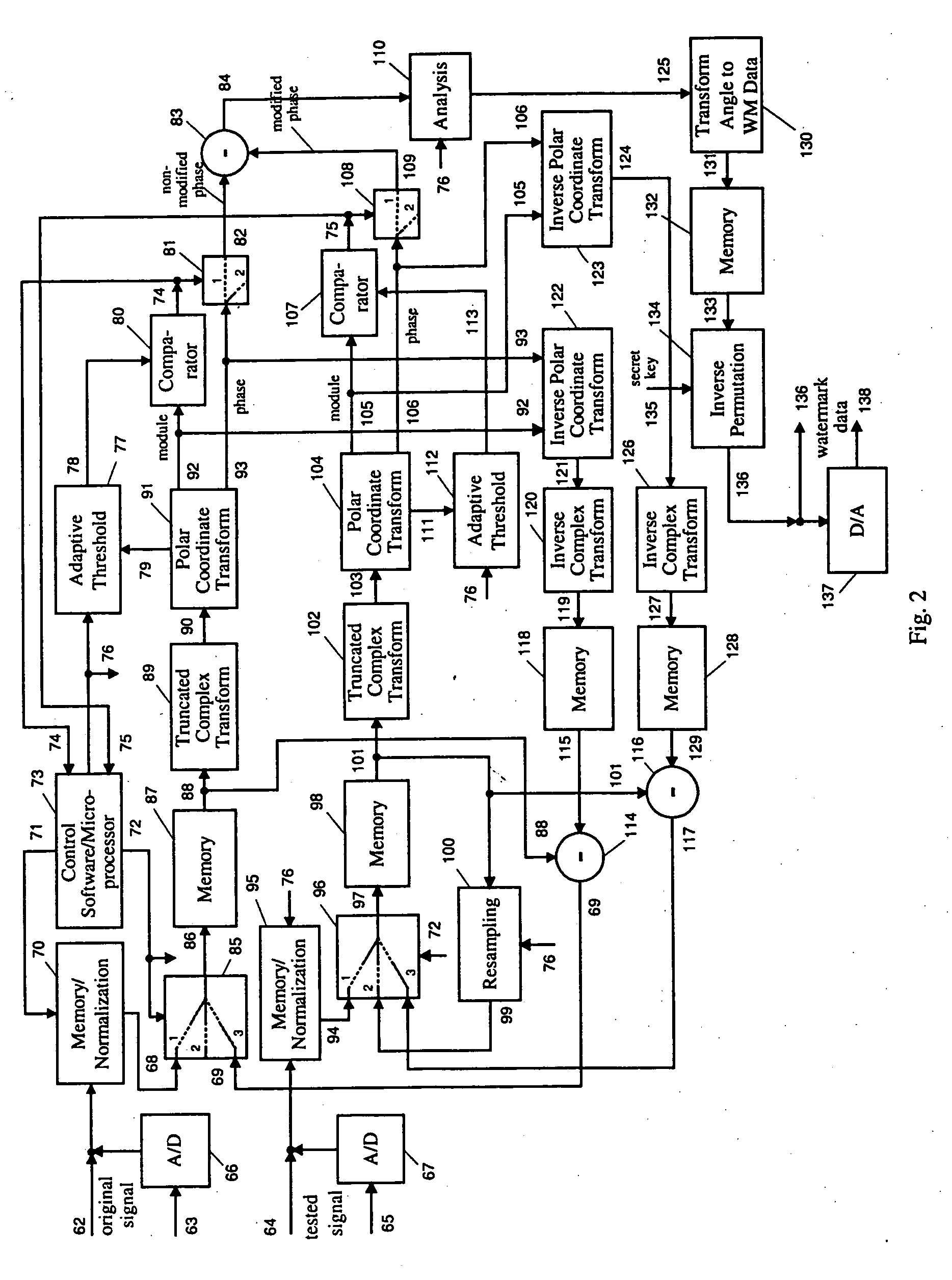

Method and system for digital watermarking of multimedia signals

InactiveUS20070014428A1High resistanceResistant to noiseCharacter and pattern recognitionImage data processing detailsDecompositionPyramid

Disclosed is a method and system for digital watermarking of multimedia signals. The input multimedia signal is represented using an inverse difference pyramid decomposition. Spectrum coefficients may be calculated for each level of the pyramid using a new kind of complex Hadamard transform, the matrix of which is distinguished from the known ones by the fact that only one-fourth of its coefficients are complex numbers. The phases of a previously selected part of the low-frequency coefficients are modified with the watermark data, limiting the angles of the phase changes in a gap of several degrees only. After an inverse complex Hadamard Transform, the values of the coefficients from all pyramid levels are summed up and the result is the watermarked signal. The watermark can contain multiple independent levels for each level of the pyramid.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ARKANSAS

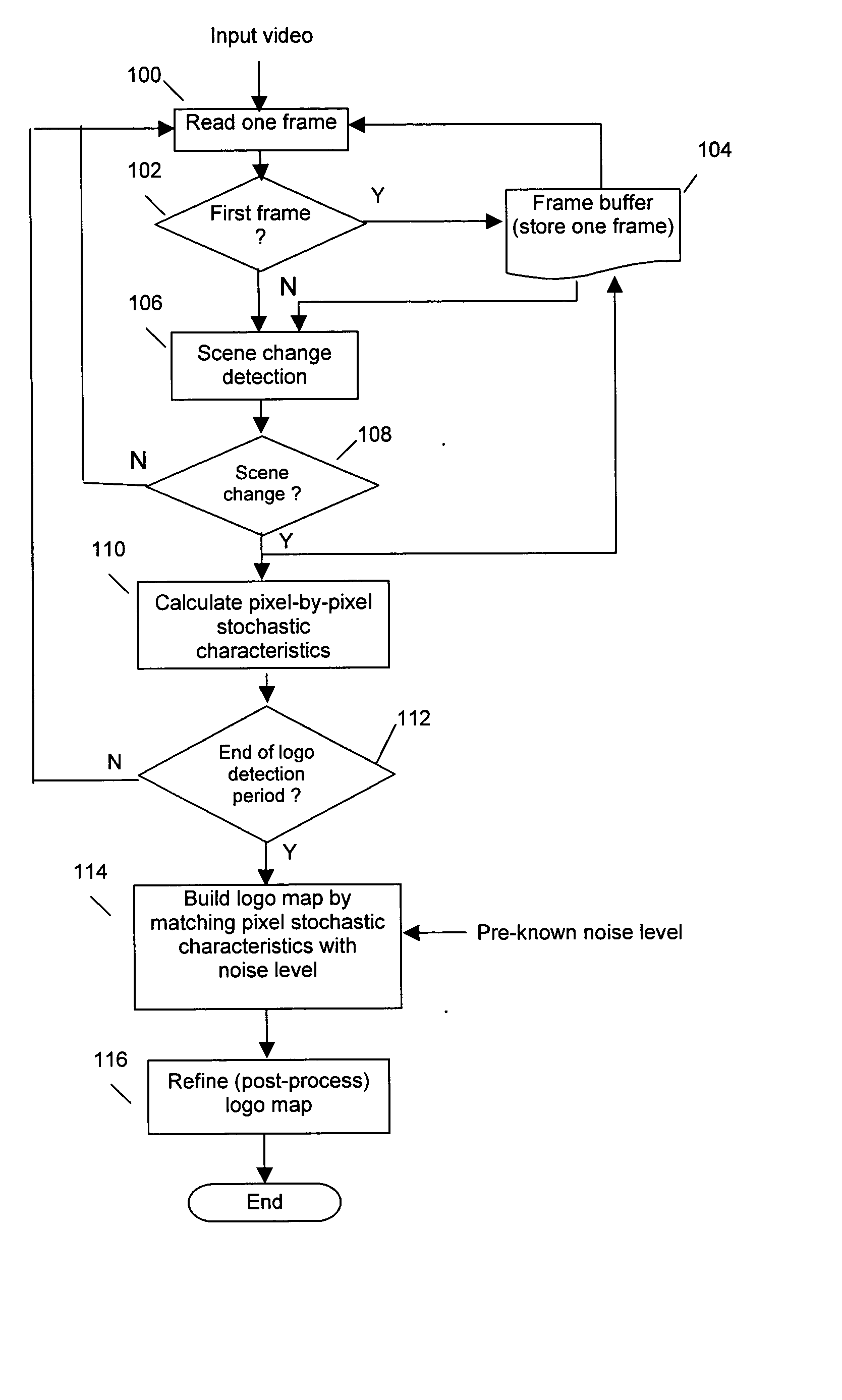

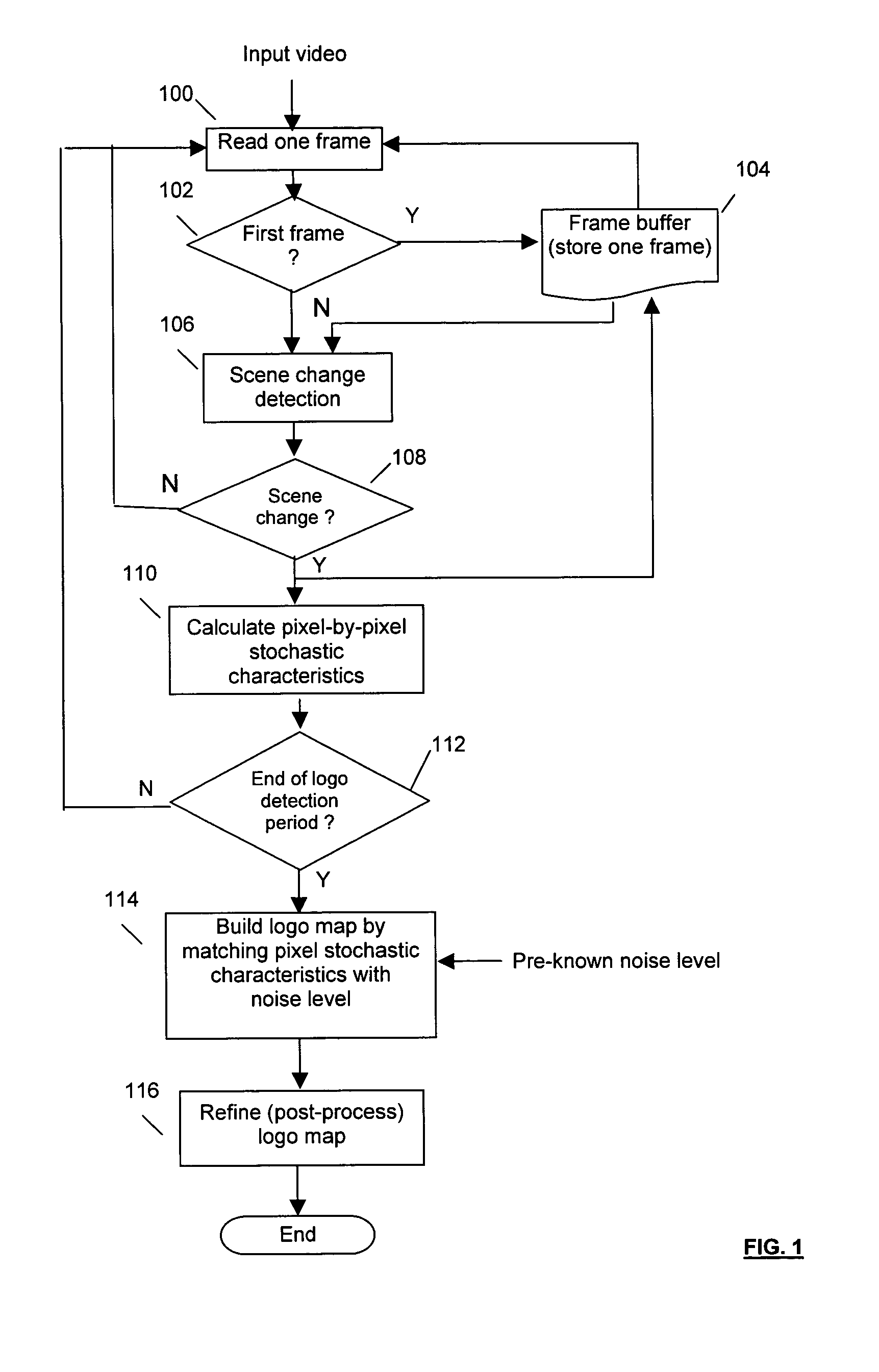

Apparatus and method for detecting opaque logos within digital video signals

InactiveUS20050078222A1Resistant to noiseTelevision system detailsPicture reproducers using cathode ray tubesPattern recognitionDigital video

A detection method and system that allows detecting an opaque logo after it has appeared in the digital video program for a short period of time, by deriving and analyzing the stochastic characteristics of the video signal along the temporal axis.

Owner:SAMSUNG ELECTRONICS CO LTD

Apparatus and method for detecting opaque logos within digital video signals

InactiveUS7483484B2Resistant to noiseTelevision system detailsPicture reproducers using cathode ray tubesPattern recognitionDigital video

A detection method and system that allows detecting an opaque logo after it has appeared in the digital video program for a short period of time, by deriving and analyzing the stochastic characteristics of the video signal along the temporal axis.

Owner:SAMSUNG ELECTRONICS CO LTD

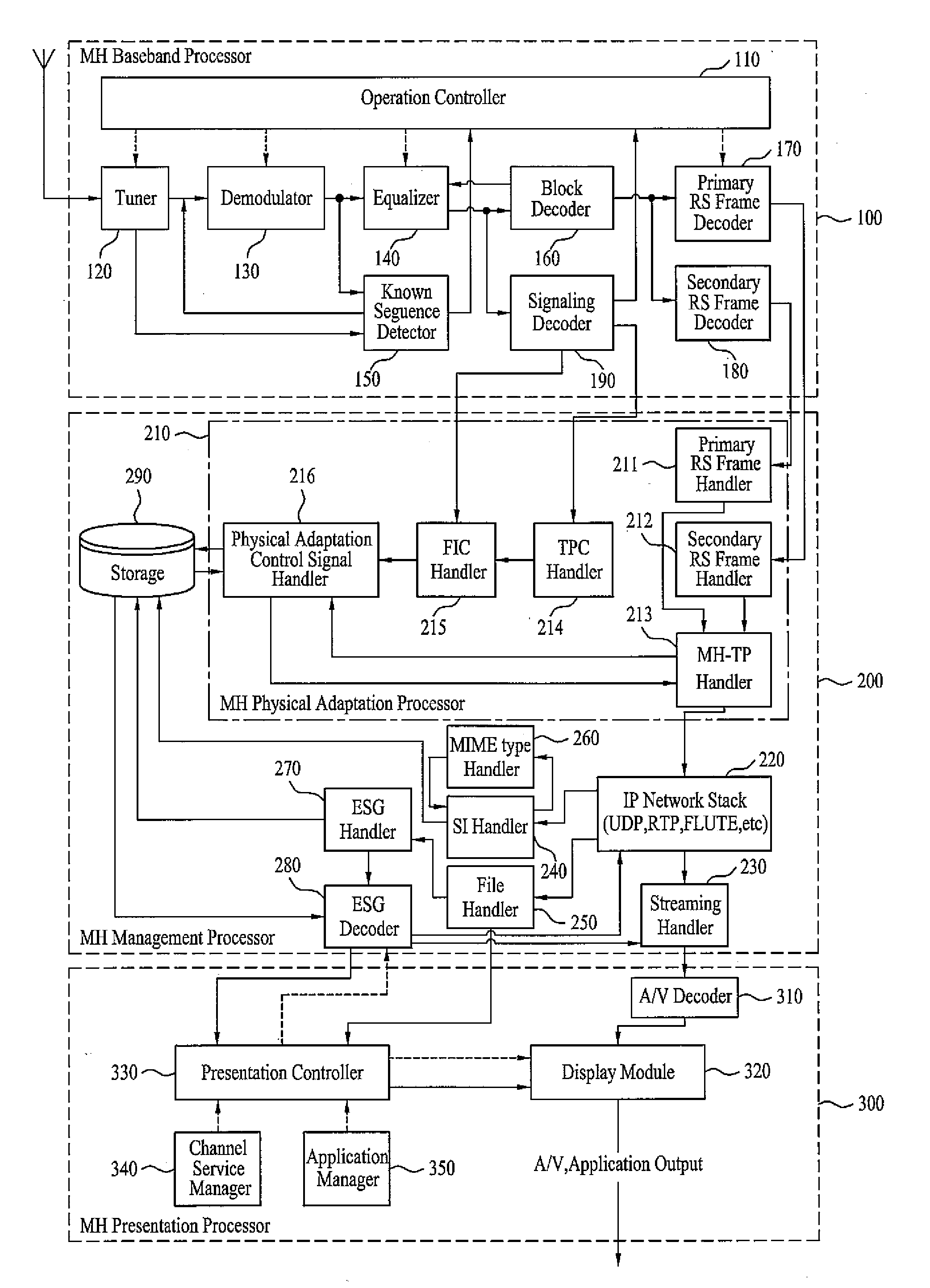

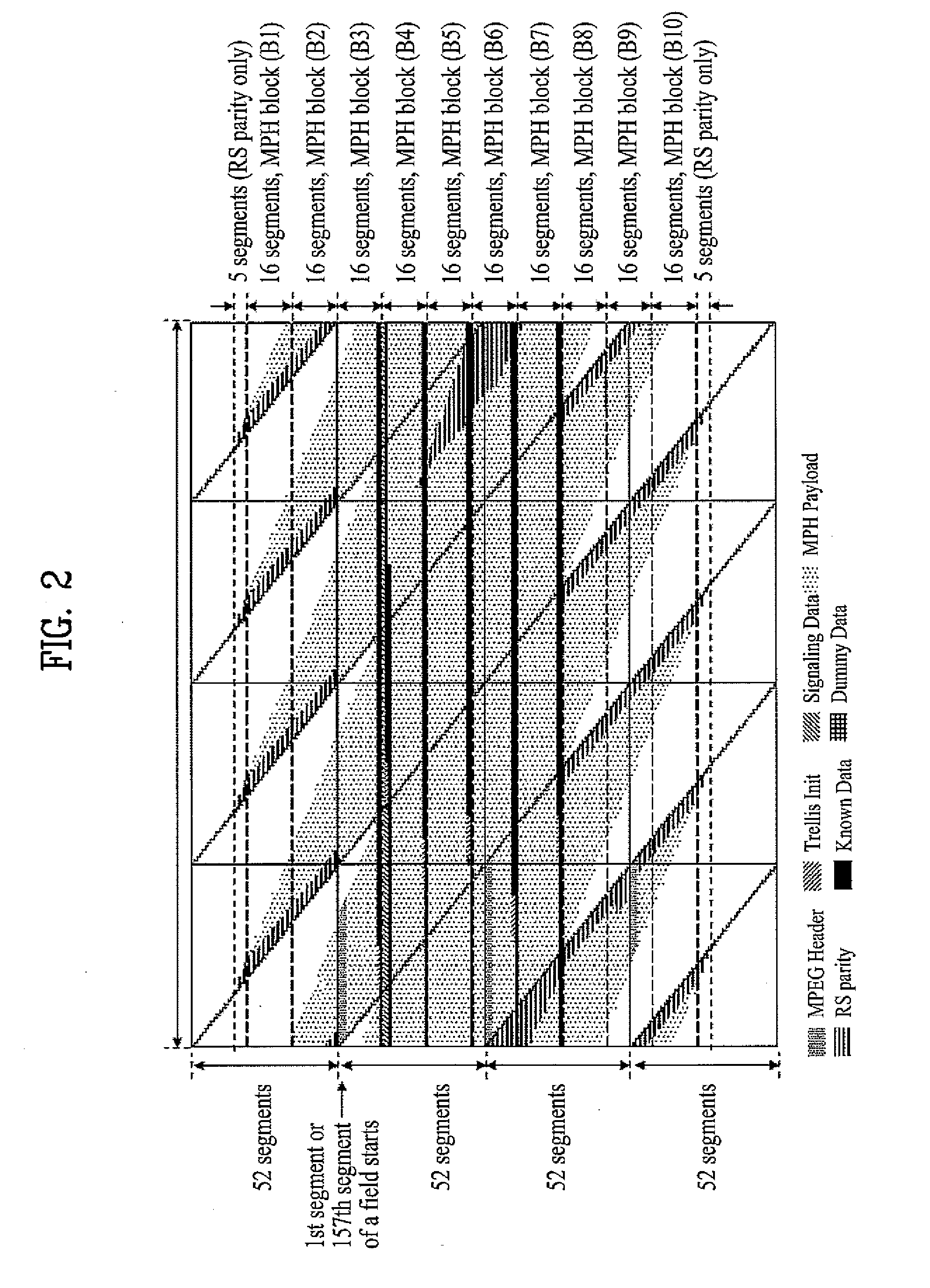

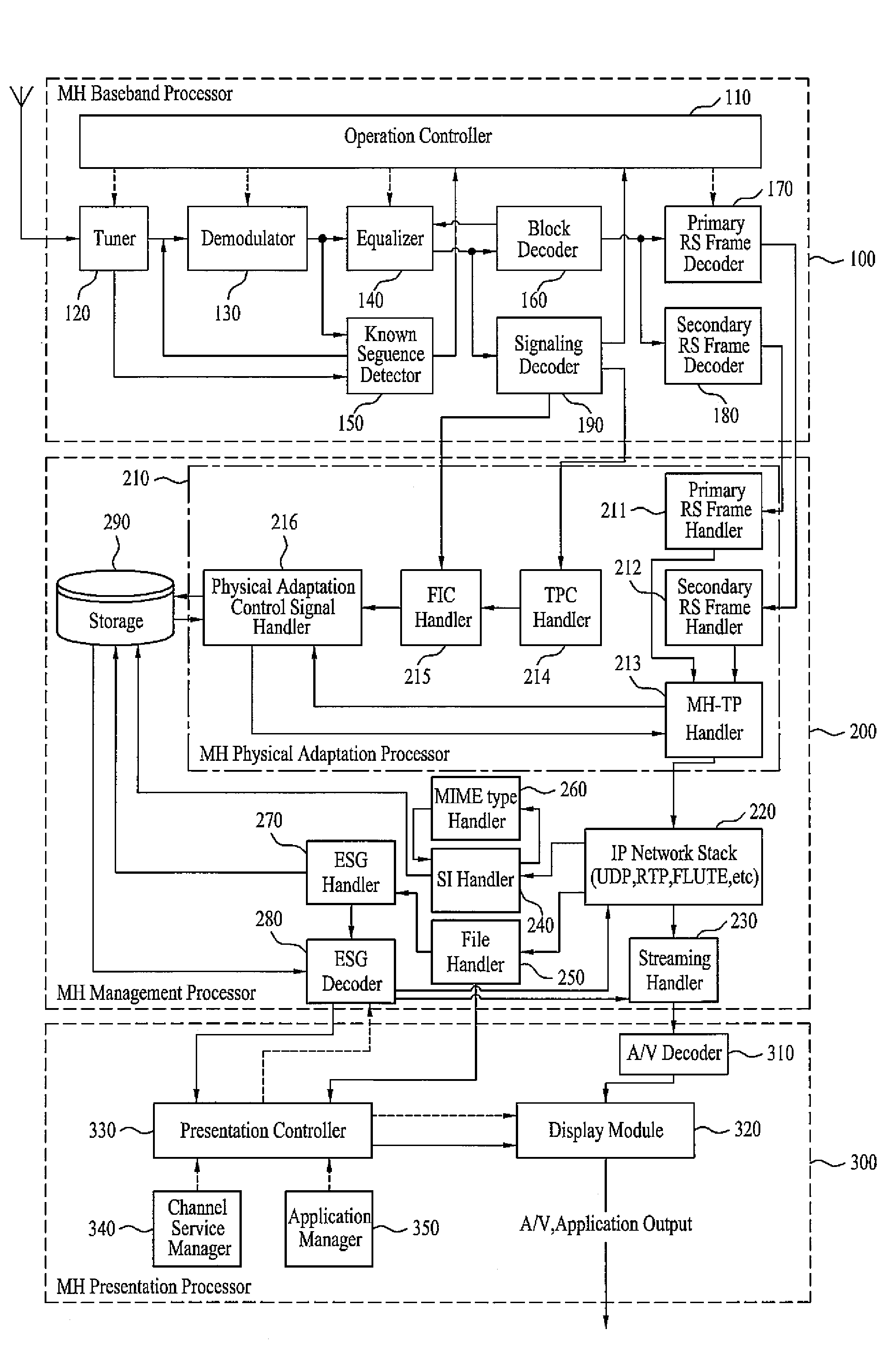

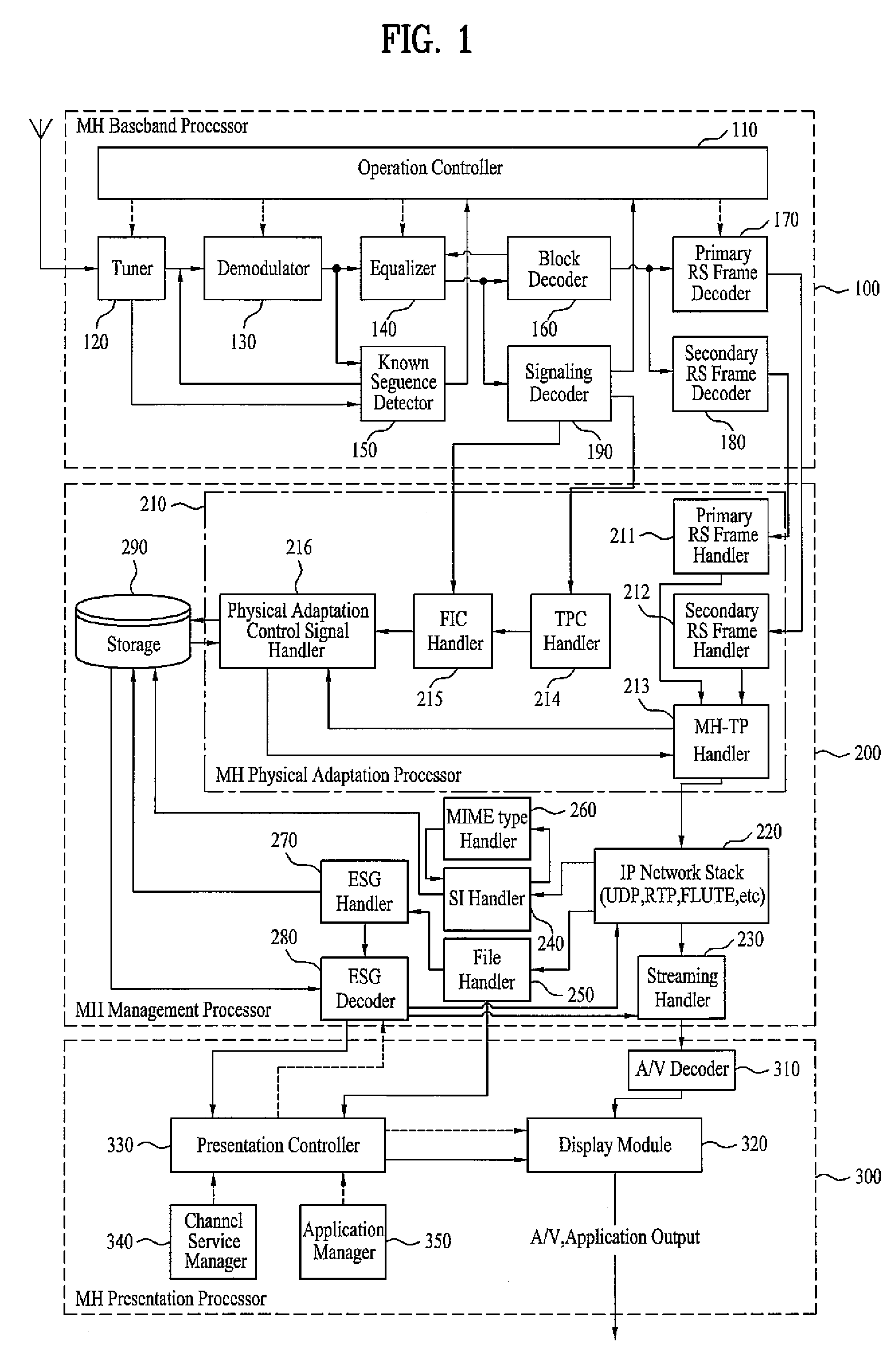

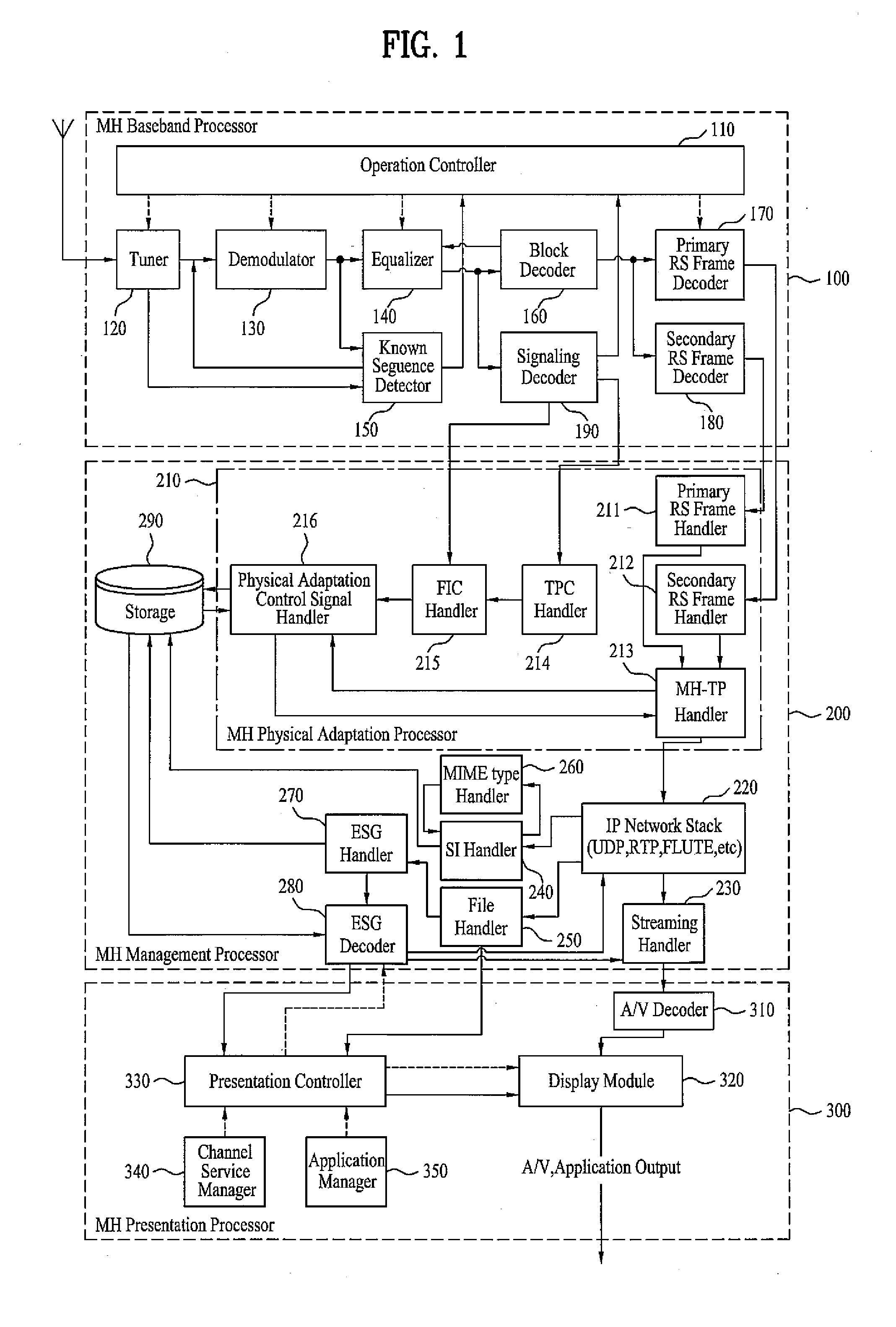

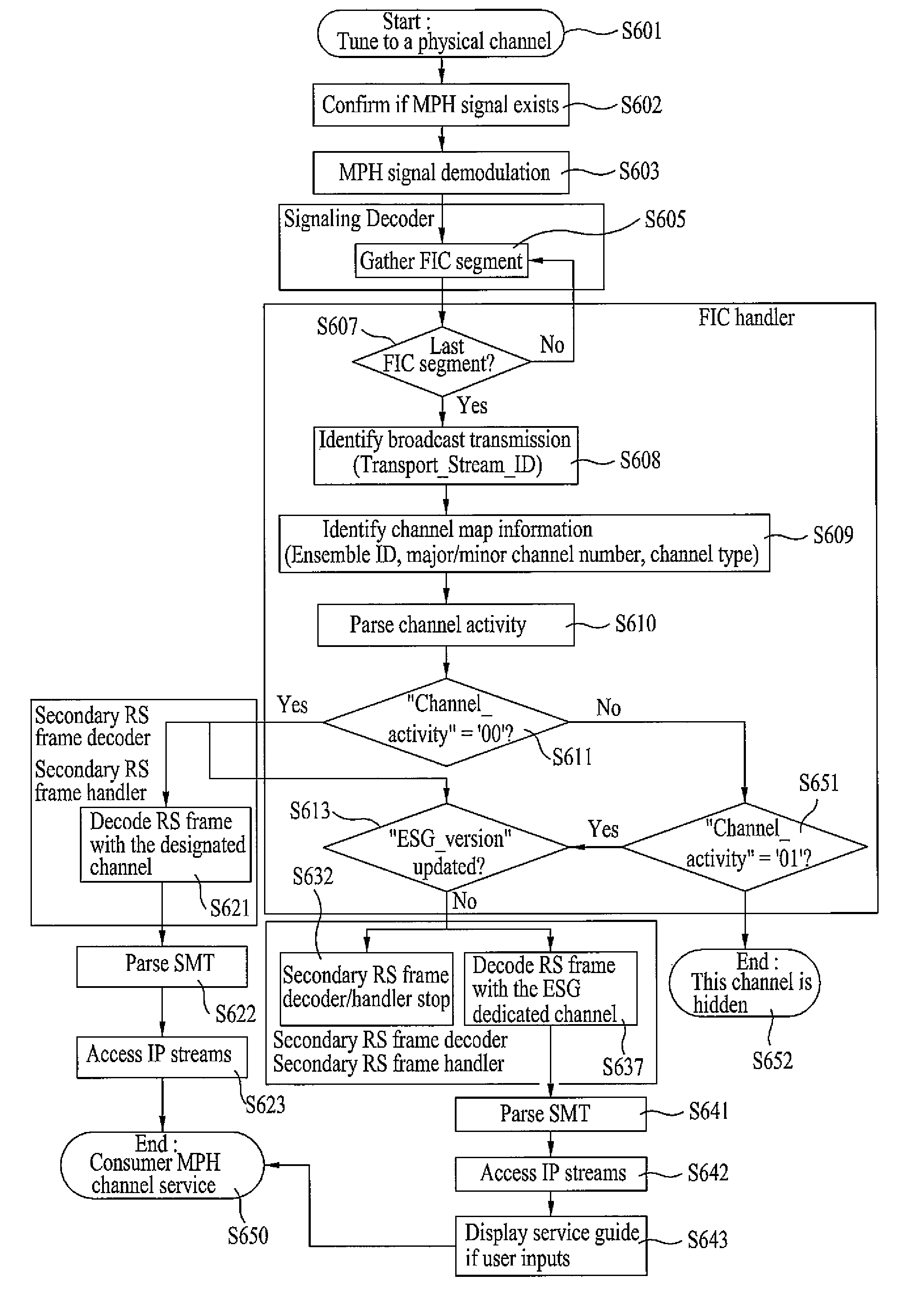

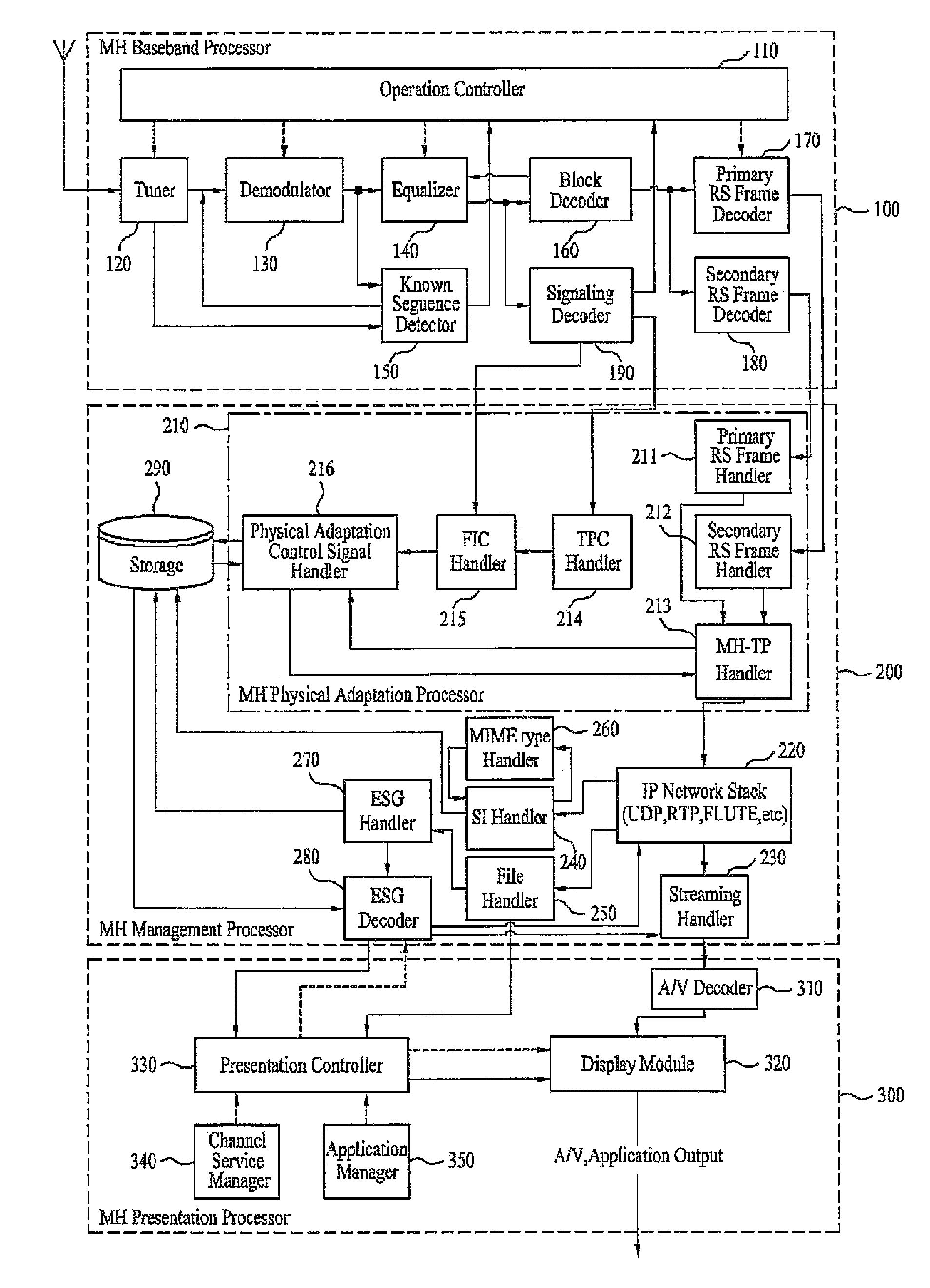

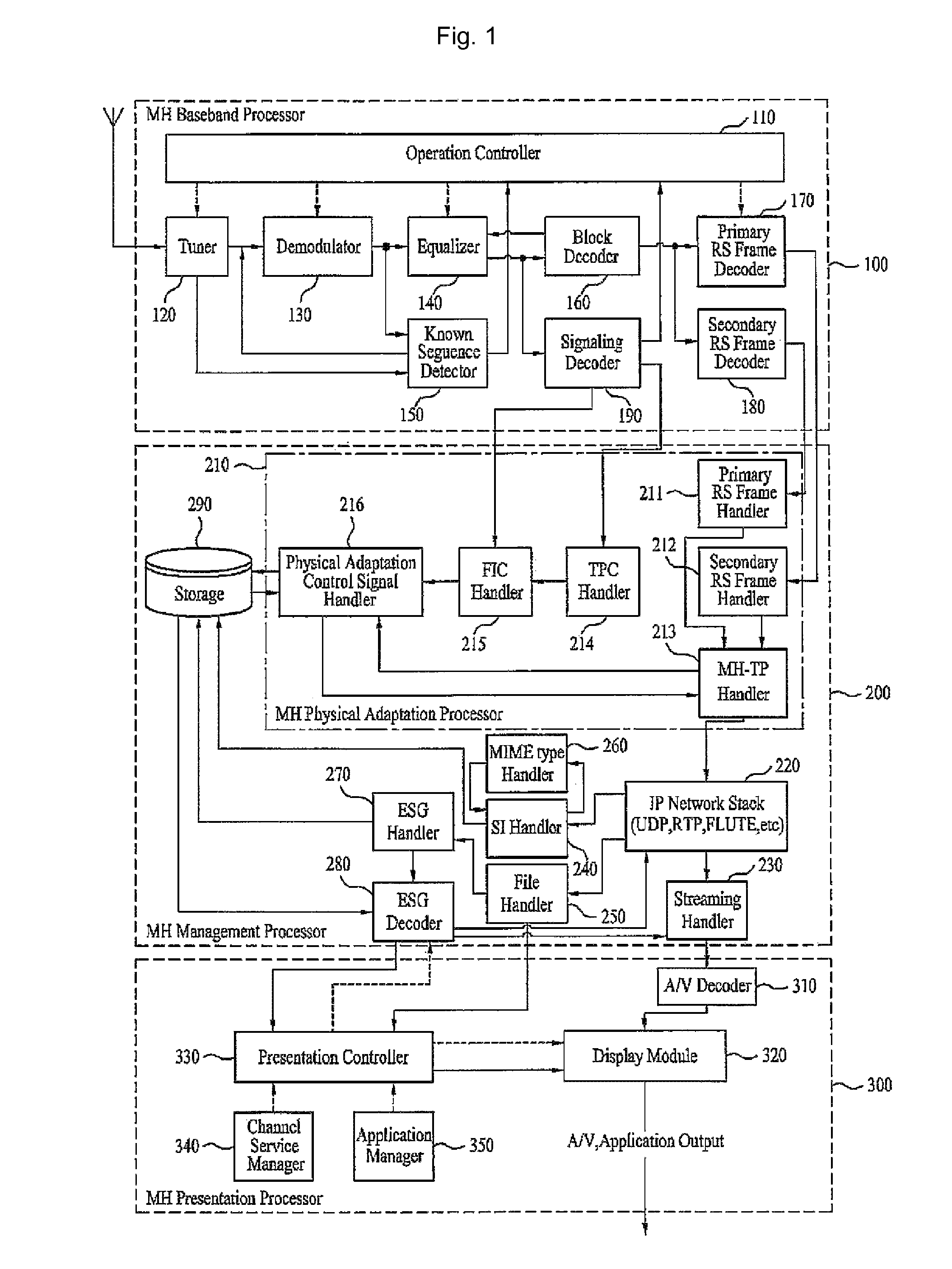

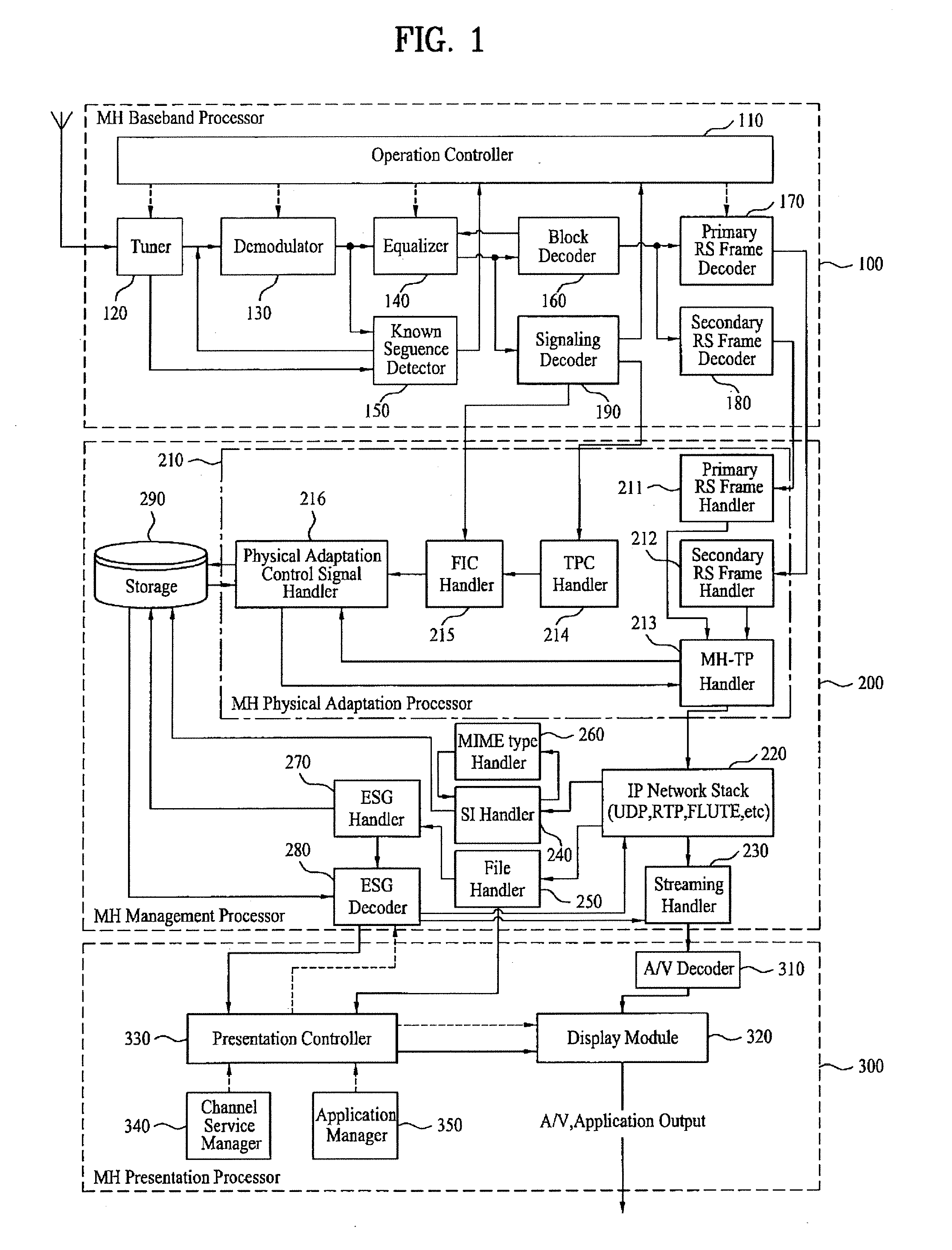

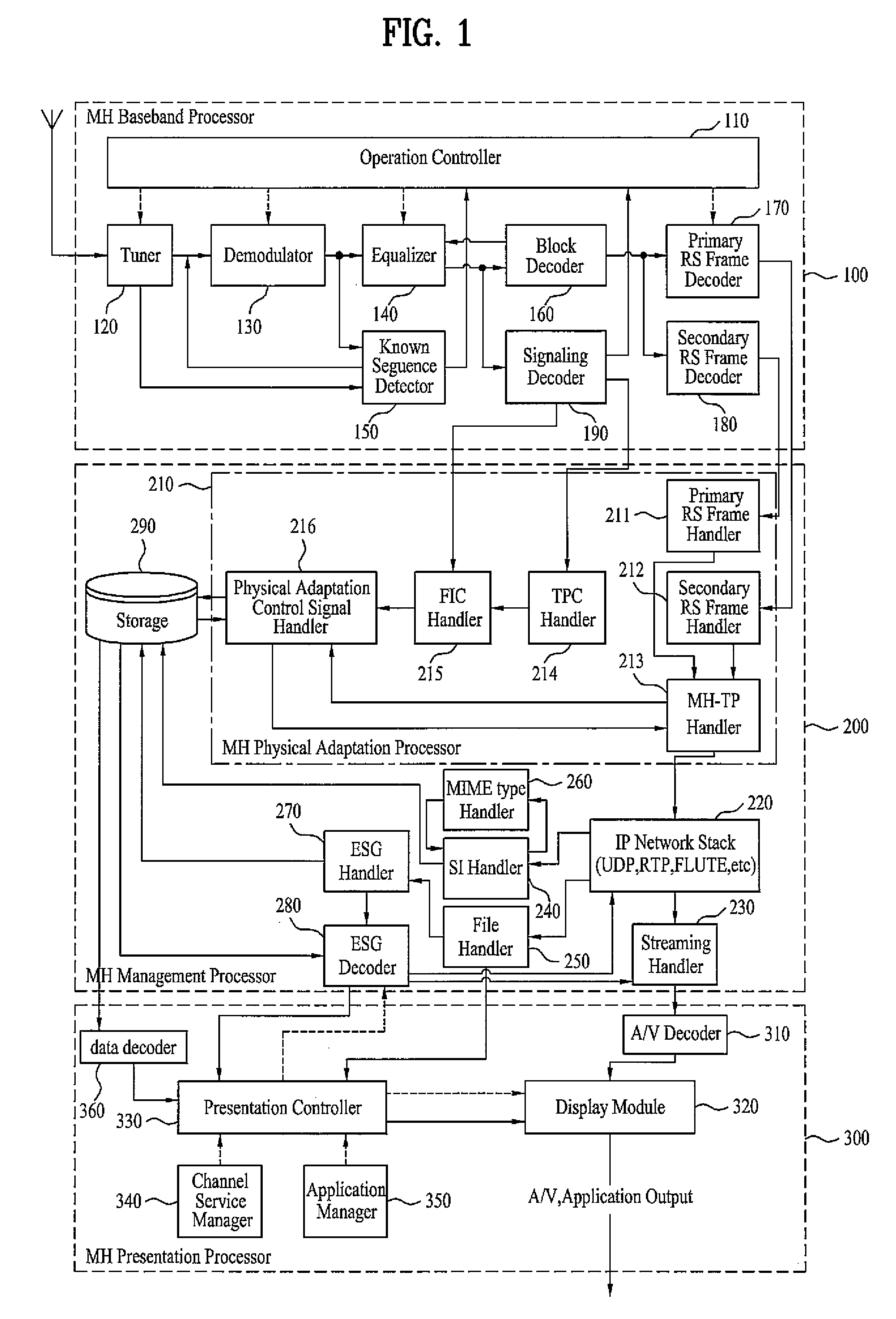

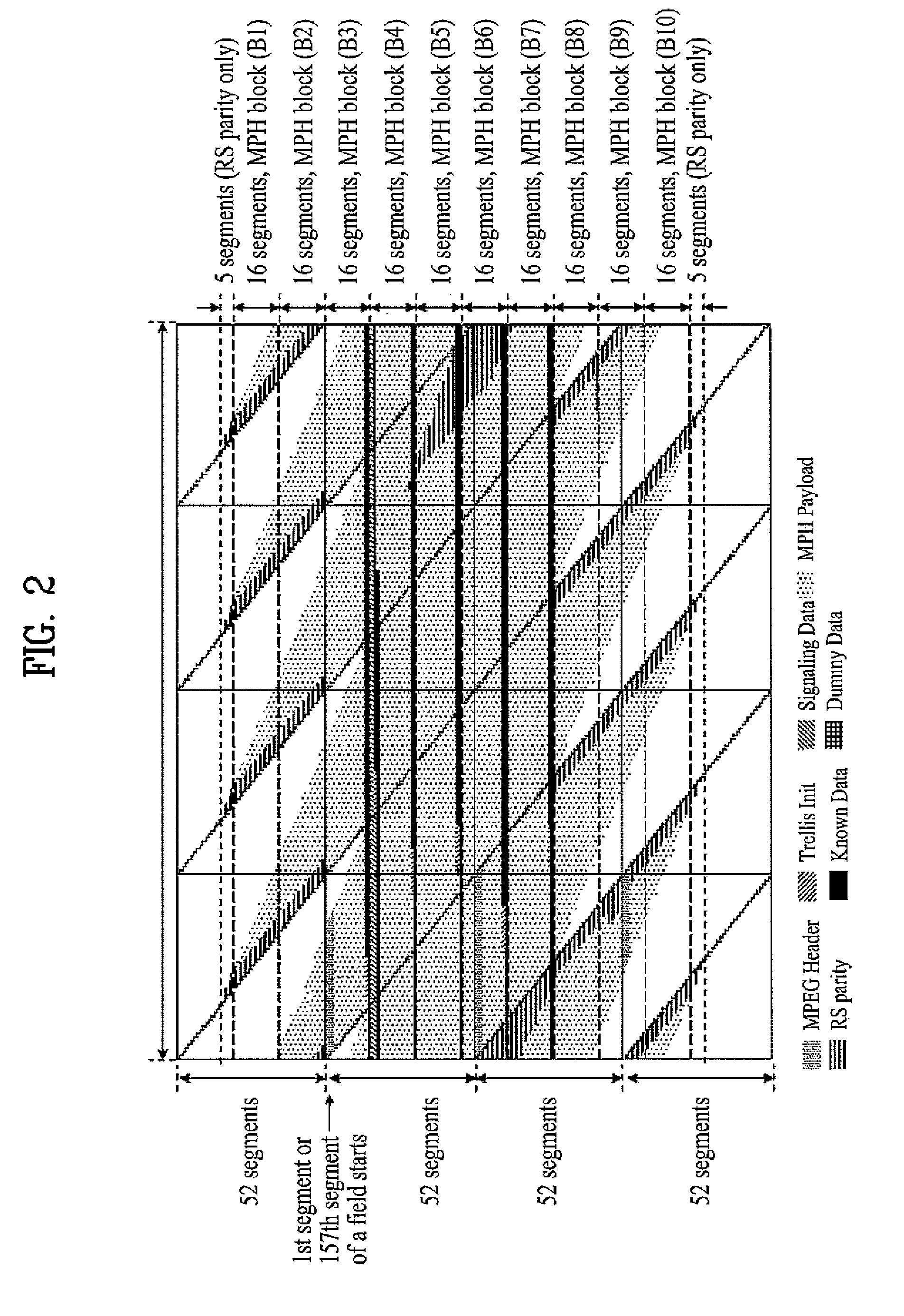

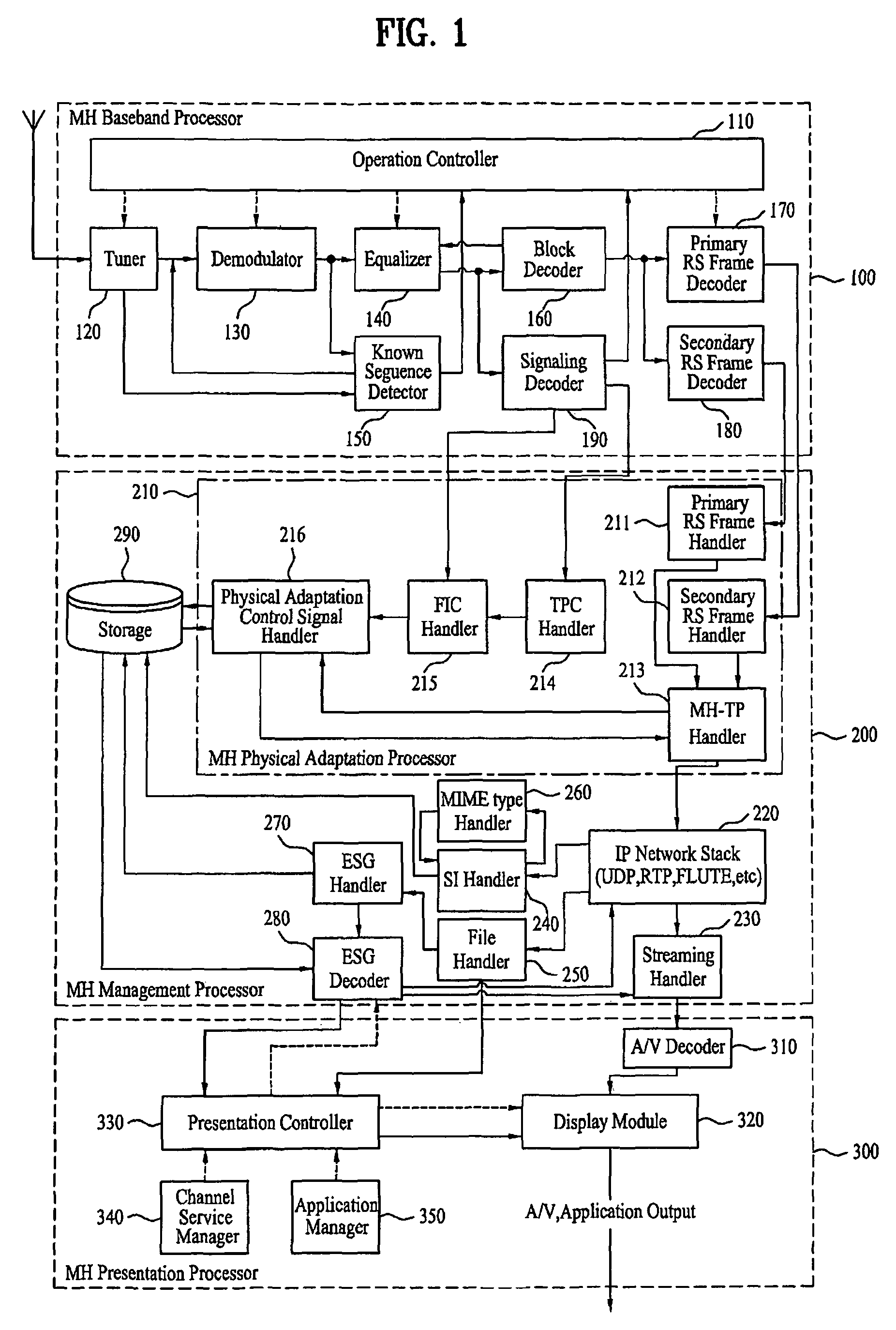

Digital broadcasting system and method of processing data in digital broadcasting system

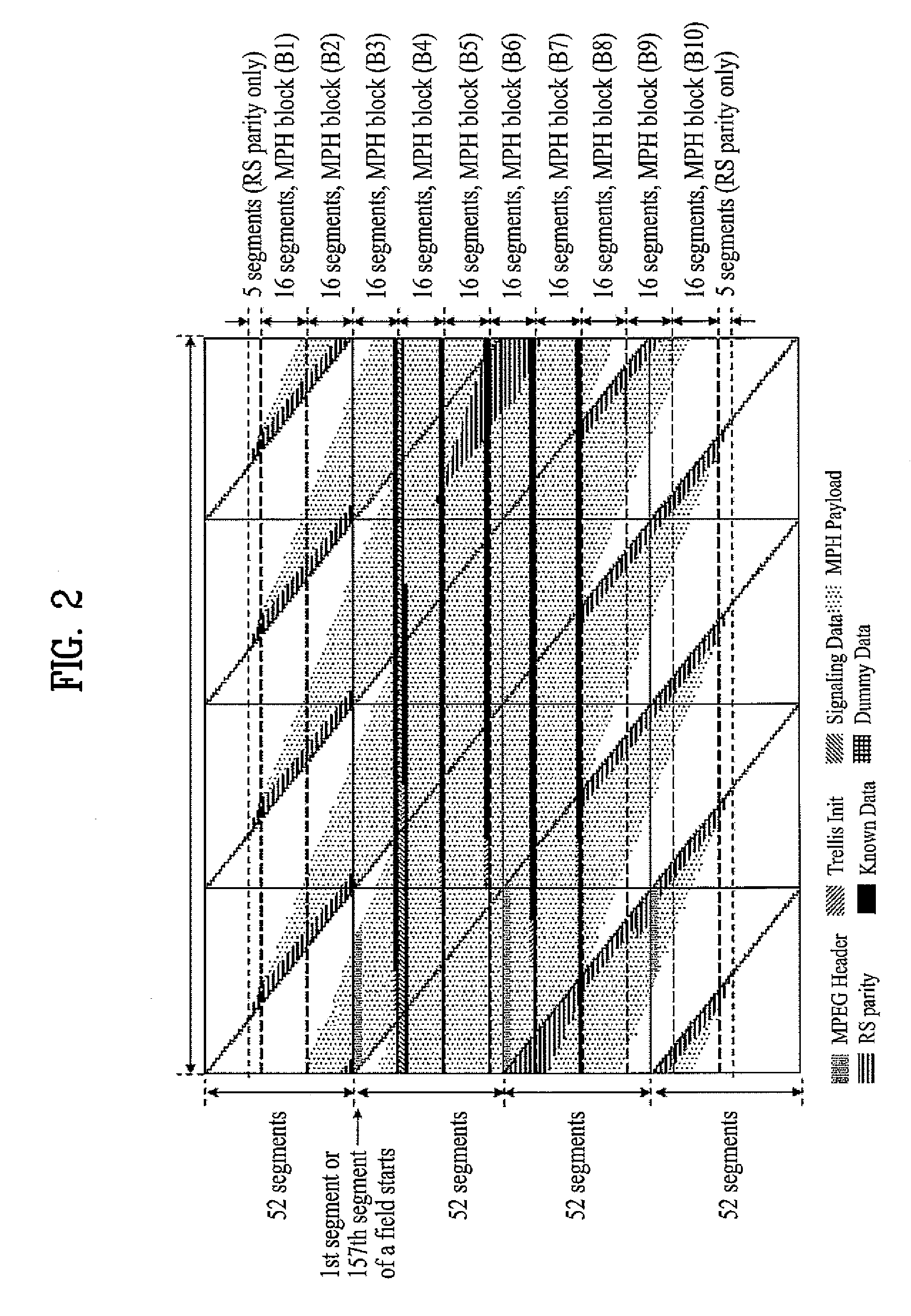

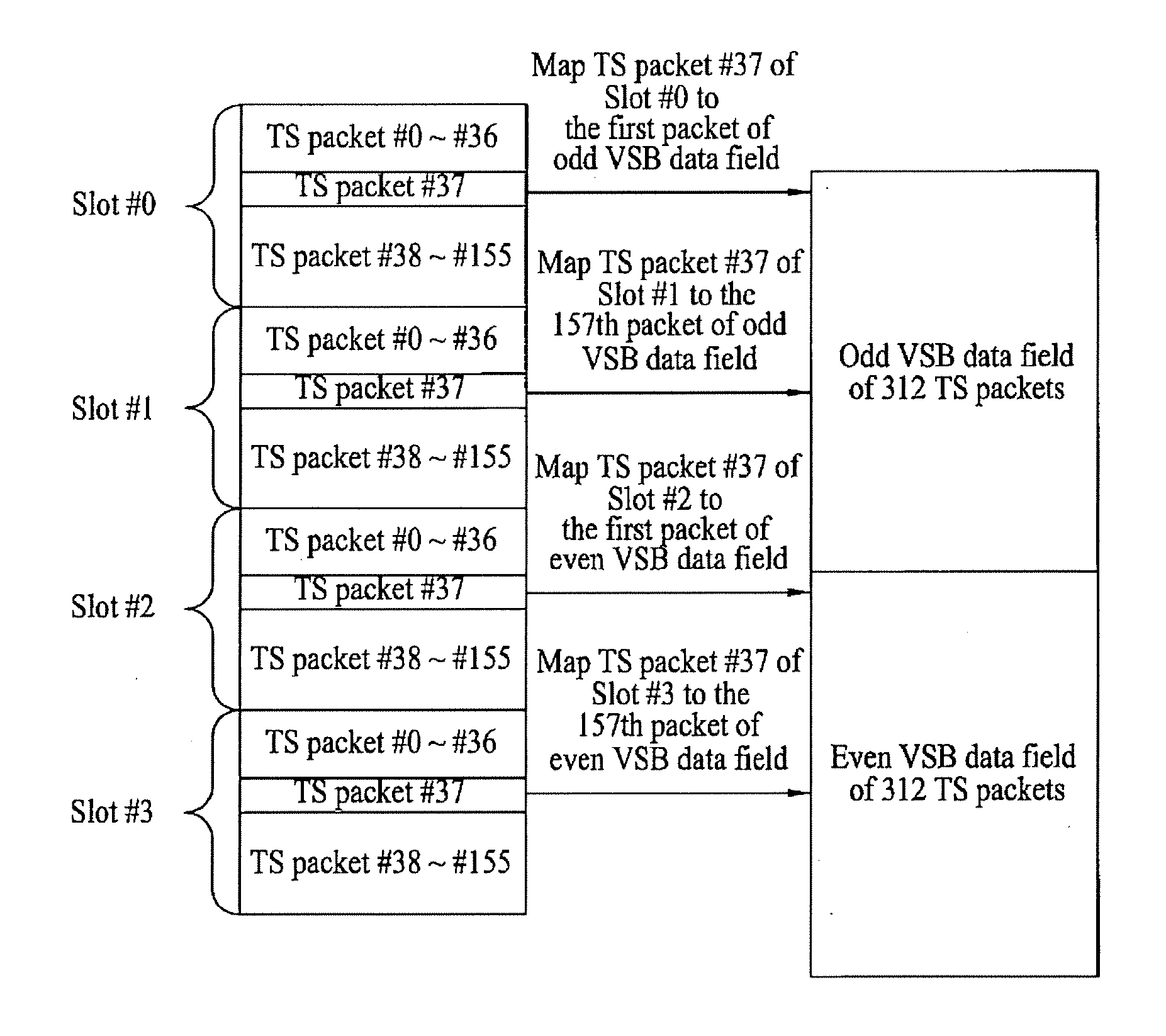

InactiveUS20090052521A1Resistant to channel changeResistant to noiseData representation error detection/correctionModulated-carrier systemsMobile businessDigital broadcasting

A digital broadcasting system and a data processing method are disclosed. The method includes receiving a data processing method includes receiving a broadcast signal in which main service data and mobile service data are multiplexed, acquiring transmission-parameter-channel signaling information including transmission parameter information of the mobile service data, and fast-information-channel signaling information, acquiring binding information describing a relationship between at least one ensemble transferring the mobile service data and a first virtual channel contained in the at least one ensemble by decoding the fast-information-channel, and acquiring status information of the first virtual channel, displaying content data contained in the mobile service data according to the binding information and the status information of the first virtual channel.

Owner:LG ELECTRONICS INC

Digital broadcasting system and method of processing data in digital broadcasting system

InactiveUS8005167B2Resistant to changeResistant to noiseModulated-carrier systemsBroadcast specific applicationsMobile businessInformation gain

The present invention provides a data processing method. The data processing method includes receiving a broadcast signal in which main service data and mobile service data are multiplexed, acquiring transmission-parameter-channel signaling information including transmission parameter information of the mobile service data, and fast-information-channel signaling information, acquiring binding information describing a relationship between at least one ensemble transferring the mobile service data and a first virtual channel contained in any of the at least one ensemble by decoding fast-information-channel signaling information, acquiring ensemble identification information transferring the first virtual channel using the binding information, and receiving at least one mobile service data group transferring an ensemble according to the ensemble identification information, parsing service table information contained in the ensemble and decoding content data contained in the first virtual channel using the parsed service table information, and displaying the decoded content data.

Owner:LG ELECTRONICS INC

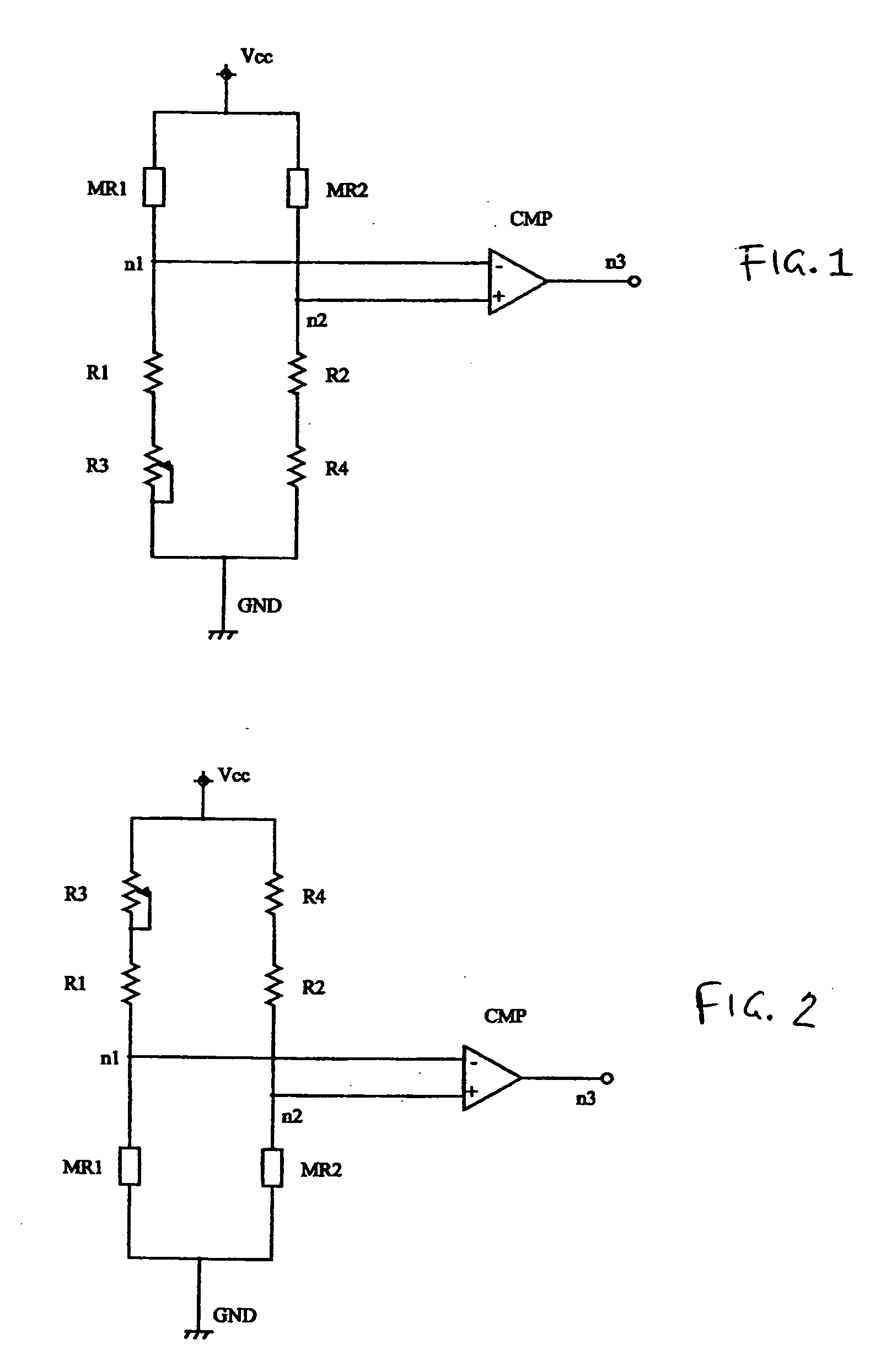

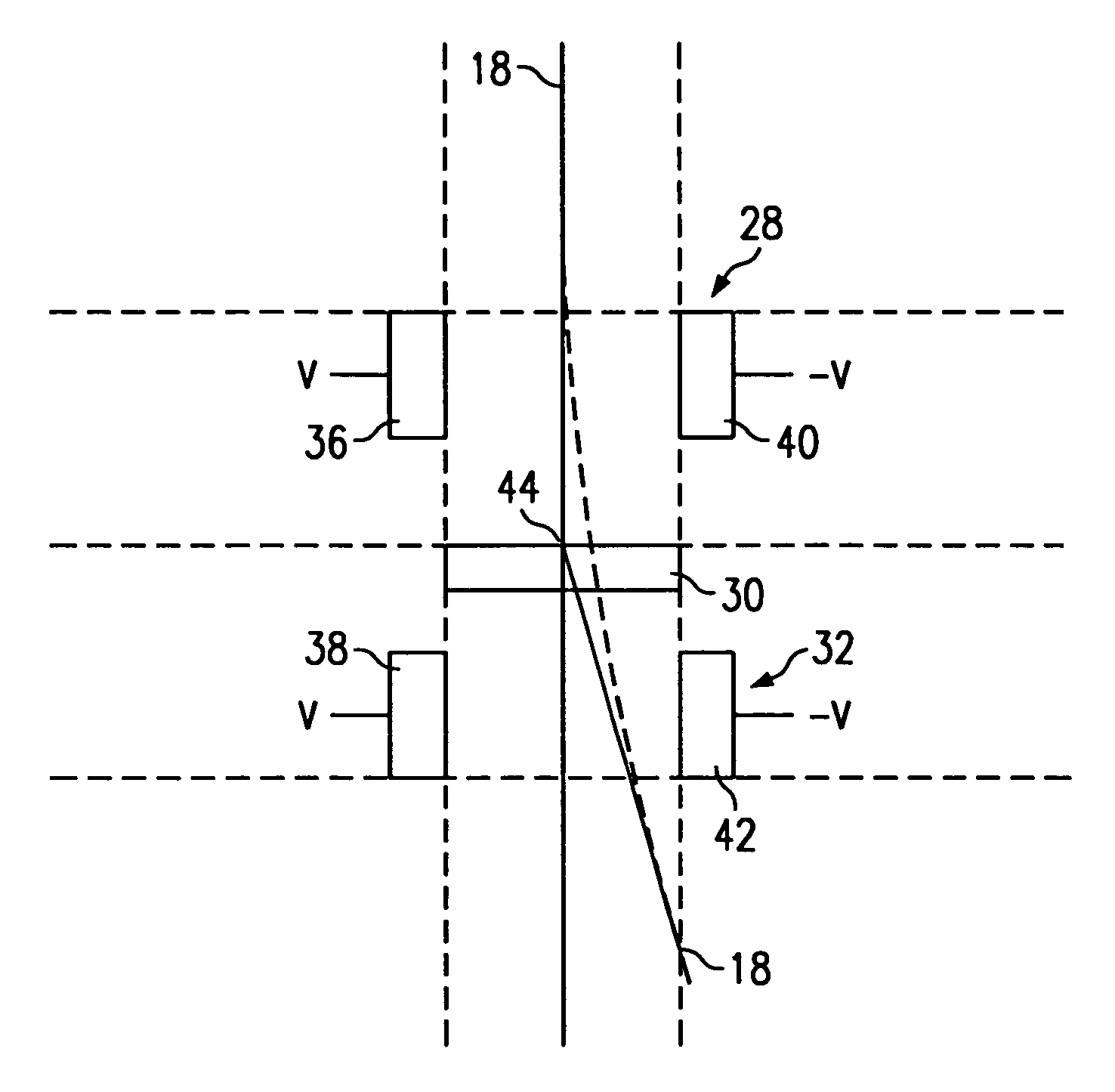

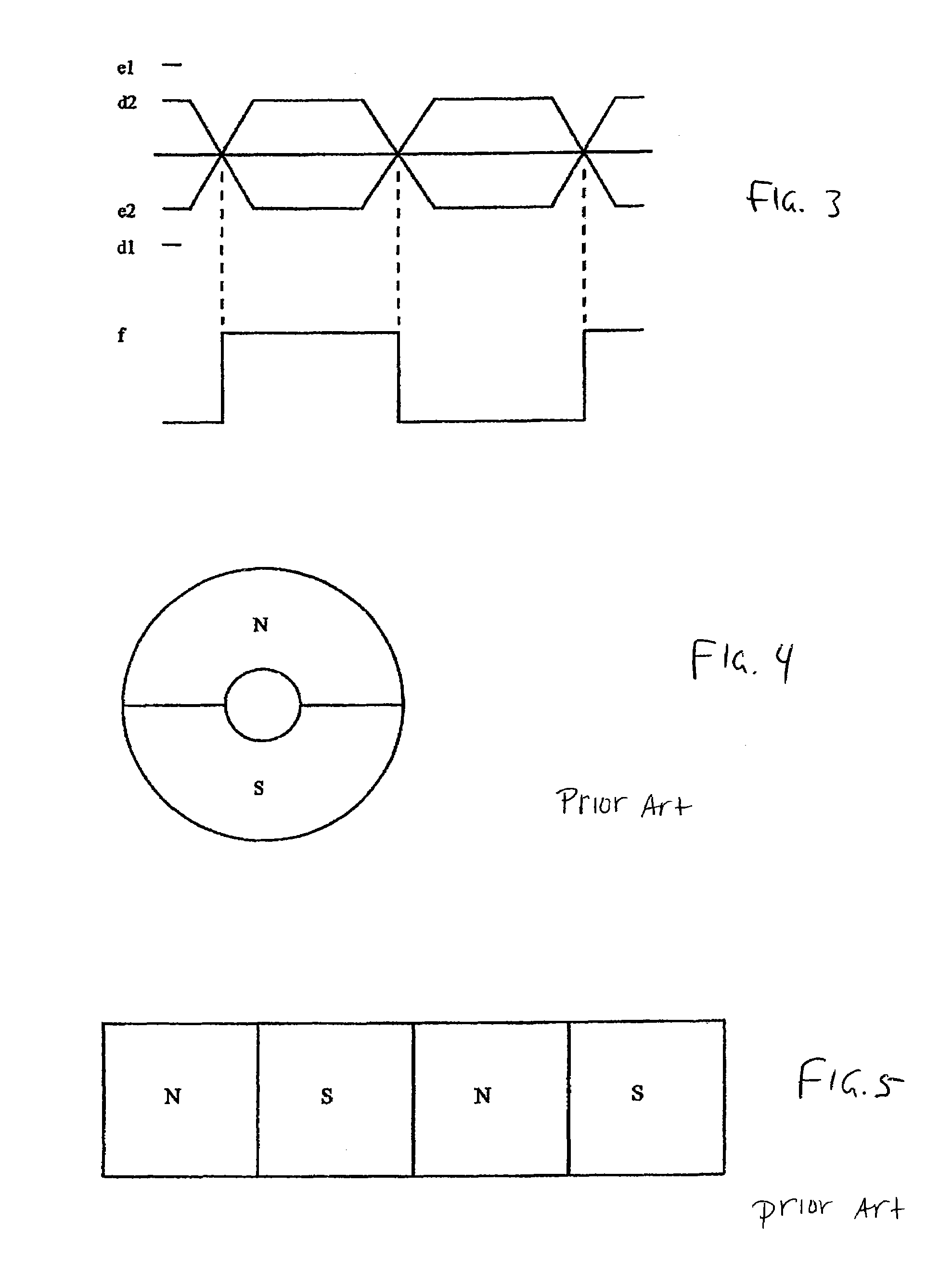

Magnetic detection circuit and encoder

InactiveUS20050200352A1Cost reductionReduce numberNanomagnetismMagnetic-field-controlled resistorsEngineeringBridge circuit

To provide a low-cost magnetic detection circuit, in which the differential detection function accomplished by outputting differential signals may not be lost, and which may be hardly affected by temperature fluctuations and may be resistant to noise, and in which the number of magnetic detection elements may be reduced, and to provide an encoder, the costs of which may be further reduced by using such a magnetic detection circuit for the multi-revolution detection part, etc., a magnetic detection circuit includes a bridge circuit formed by two bridge sections between the current-source terminal and the grounding terminal. The first bridge section and the second bridge section of the bridge circuit include magnetic detection elements MR1, MR2, respectively, and, viewed from the output-signal output points, the magnetic detection elements MR1, MR2 in the two bridge sections are arranged on only one of the sides that include the current-source side and the grounding-terminal side. An encoder includes such a magnetic detection circuit.

Owner:DR JOHANNES HEIDENHAIN GMBH

Sports bottle with preloaded valve and methods

InactiveUS8561851B1Particular resistanceResistant to leakageCheck valvesEqualizing valvesEngineeringWater bottle

A beverage bottle for storing and dispensing water and impure sports beverages having a container and a dispensing opening on a top wall movable between an open position and a closed position and a unitary valve disposed within the container bottom wall having a vertically sinuous contour, and laterally opposed, laterally actuating, compliant slit faces and a substantially rigid annular flat surface. As the vertically sinuous contour is flattened upon the annular flat surface, the slit faces are laterally urged together establishing a preloaded seal, for leak resistant valve operation, and reduced restriction dispensing of water and impure sports beverages.

Owner:LEONOFF CHRISTOPHER A

Digital broadcasting system and method of processing data in digital broadcasting system

InactiveUS20090129504A1Resistant to changeResistant to noiseModulated-carrier systemsBroadcast specific applicationsMobile businessInformation gain

The present invention provides a data processing method. The data processing method includes receiving a broadcast signal in which main service data and mobile service data are multiplexed, acquiring transmission-parameter-channel signaling information including transmission parameter information of the mobile service data, and fast-information-channel signaling information, acquiring binding information describing a relationship between at least one ensemble transferring the mobile service data and a first virtual channel contained in any of the at least one ensemble by decoding fast-information-channel signaling information, acquiring ensemble identification information transferring the first virtual channel using the binding information, and receiving at least one mobile service data group transferring an ensemble according to the ensemble identification information, parsing service table information contained in the ensemble and decoding content data contained in the first virtual channel using the parsed service table information, and displaying the decoded content data.

Owner:LG ELECTRONICS INC

Digital broadcasting system and method of processing data in digital broadcasting system

InactiveUS20090051811A1Resistant to channel changeResistant to noiseTelevision system detailsPicture reproducers using cathode ray tubesMobile businessDigital broadcasting

A digital broadcasting system and a data processing method are disclosed. The method includes, receiving a broadcast signal in which mobile service data and main service data are multiplexed, extracting transmission parameter signaling information and fast-information-channel signaling information from a data group contained in the received mobile service data, parsing first program table information, which describes virtual channel information and a service of an ensemble acting as a virtual channel group of the received mobile service data, using the fast-information-channel signaling information, parsing second program table information including a data chunk acting as data-broadcasting contents of the mobile service data, and providing a data broadcasting service using the data broadcasting contents of the parsed second program table information.

Owner:LG ELECTRONICS INC

Method and system for calibrating the scan amplitude of an electron beam lithography instrument

InactiveUS6941006B1Effective positioningControlling signalElectric discharge tubesNanoinformaticsLight beamElectron-beam lithography

A method for calibrating the scan amplitude of an electron beam lithography instrument by determining the position of a feature within the scan. The method is effective at the operating frequency of the scan and using a limited bandwidth video signal including the steps of determining the reference feature to be an edge over which the video signal rises abruptly from a background level to a white level. The method turns the beam on only over a short region of the scan and represents the degree of overlap between the beam on portion of the scan and the white part of the feature as the total video signal accumulated in that scan.

Owner:DUPONT PHOTOMASKS

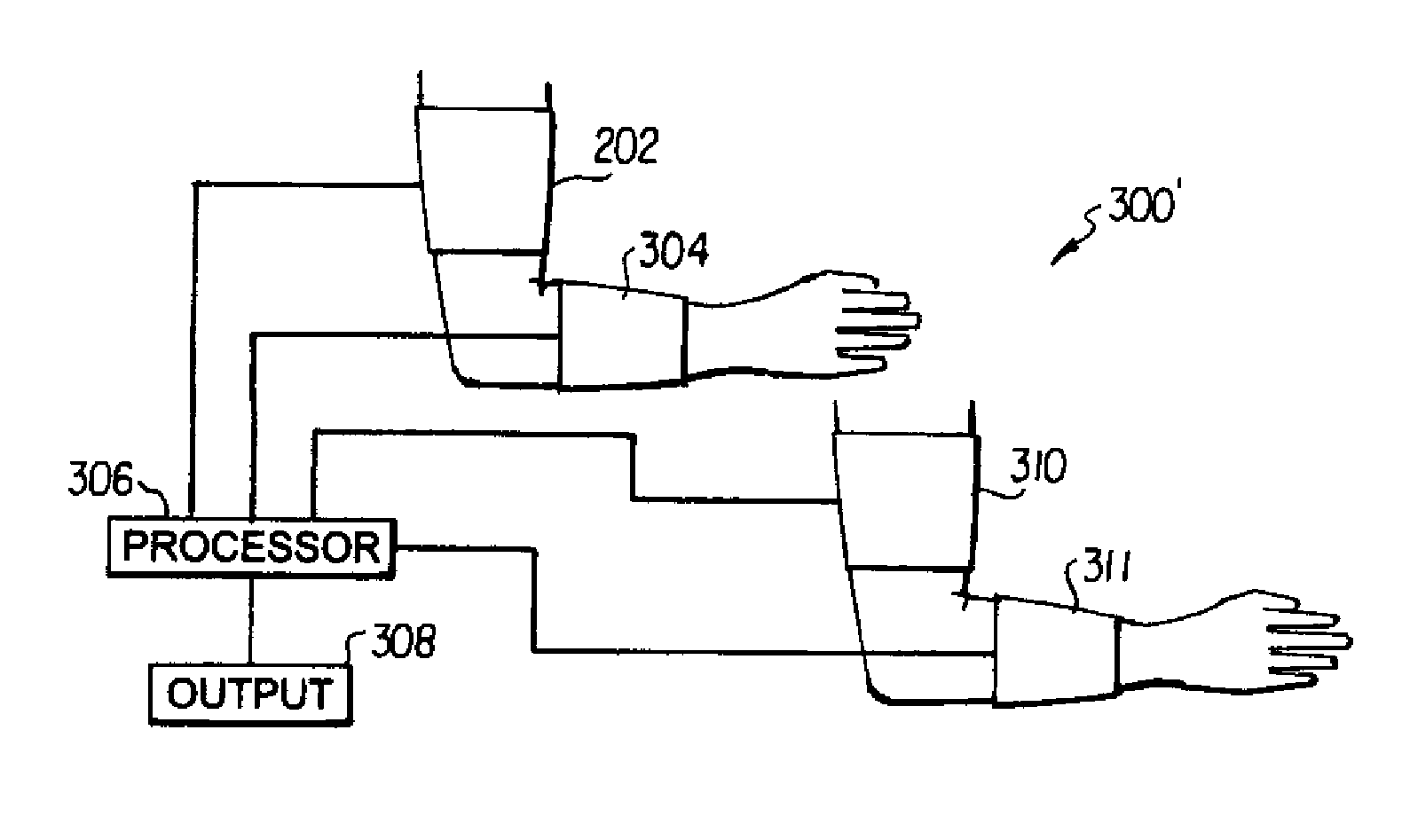

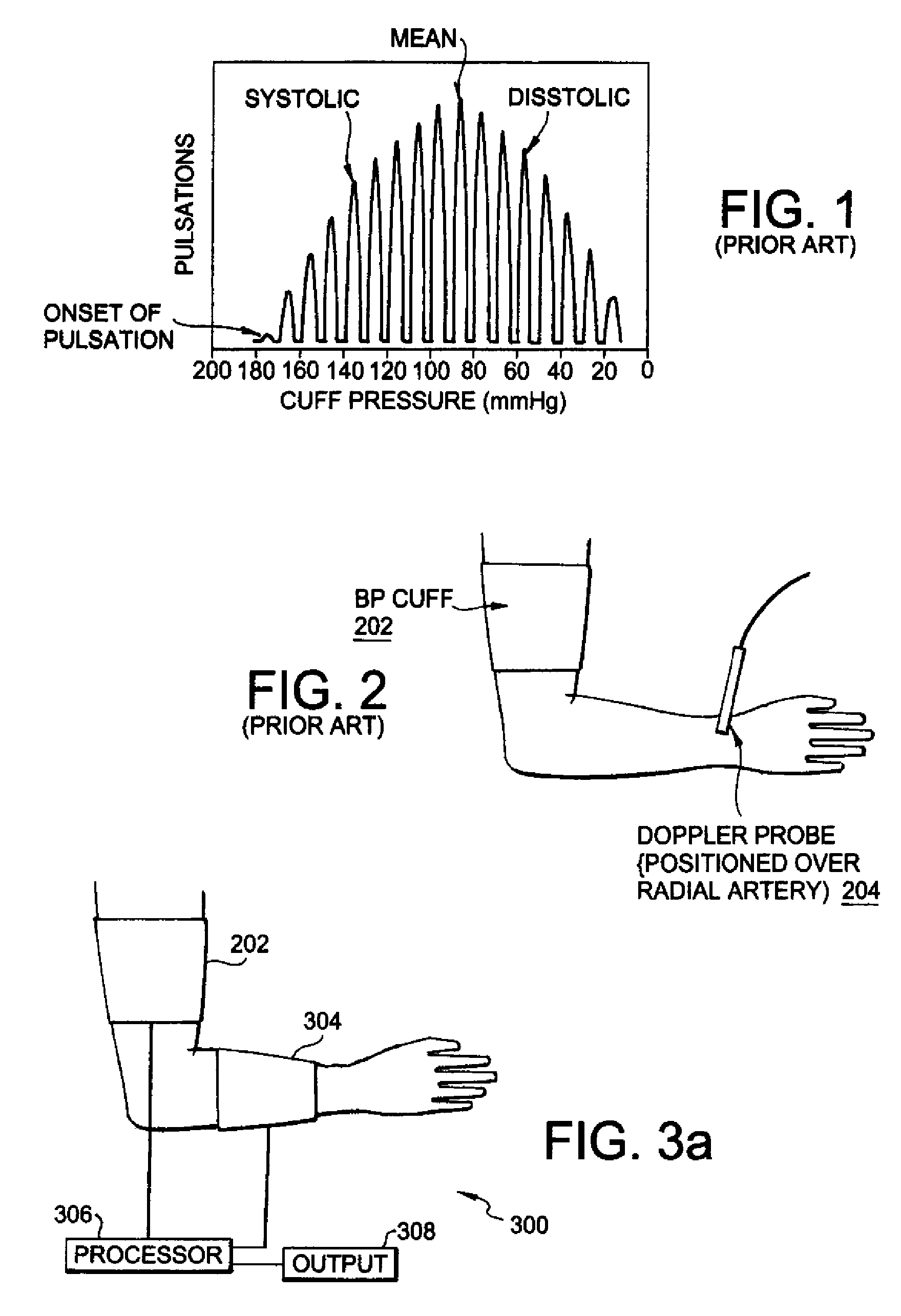

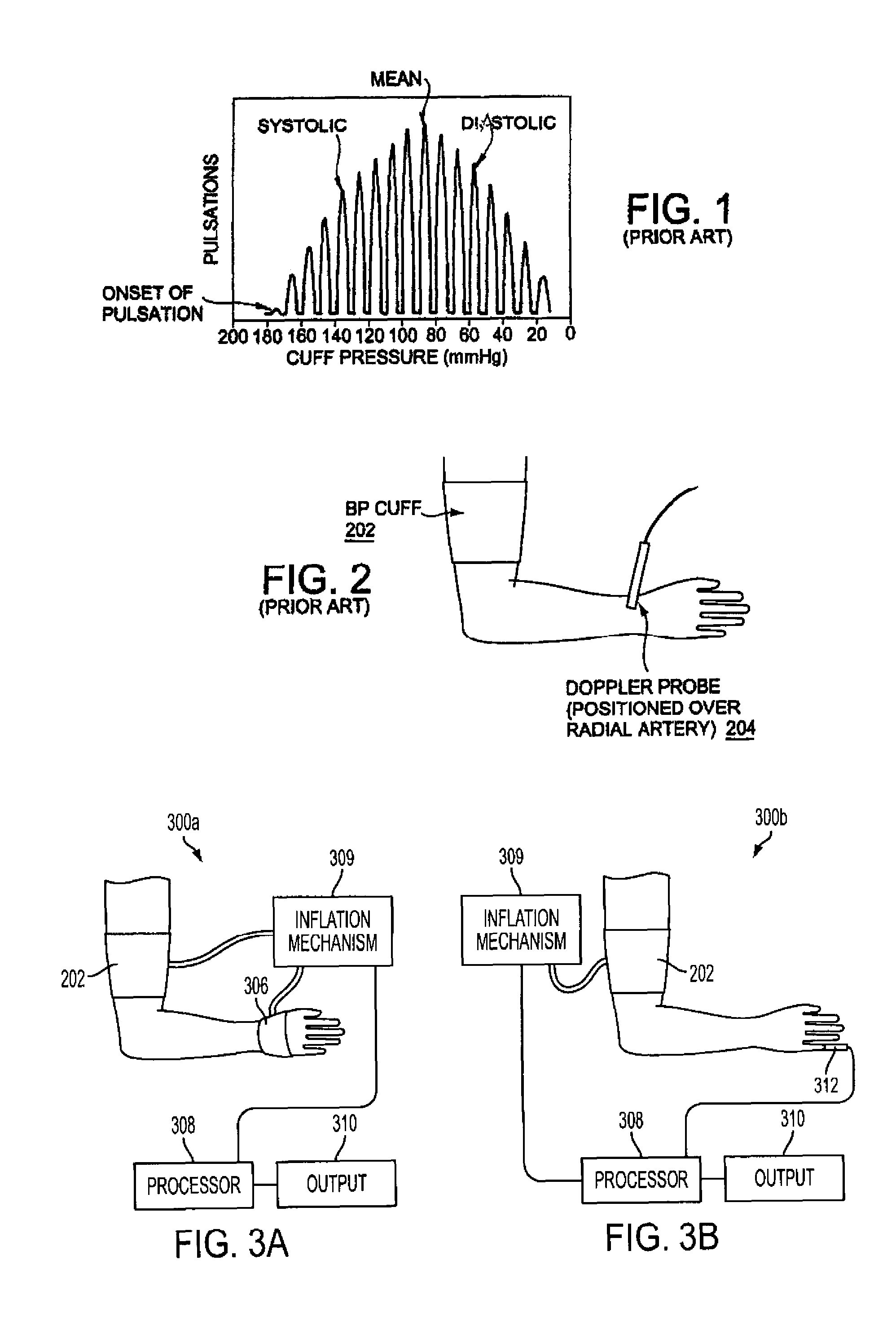

Impedance based device for non-invasive measurement of blood pressure and ankle-brachial index

ActiveUS7887491B2Accurate pressurePerformed easily and reliablyEvaluation of blood vesselsCatheterBlood pressure cuffsBlood pressure cuff

A device for non-invasive measurement of blood pressure includes a blood pressure cuff, a plethysmographic electrode for acquiring an impedance plethysmogram distal to the cuff and a processing device to inflate and deflate the cuff generate the impedance plethysmogram and to determine the systolic and diastolic blood pressures. The device can be used to measure systolic or diastolic blood pressure or both. It can also be used to take ankle-brachial measurements. An autocorrelation technique can be used to correct noise.

Owner:SMITHMARKS INC

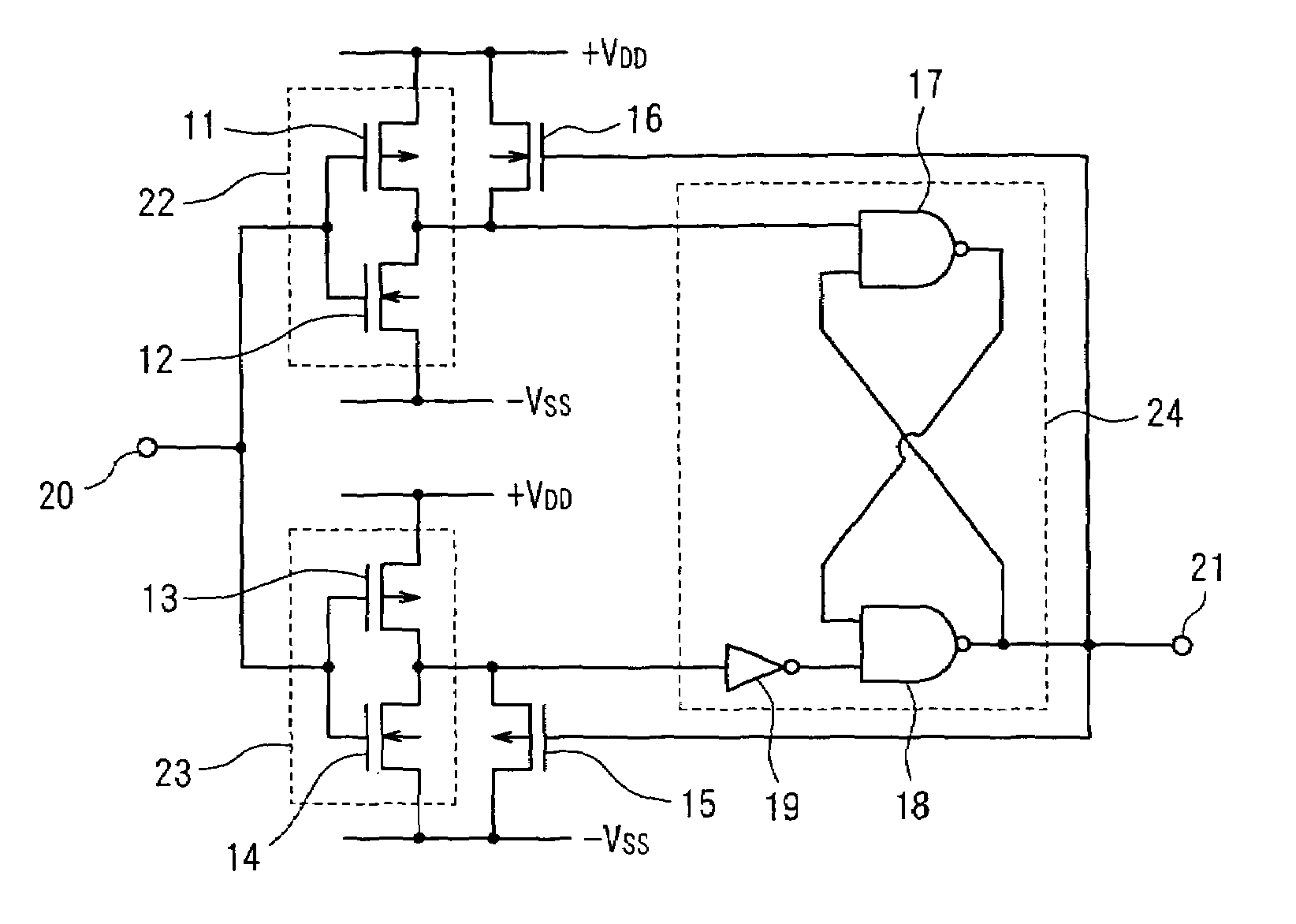

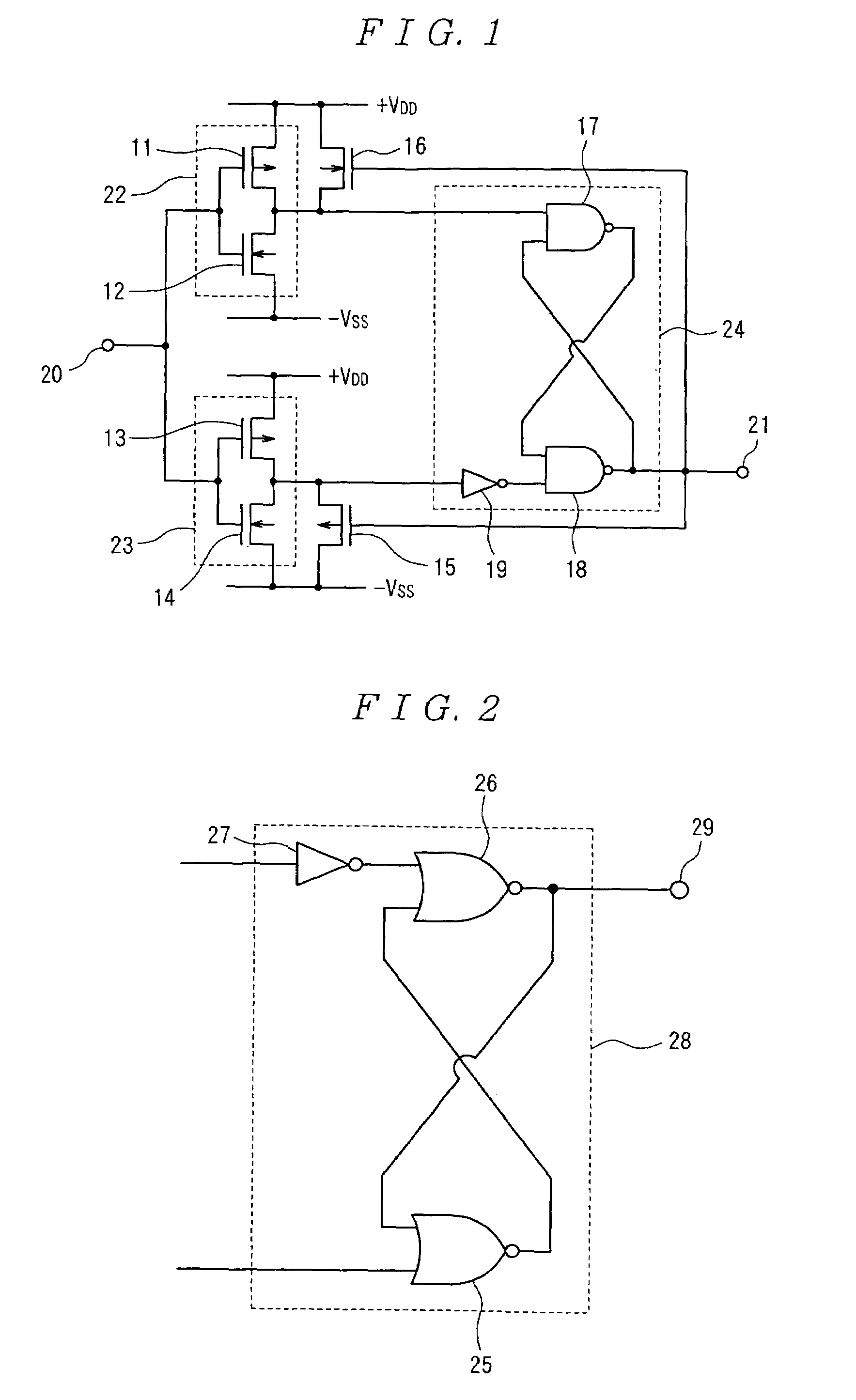

High hysteresis width input circuit

The present invention is constructed of a first input circuit having a higher logic level VIH made up of a first inverter circuit 22 controlled by an input signal and an N-type MOSFET 16 controlled by a latch circuit 24 which stores a preceding state, a second input circuit having a lower logic level VIL made up of a second inverter circuit 23 controlled by an input signal and a P-type MOSFET 15 controlled by a latch circuit which stores a preceding state and the latch circuit 24 which stores a preceding state.

Owner:SEIKO EPSON CORP

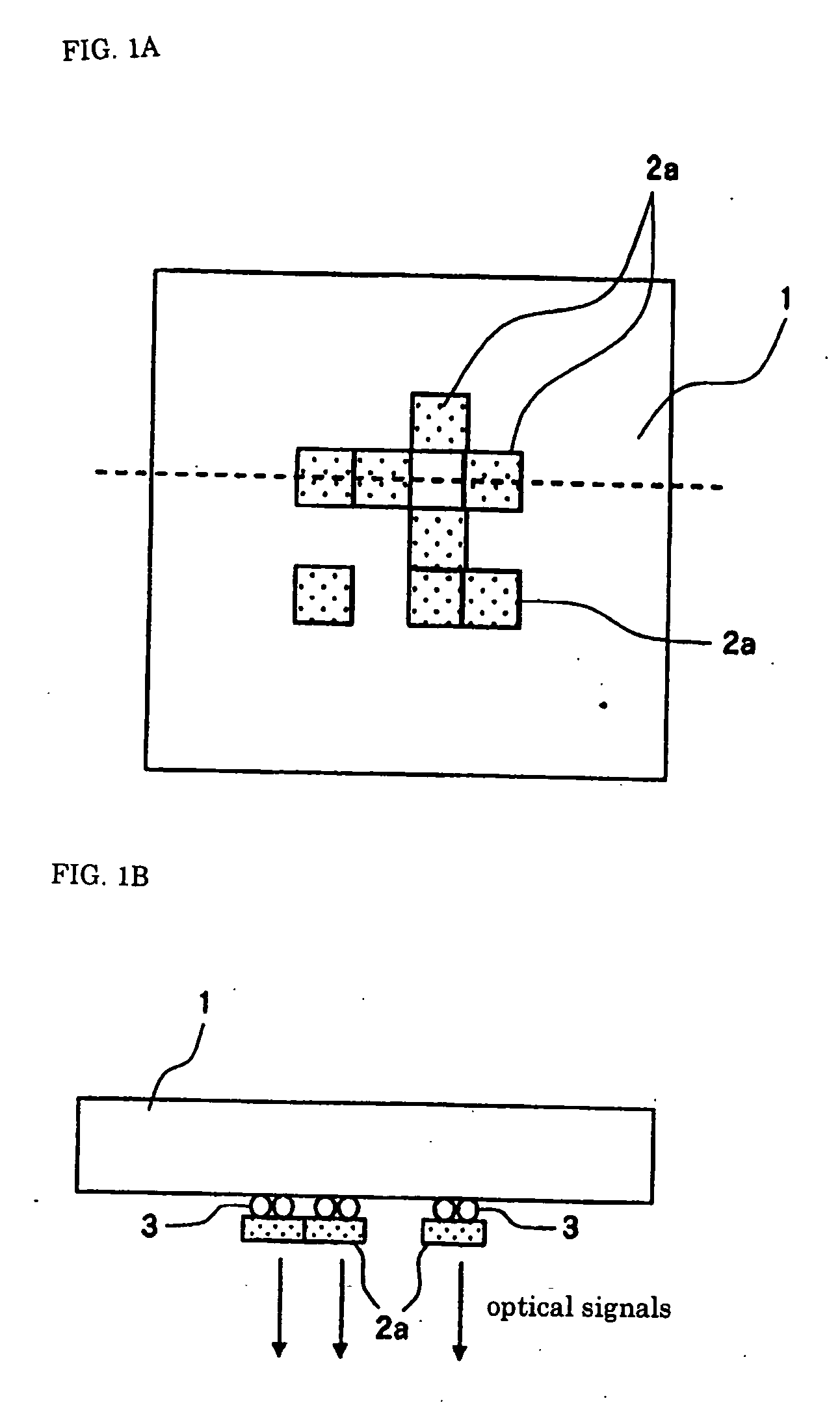

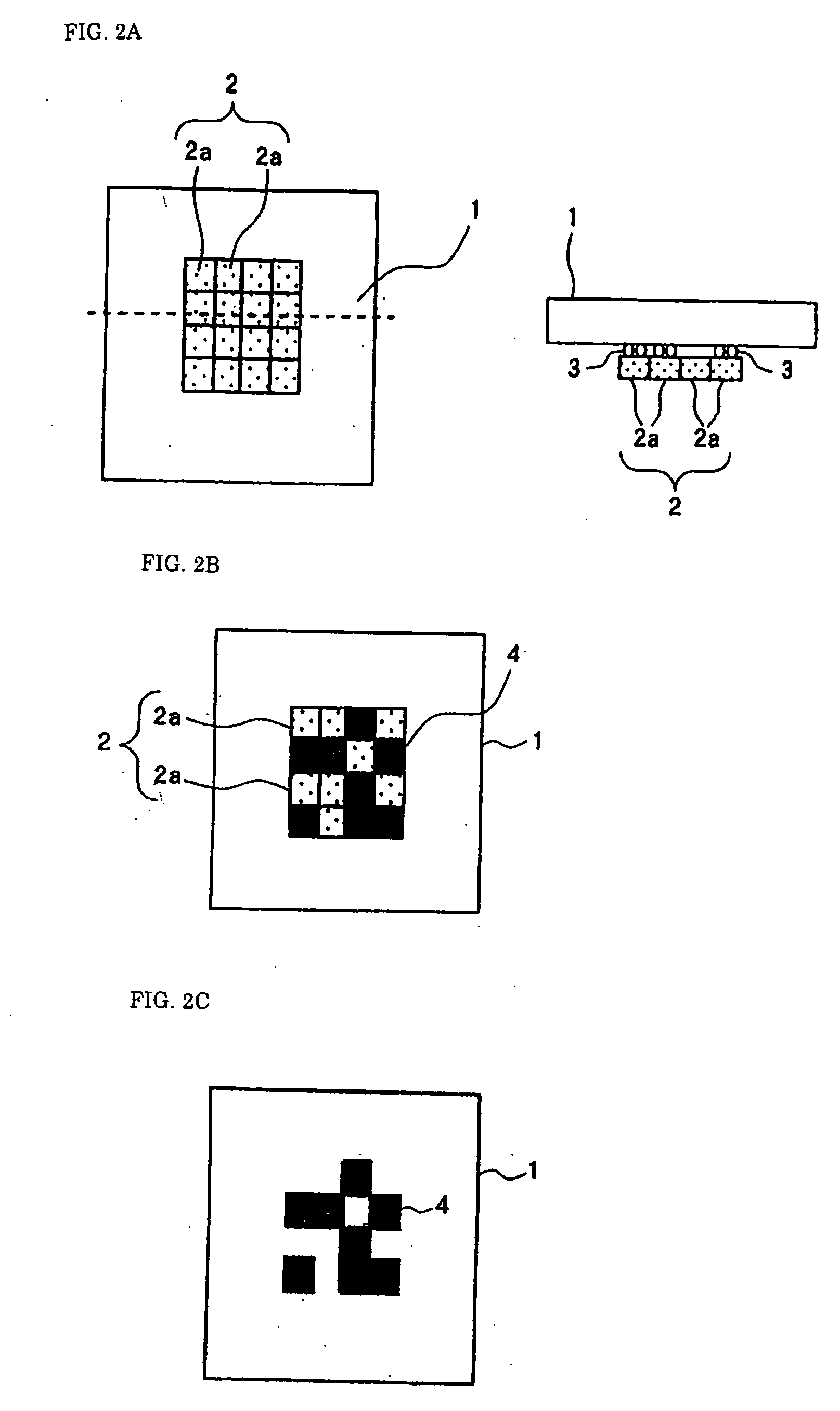

Optical-element integrated semiconductor integrated circuit and fabrication method thereof

InactiveUS20070164297A1Resistant to noiseEfficiently coupleSolid-state devicesSemiconductor devicesIntegrated circuitEngineering

Light-emitting device array 2 is mounted on LSI 1, following which necessary light-emitting devices 2a among two or more light-emitting devices 2 that make up mounted light-emitting device array 2 are allowed to remain and unnecessary light-emitting devices 2a are removed in order to mount light-emitting devices on a plurality of output ports that are randomly arranged on LSI 1.

Owner:NEC CORP

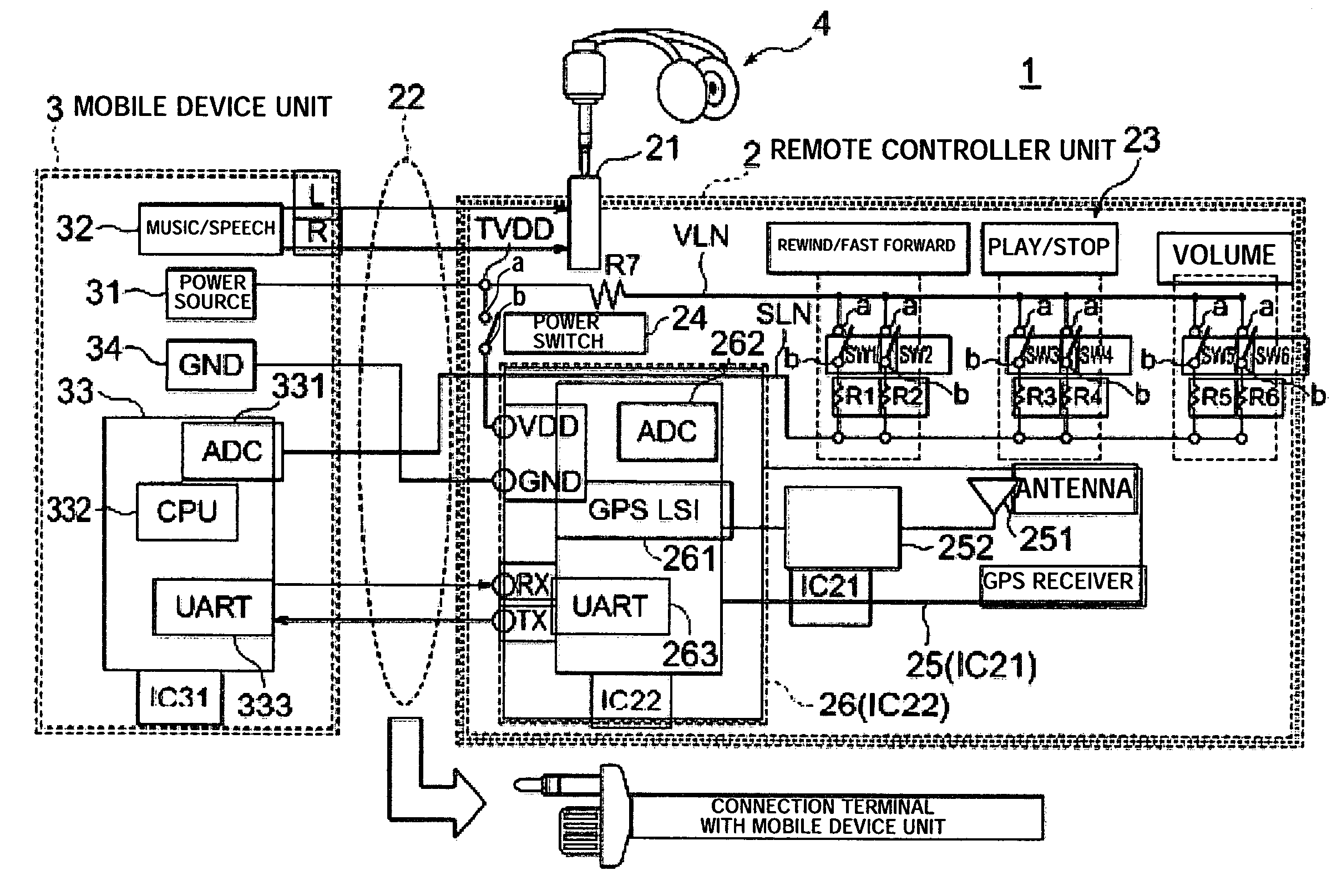

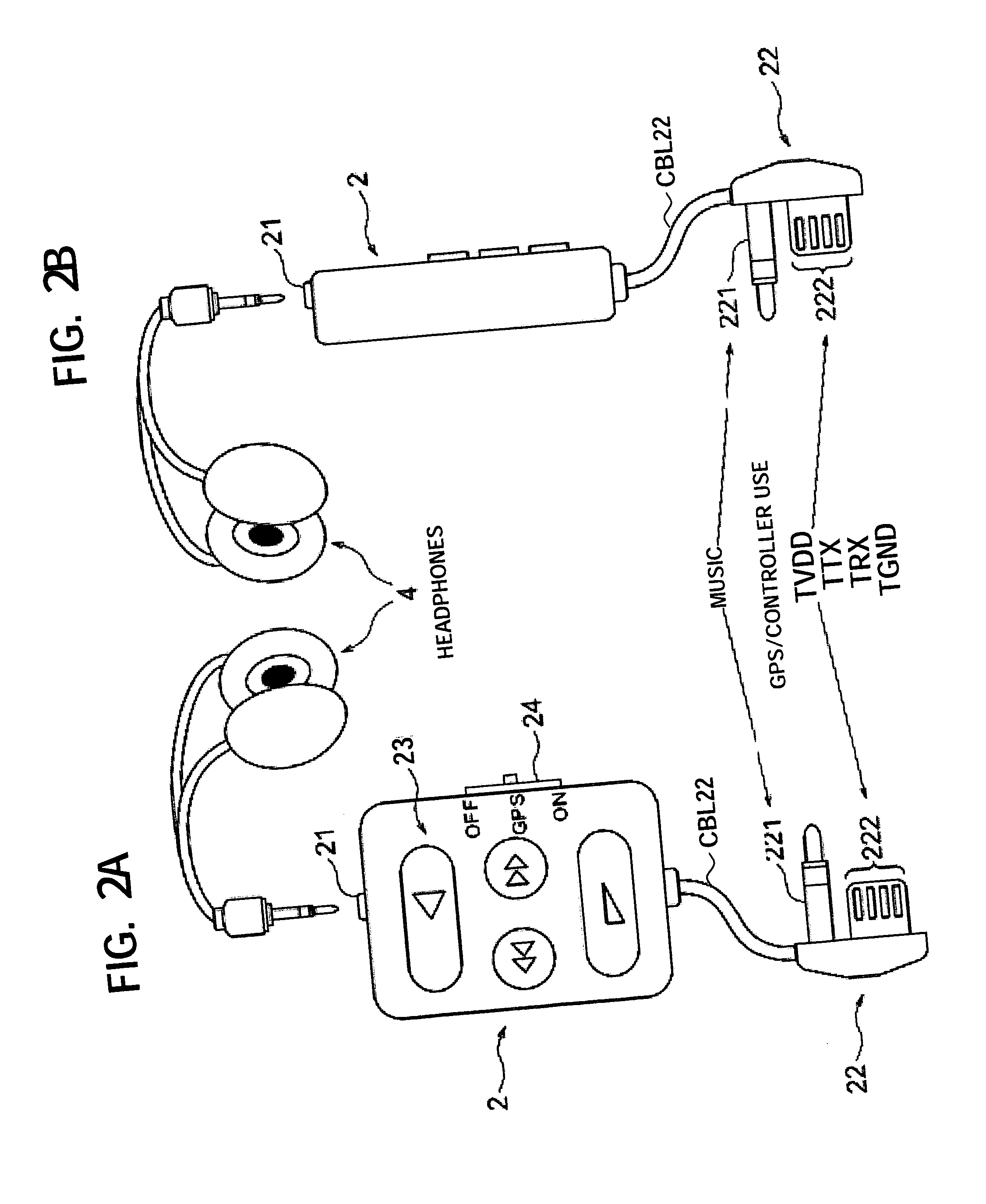

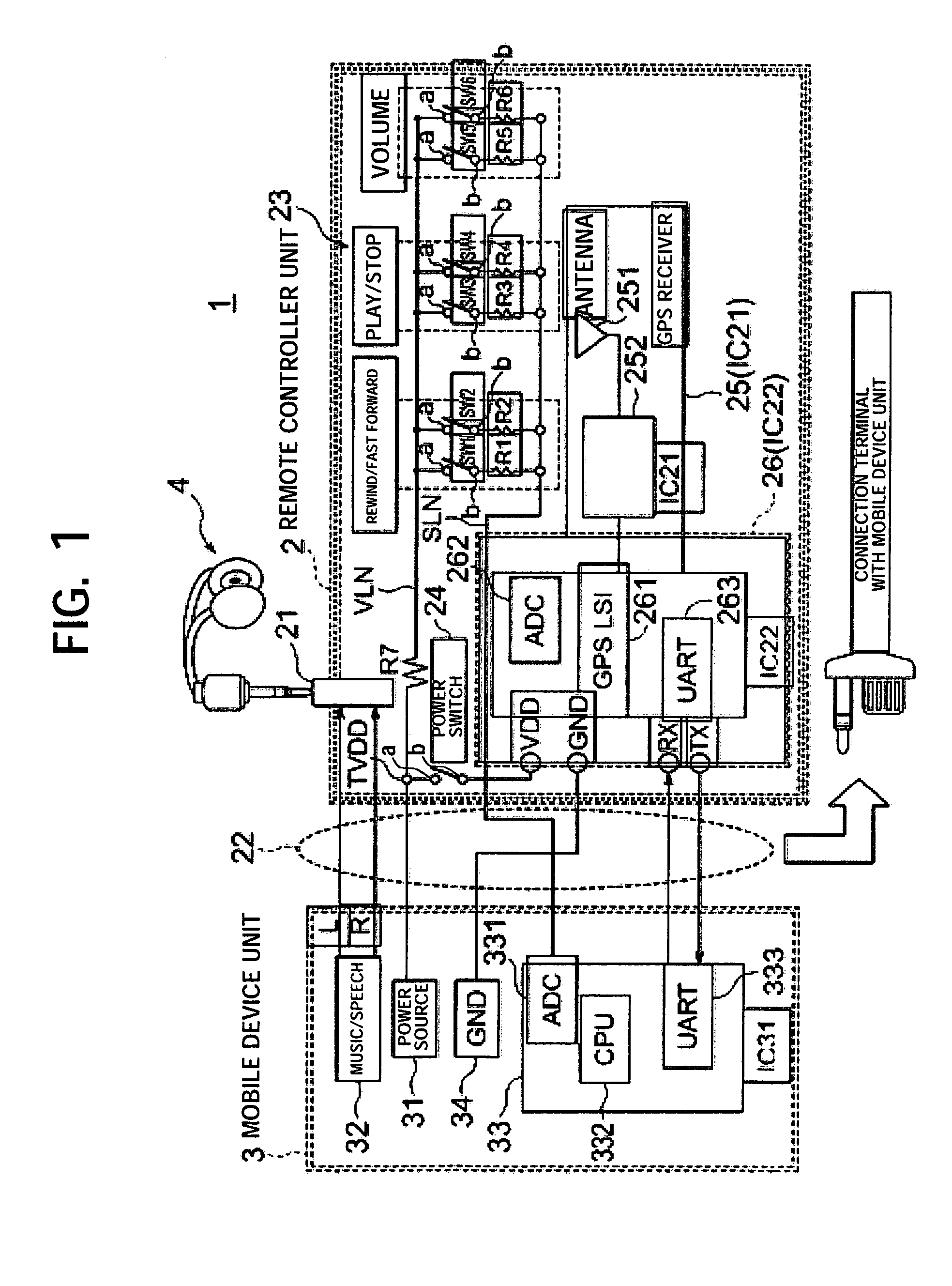

Mobile device

ActiveUS20050242988A1Firmly connectedLittle susceptibility to noisePower managementSubstation speech amplifiersGps receiverEngineering

A mobile device is provided. The mobile device provides simple connection with a mobile device unit, resistant to noise from the mobile device unit, and enabling a GPS function to be fully exhibited, wherein a first integrated circuit IC21 mounting a GPS receiver and GPS antenna and a second integrated circuit IC22 mounting a controller control circuit are housed in a controller unit, the controller unit is provided with a headphone jack and a music / speech terminal-GPS terminal to be connected to the mobile device, and the terminal is inserted into the mobile device unit to supply power source voltage from the mobile device unit side and enable the controller and GPS function to be used.

Owner:SONY CORP

Mobile device

ActiveUS7151488B2Firmly connectedLittle susceptibility to noisePower managementSubstation speech amplifiersGps receiverComputer terminal

A mobile device is provided. The mobile device provides simple connection with a mobile device unit, resistant to noise from the mobile device unit, and enabling a GPS function to be fully exhibited, wherein a first integrated circuit IC21 mounting a GPS receiver and GPS antenna and a second integrated circuit IC22 mounting a controller control circuit are housed in a controller unit, the controller unit is provided with a headphone jack and a music / speech terminal-GPS terminal to be connected to the mobile device unit, and the terminal is inserted into the mobile device unit to supply power source voltage from the mobile device unit side and enable the controller and GPS function to be used.

Owner:SONY CORP

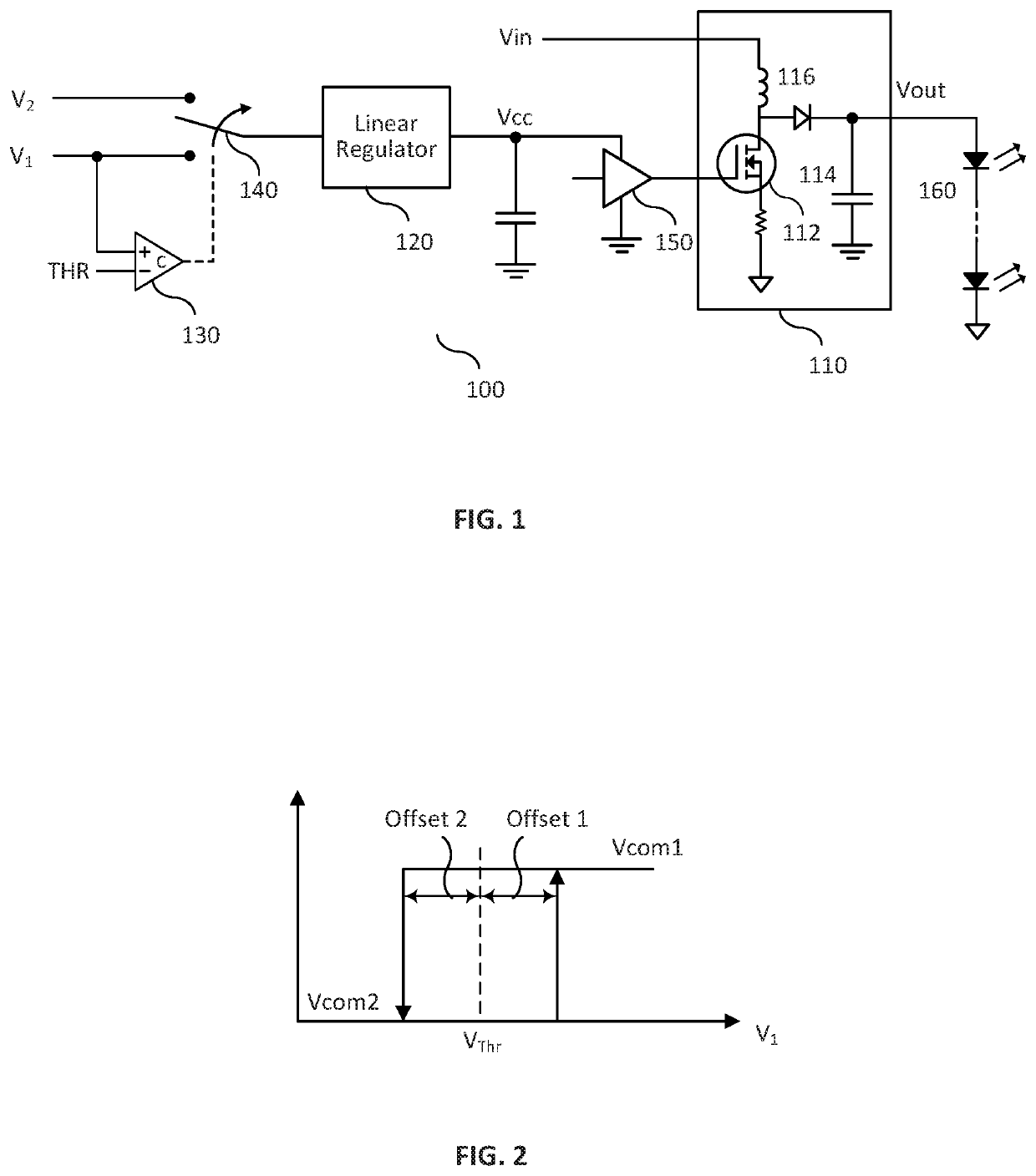

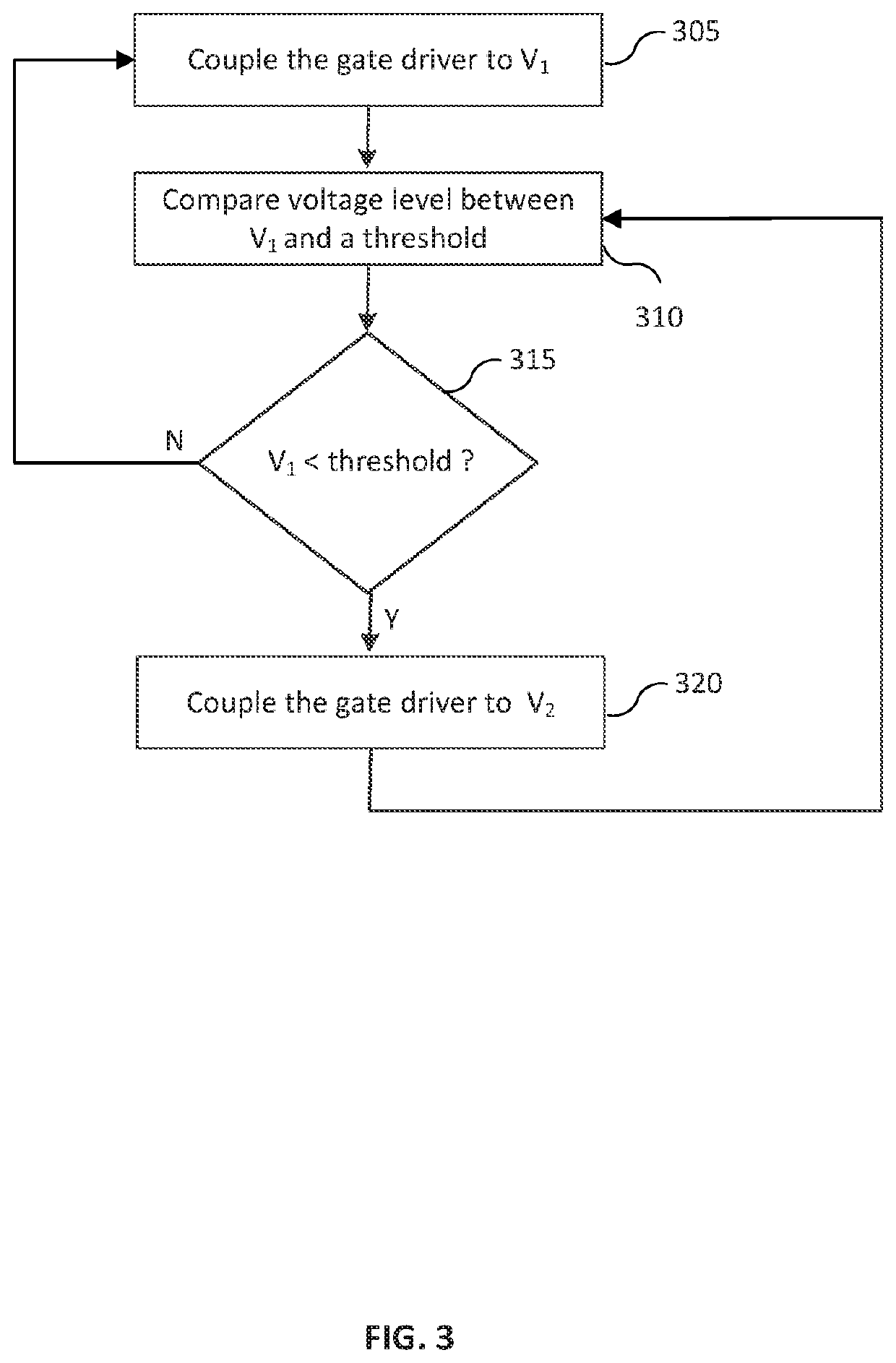

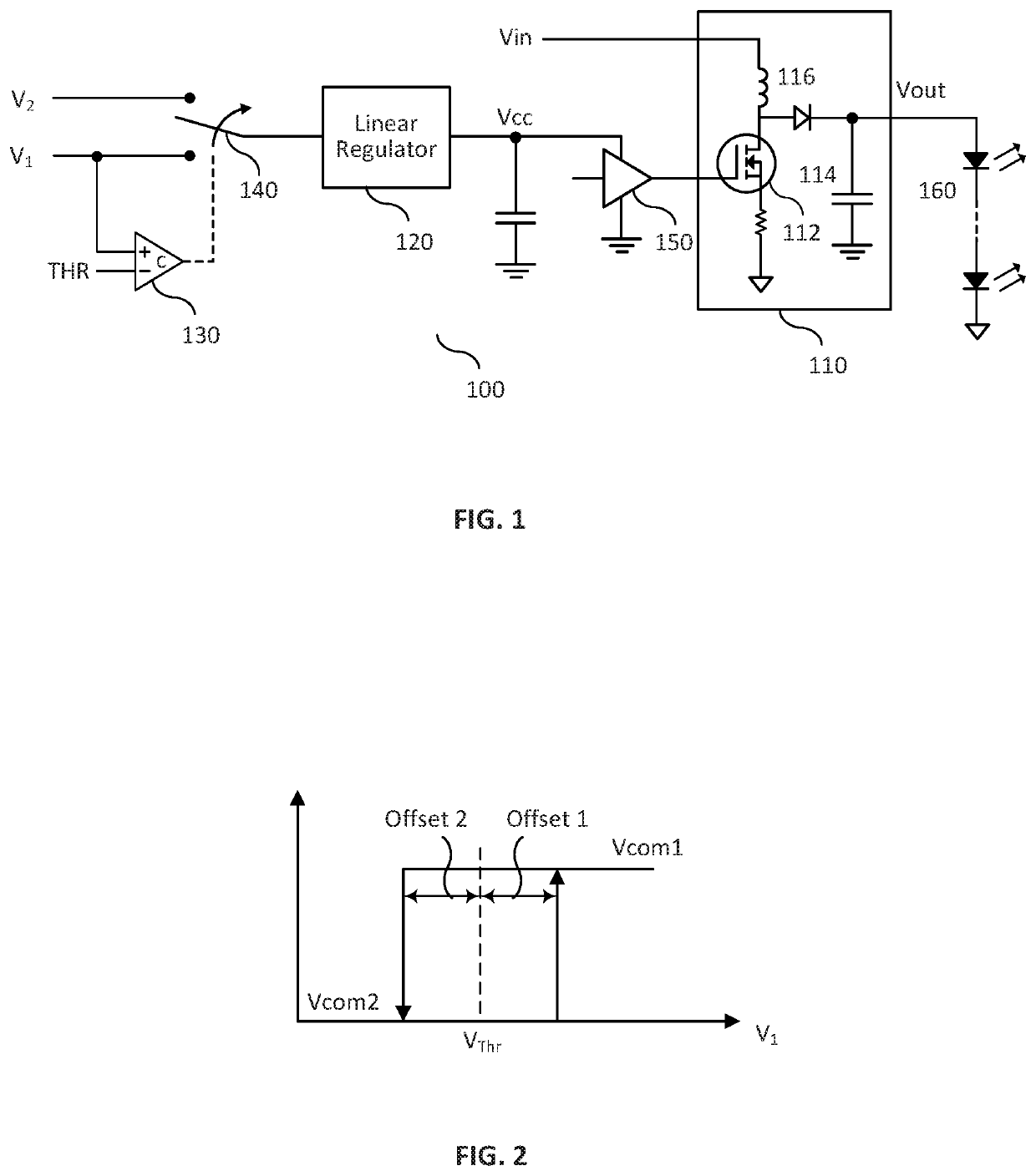

LED driver with ability to operate at arbitrarily low input voltages

ActiveUS20200084846A1Improve performanceImprove comprehensive applicabilityElectric circuit arrangementsElectroluminescent light sourcesMOSFETLinear regulator

An LED driver with ability to operate at low input voltages is disclosed. The LED driver comprises a boost converter to boost an input voltage to a desired output voltage to power one or more LED strings. The boost converter incorporates a first controllable switch, such as a metal-oxide-semiconductor field-effect transistor (MOSFET), IGBT, etc., for output voltage control. The boost converter receives input from an external source, such as a battery voltage, as power source for voltage boost operation. The first controllable switch couples to a gate driver powered by a linear regulator, which switchably couples to different voltage sources via a second switch to ensure that the gate driver is able to provide enough voltage for switching the first controllable switch.

Owner:MAXIM INTEGRATED PROD INC

Digital broadcasting system and method of processing data in digital broadcasting system

InactiveUS7889695B2Resistant to changeResistant to noiseData representation error detection/correctionModulated-carrier systemsMobile businessDigital audio broadcasting

A digital broadcasting system and a data processing method are disclosed. The method includes receiving a data processing method includes receiving a broadcast signal in which main service data and mobile service data are multiplexed, acquiring transmission-parameter-channel signaling information including transmission parameter information of the mobile service data, and fast-information-channel signaling information, acquiring binding information describing a relationship between at least one ensemble transferring the mobile service data and a first virtual channel contained in the at least one ensemble by decoding the fast-information-channel, and acquiring status information of the first virtual channel, displaying content data contained in the mobile service data according to the binding information and the status information of the first virtual channel.

Owner:LG ELECTRONICS INC

Digital broadcasting system and method of processing data in digital broadcasting system

InactiveUS8776143B2Resistant to changeResistant to noiseTelevision system detailsPulse modulation television signal transmissionMobile businessDigital broadcasting

The present invention provides a data processing method, the data processing method including receiving a broadcasting signal where mobile service data are multiplexed with main service data, extracting transmission-parameter-channel signaling information and fast-information-channel signaling information from a data group within the received mobile service data, parsing first program table information describing virtual channel information of an ensemble and a service provided by the ensemble using the fast-information-channel signaling information, the ensemble corresponding to a virtual channel group of the received mobile service data, obtaining information representing that second program table information, which includes a descriptor describing event information of the mobile service data, is received, from the first program table information, parsing the second program table information, and storing the event information and displaying service guide information including the event information.

Owner:LG ELECTRONICS INC

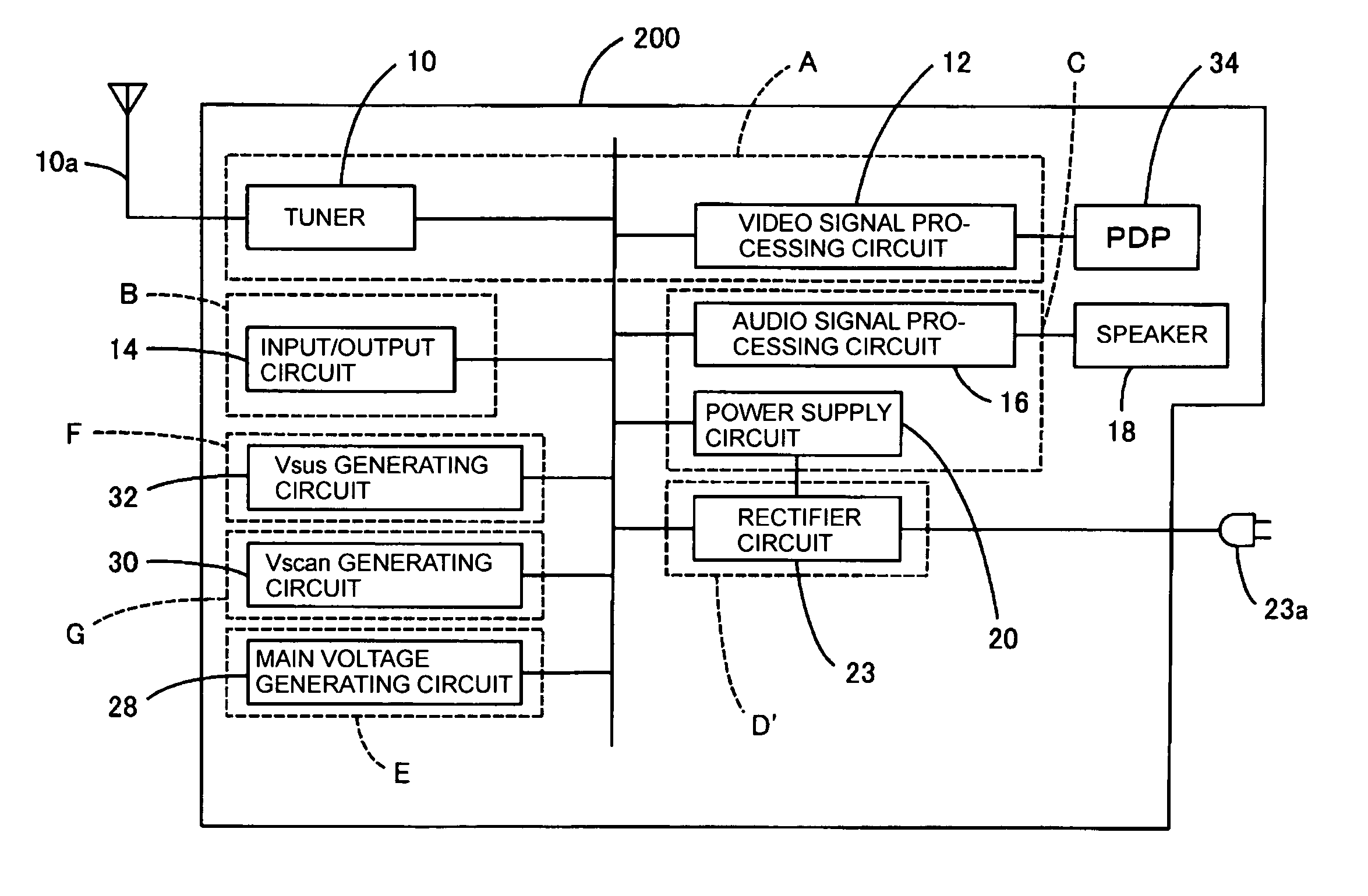

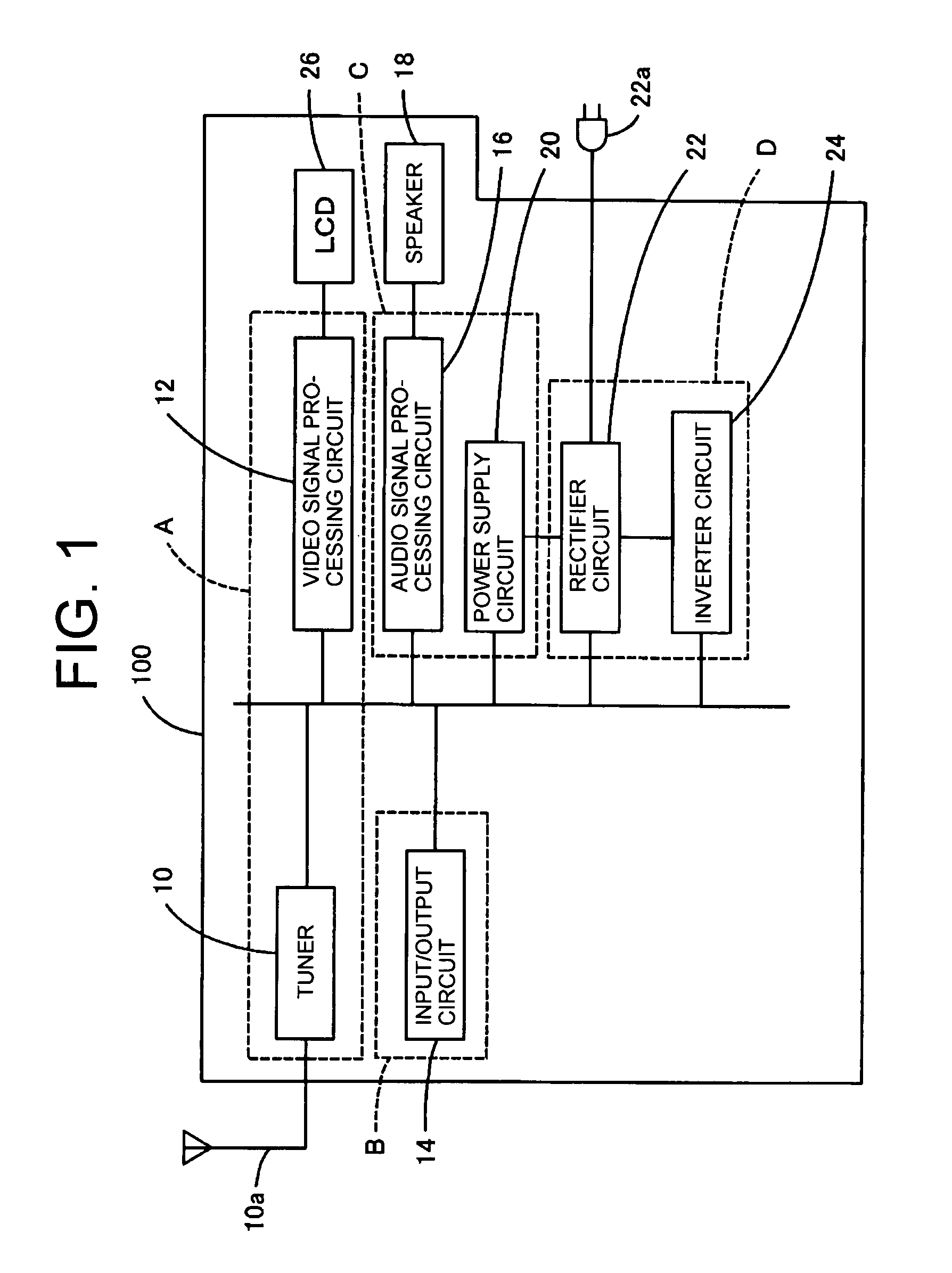

Liquid crystal panel, plasma display panel, and wide-screen liquid crystal television

InactiveUS8339522B2Work lessReduce deliveryTelevision system detailsTelevision system scanning detailsSignal processing circuitsLiquid crystal

There is provided a liquid crystal television and a plasma television that can adapt to various destinations and are resistant to noise in view of the difference of circuit configurations between a liquid crystal television and a plasma television. A video signal processing circuit is formed on a digital board, an input and output circuit is formed on a jack board, an audio signal processing circuit and a power supply circuit are formed on an analog board, and a rectifier circuit and an inverter circuit are formed on an inverter board. Further, on the back of the LCD, the inverter board is disposed in a vertically oriented shape in the left, the analog board is disposed in the lower center, the digital board is disposed in the upper center adjacent to the analog board, and the jack board is disposed in the upper right.

Owner:FUNAI ELECTRIC CO LTD

Digital broadcasting system and method of processing data in digital broadcasting system

ActiveUS20120099581A1Resistant to changeResistant to noiseNetwork traffic/resource managementTime-division multiplexTime informationMobile business

A digital broadcasting system and a data processing method are disclosed. The data processing method includes receiving a broadcast signal in which main service data and mobile service data are multiplexed, demodulating the broadcast signal to acquire fast-information-channel signaling information including reference time information for a system clock, and outputting demodulation time information of a specific position of a frame of the broadcast signal, decoding the fast-information-channel signaling information, and establishing the reference time information as the system clock at a demodulation time according to on the outputted demodulation time information and decoding the mobile service data according to the system clock.

Owner:LG ELECTRONICS INC

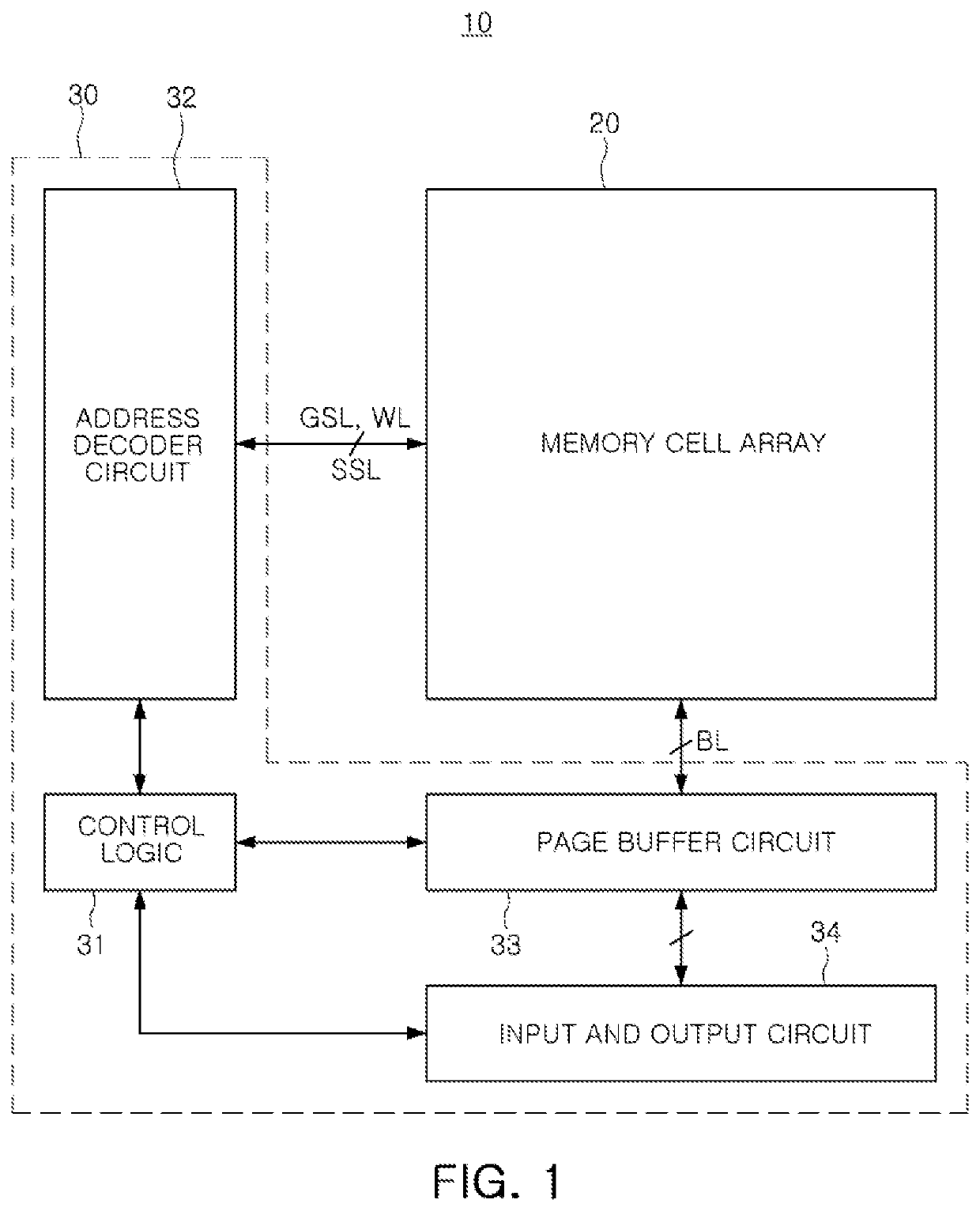

Page buffer and memory device including the same

ActiveUS20210050049A1Resistant to noiseReduce effective capacitanceRead-only memoriesDigital storagePage buffersComputer hardware

A memory device includes a first page buffer supplying a first bias voltage to a selected bitline in a bitline precharge phase; and a second page buffer supplying a second bias voltage to an unselected bitline, adjacent to the selected bitline, in the bitline precharge phase, wherein the first page buffer includes a first bitline precharge circuit supplying the first bias voltage to the selected bitline, the second page buffer includes a second bitline precharge circuit supplying the second bias voltage to the unselected bitline, wherein the second page buffer floats the unselected bitline in a sensing phase for detecting data of a selected memory cell connected to the selected to bitline.

Owner:SAMSUNG ELECTRONICS CO LTD

Device for non-invasive measurement of blood pressure and ankle-brachial index

ActiveUS8409105B2Accurate pressurePerformed easily and reliablyEvaluation of blood vesselsCatheterBlood pressure cuffsBlood pressure cuff

A device for non-invasive measurement of blood pressure includes a blood pressure cuff, a plethysmographic electrode for acquiring an impedance plethysmogram distal to the cuff and a processing device to inflate and deflate the cuff, generate the impedance plethysmogram and to determine the systolic and diastolic blood pressures. It is determined when the cuff is completely occluding the extremity, e.g., by detecting pulses at a second, partially occluded cuff or by a photoplethysmogram attached to the big toe. The device can be used to measure systolic or diastolic blood pressure or both. It can also be used to take ankle-brachial measurements. An autocorrelation technique can be used to correct noise.

Owner:SMITHMARKS INC

Magnetic detection circuit and encoder

InactiveUS7391206B2LessResistant to noiseNanomagnetismMagnetic-field-controlled resistorsDifferential signalingCurrent source

To provide a low-cost magnetic detection circuit, in which the differential detection function accomplished by outputting differential signals may not be lost, and which may be hardly affected by temperature fluctuations and may be resistant to noise, and in which the number of magnetic detection elements may be reduced, and to provide an encoder, the costs of which may be further reduced by using such a magnetic detection circuit for the multi-revolution detection part, etc., a magnetic detection circuit includes a bridge circuit formed by two bridge sections between the current-source terminal and the grounding terminal. The first bridge section and the second bridge section of the bridge circuit include magnetic detection elements MR1, MR2, respectively, and, viewed from the output-signal output points, the magnetic detection elements MR1, MR2 in the two bridge sections are arranged on only one of the sides that include the current-source side and the grounding-terminal side. An encoder includes such a magnetic detection circuit.

Owner:DR JOHANNES HEIDENHAIN GMBH

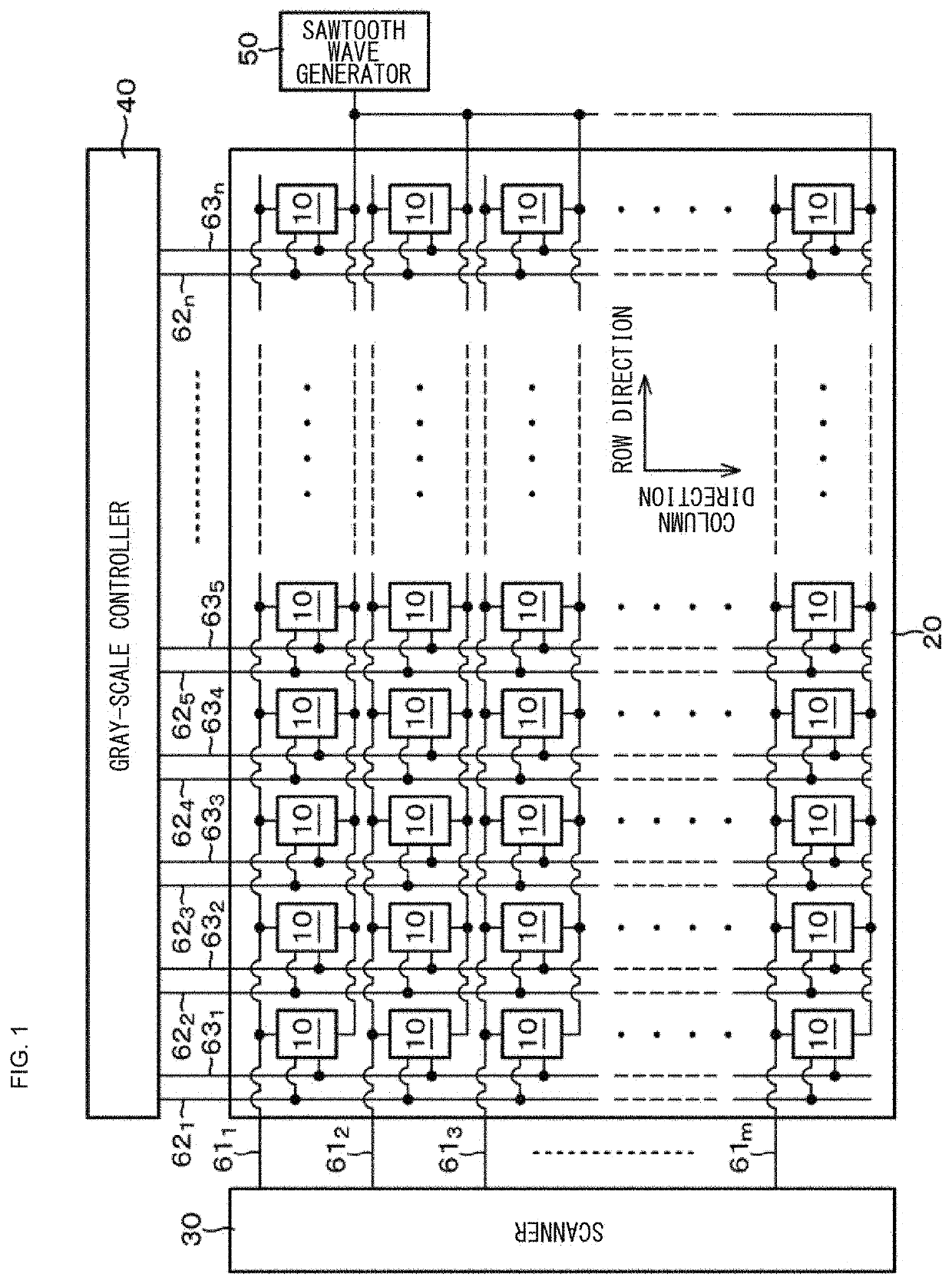

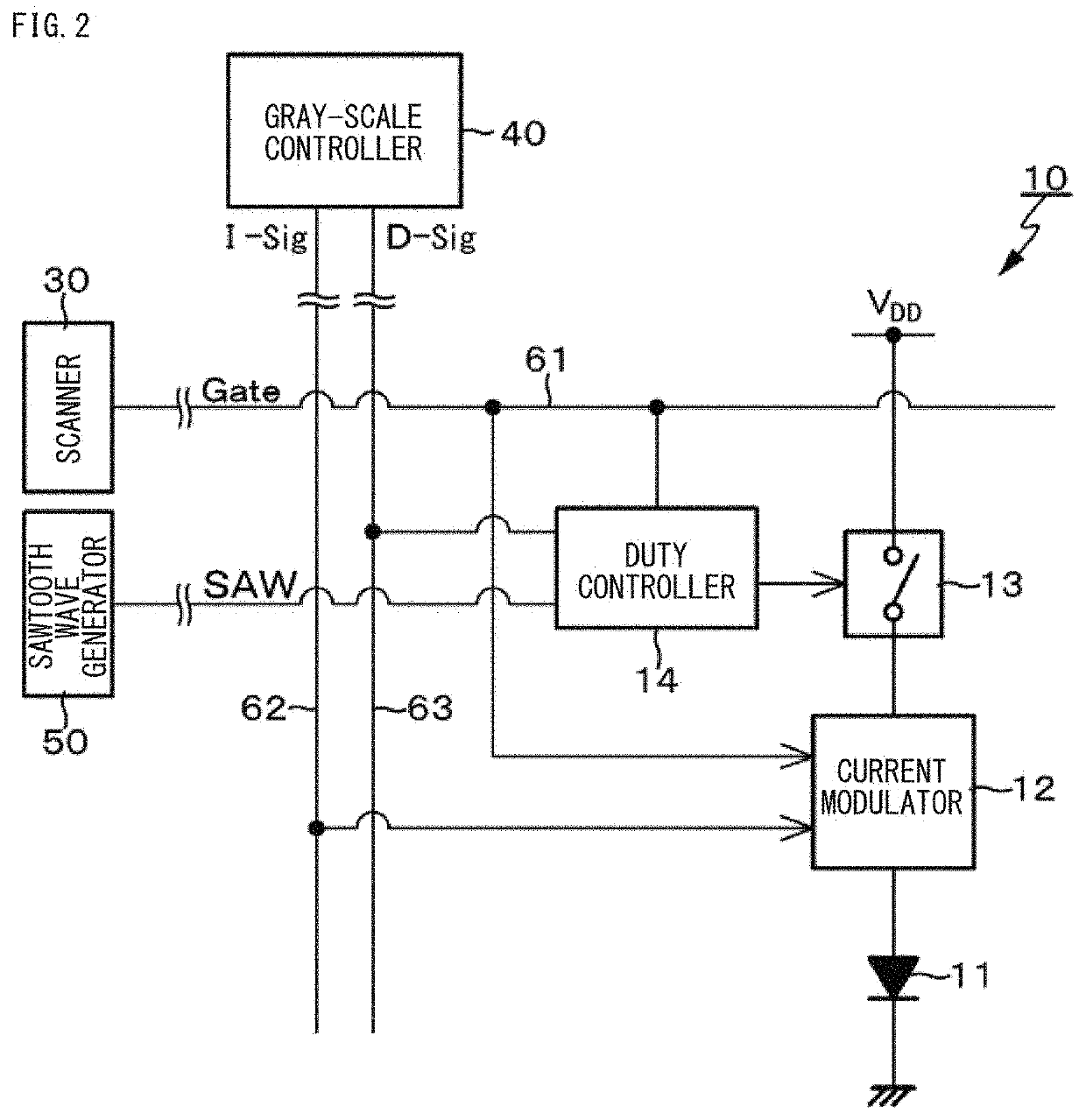

Display device, method of driving display device, and electronic apparatus

ActiveUS20220208066A1High gray-scale performanceResistant to noiseCathode-ray tube indicatorsSemiconductor devicesComputer hardwareDisplay device

A display device of the present disclosure is provided with a pixel circuit that includes a light-emitting element; a current modulator that controls a current value flowing through the light-emitting element; a current breaker that interrupts a current flowing through the light-emitting element; and a gray-scale controller that controls the current modulator and the current breaker to perform gray-scale control. The gray-scale controller discretely controls a light emission duty of the light-emitting element through the current breaker, and controls, through the current modulator, the current value flowing through the light-emitting element in accordance with the light emission duty of the light-emitting element.

Owner:SONY CORP

High hysteresis width input circuit

InactiveUS20050212579A1Large hysteresis widthResistant to noiseElectric pulse generatorMOSFETHysteresis

The present invention is constructed of a first input circuit having a higher logic level VIH made up of a first inverter circuit 22 controlled by an input signal and an N-type MOSFET 16 controlled by a latch circuit 24 which stores a preceding state, a second input circuit having a lower logic level VIL made up of a second inverter circuit 23 controlled by an input signal and a P-type MOSFET 15 controlled by a latch circuit which stores a preceding state and the latch circuit 24 which stores a preceding state.

Owner:SEIKO EPSON CORP

Led driver with ability to operate at arbitrarily low input voltages

ActiveUS10999911B2Improvement in performance and applicabilityReduce input voltageElectric circuit arrangementsElectroluminescent light sourcesMOSFETLinear regulator

An LED driver with ability to operate at low input voltages is disclosed. The LED driver comprises a boost converter to boost an input voltage to a desired output voltage to power one or more LED strings. The boost converter incorporates a first controllable switch, such as a metal-oxide-semiconductor field-effect transistor (MOSFET), IGBT, etc., for output voltage control. The boost converter receives input from an external source, such as a battery voltage, as power source for voltage boost operation. The first controllable switch couples to a gate driver powered by a linear regulator, which switchably couples to different voltage sources via a second switch to ensure that the gate driver is able to provide enough voltage for switching the first controllable switch.

Owner:MAXIM INTEGRATED PROD INC

Digital broadcasting system and method of processing data in digital broadcasting system

InactiveUS8386893B2Resistant to changeResistant to noiseTelevision system detailsPicture reproducers using cathode ray tubesMobile businessDigital audio broadcasting

A digital broadcasting system and a data processing method are disclosed. The method includes, receiving a broadcast signal in which mobile service data and main service data are multiplexed, extracting transmission parameter signaling information and fast-information-channel signaling information from a data group contained in the received mobile service data, parsing first program table information, which describes virtual channel information and a service of an ensemble acting as a virtual channel group of the received mobile service data, using the fast-information-channel signaling information, parsing second program table information including a data chunk acting as data-broadcasting contents of the mobile service data, and providing a data broadcasting service using the data broadcasting contents of the parsed second program table information.

Owner:LG ELECTRONICS INC

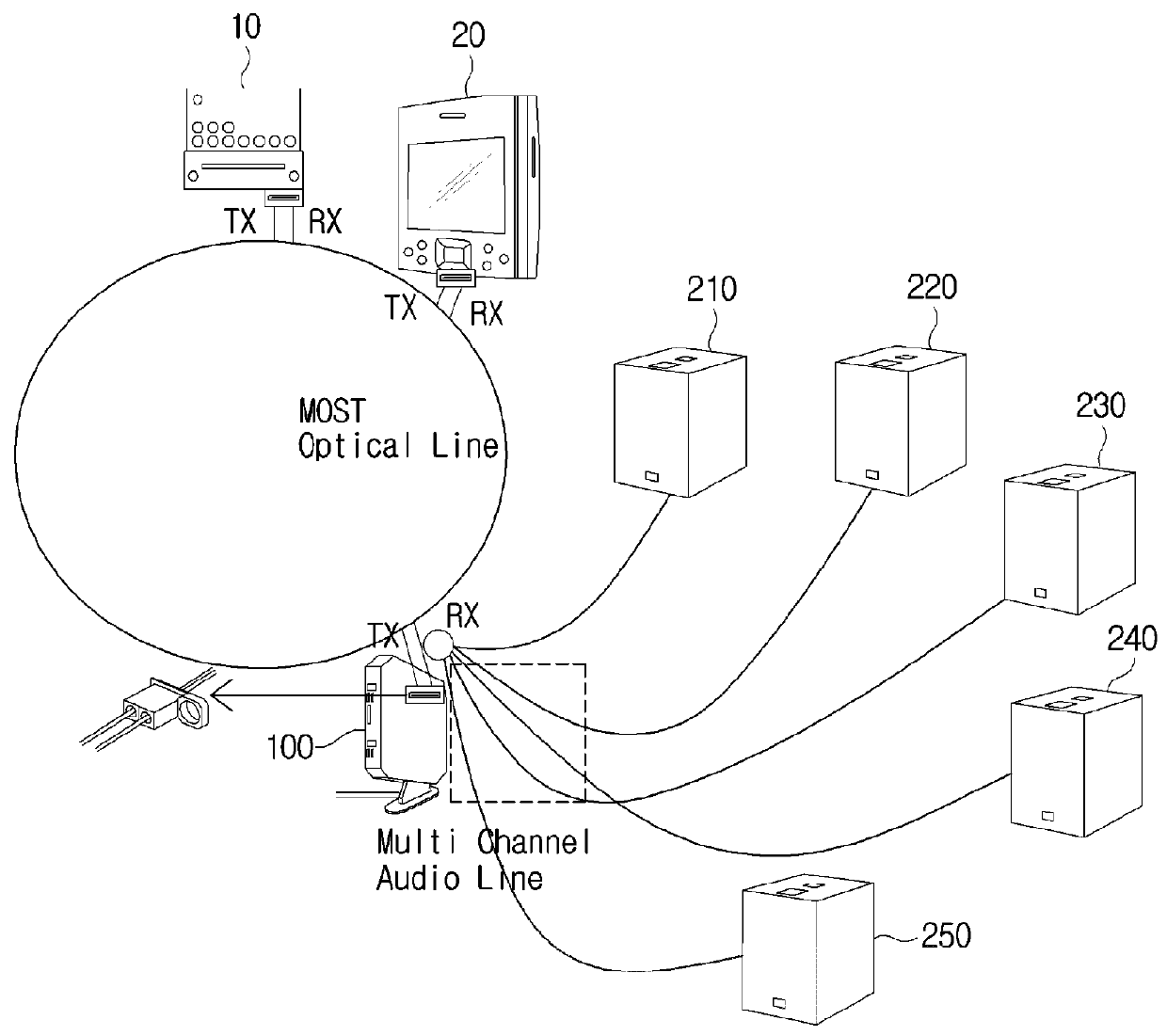

Audio system based on in-vehicle optical network and broadcasting method thereof

ActiveUS9998224B2Resistant to noiseBroadcast circuit arrangementsElectromagnetic network arrangementsIn vehicleLoudspeaker

An audio system based on an in-vehicle optical network and a broadcasting method thereof are provided. The audio system according to an exemplary embodiment includes: a multi-channel router which is connected to an in-vehicle optical network to receive a multi-channel audio signal from audio signals received from the optical network; and a plurality of speakers which are connected to the multi-channel router to receive the multi-channel audio signal through the multi-channel router. Accordingly, the speakers can operate by interworking with a network even when they have no function as network devices.

Owner:KOREA ELECTRONICS TECH INST

Digital broadcasting system and method of processing data in digital broadcasting system

InactiveUS8683529B2Resistant to changeResistant to noiseTelevision system detailsError preventionMobile businessDigital broadcasting

The present invention provides a method of processing data. The method of processing data includes receiving a broadcasting signal where mobile service data are multiplexed with main service data, extracting transmission-parameter-channel signaling information and fast-information-channel signaling information from a data group within the received mobile service data; obtaining first program table information describing virtual channel information of an ensemble and a service provided by the ensemble using the fast-information-channel signaling information, the ensemble the ensemble corresponding to a virtual channel group of the received mobile service data, obtaining information indicating that second program table information, which describes an additional service provided by the ensemble, is included in the ensemblem and parsing the second program table information according to the obtained information; and providing the additional service by using the second program table information.

Owner:LG ELECTRONICS INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com