Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

34results about How to "Eliminate drop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

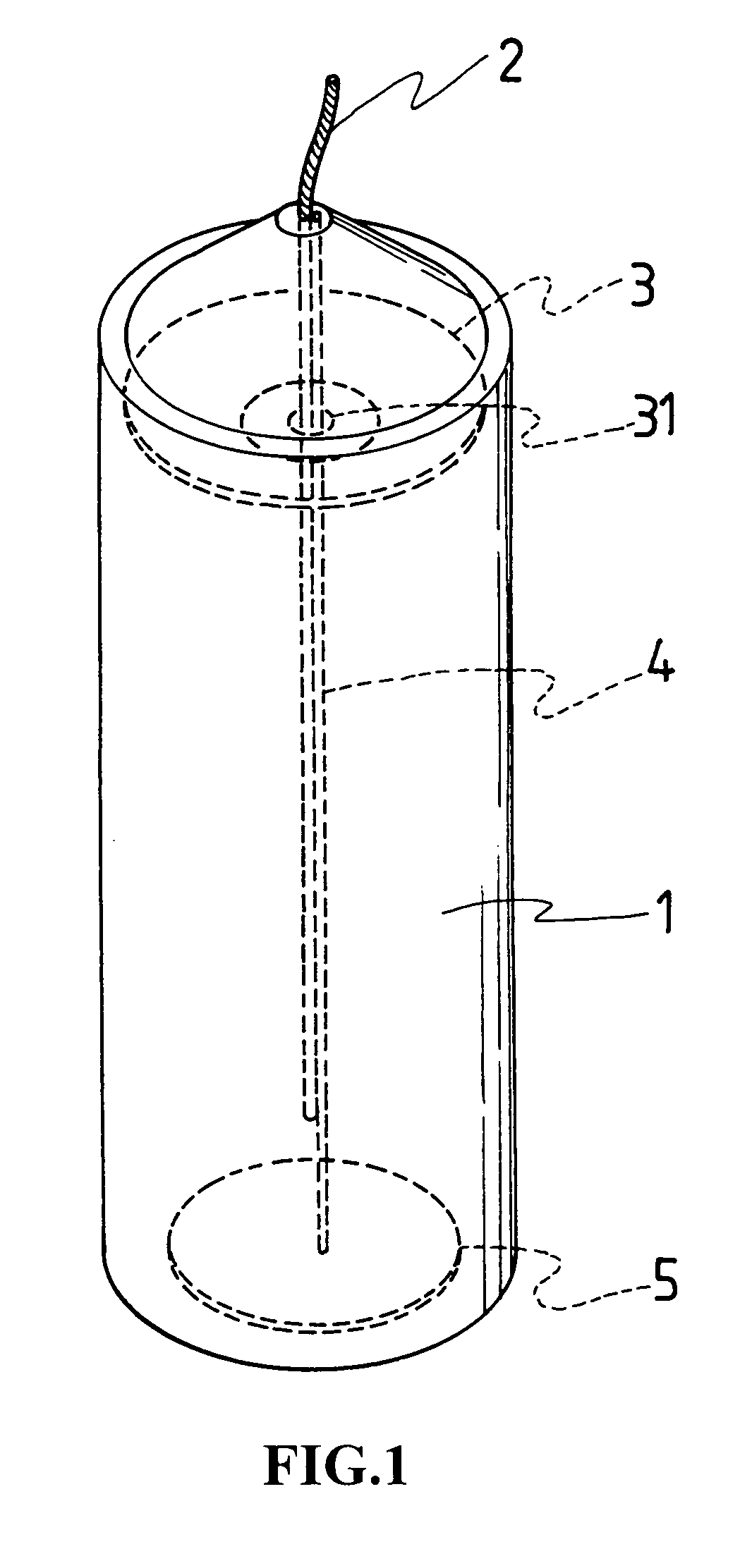

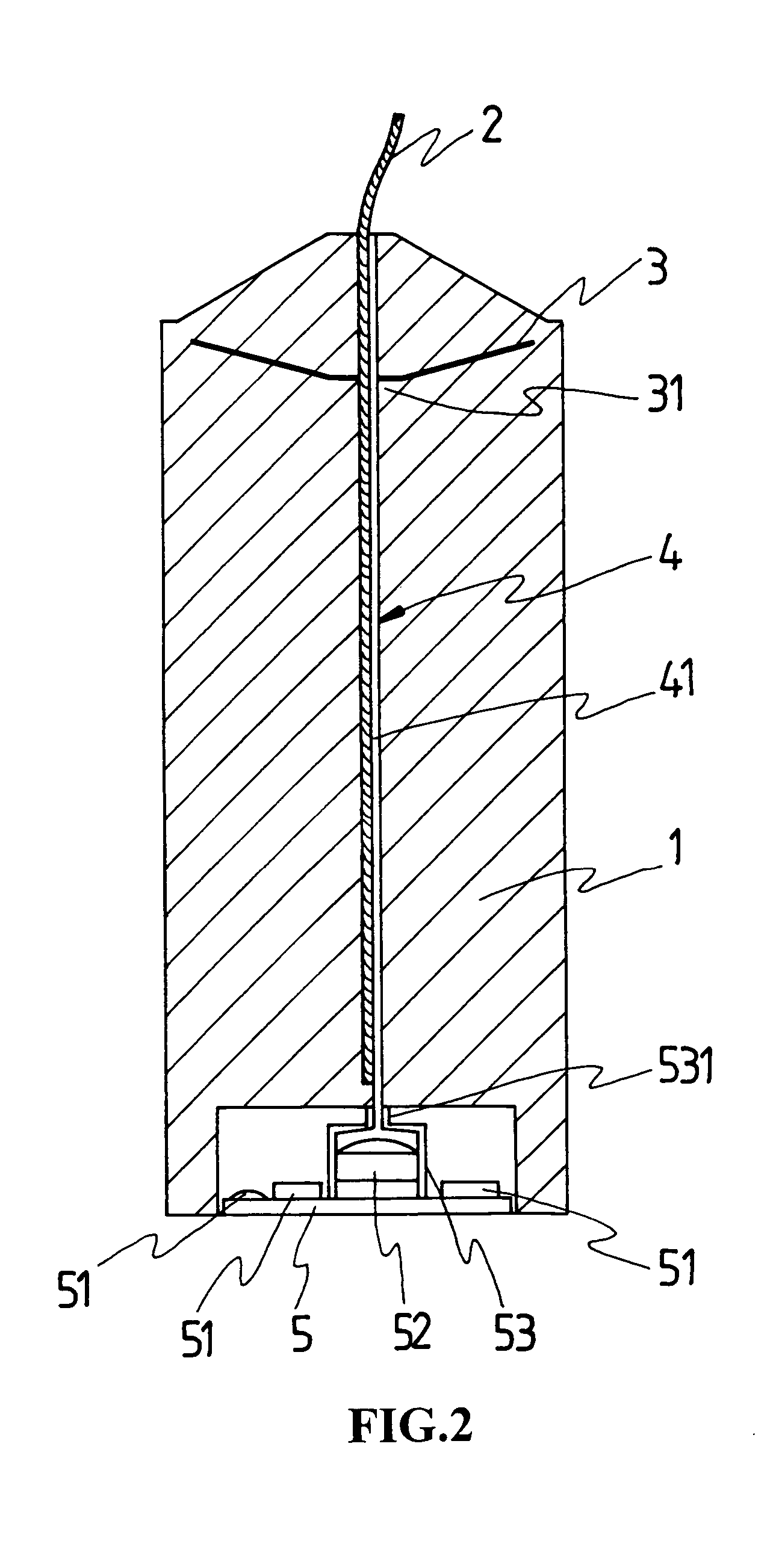

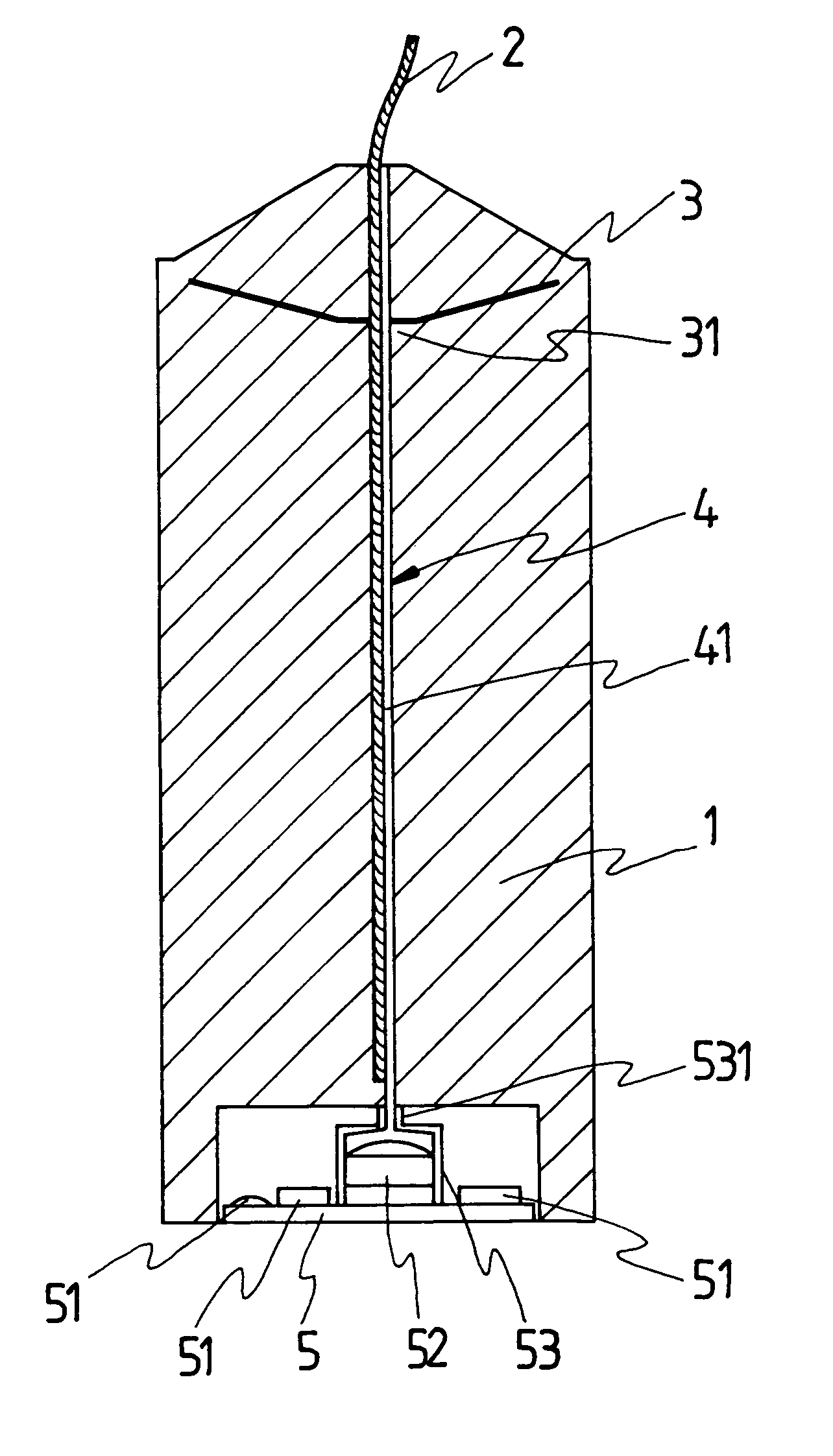

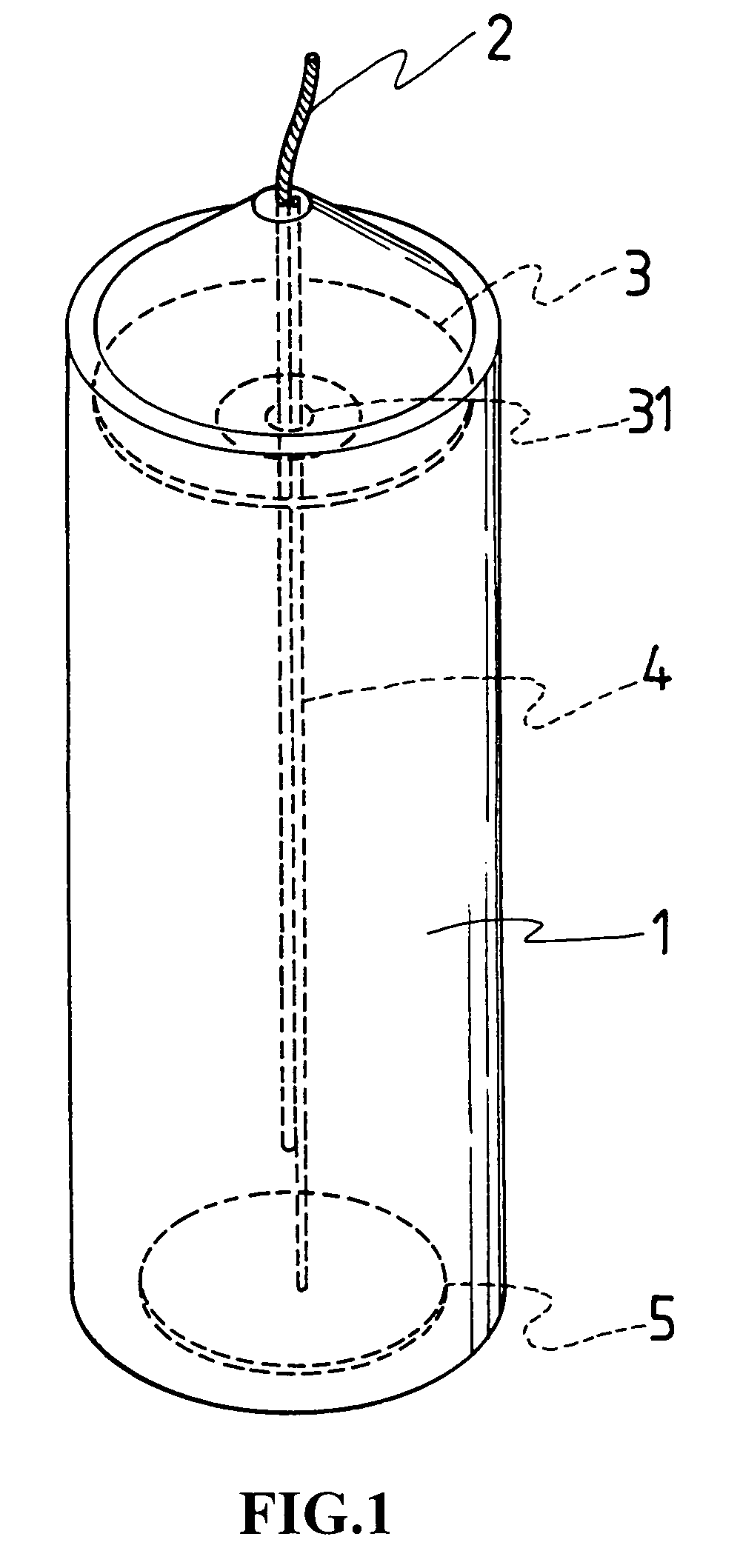

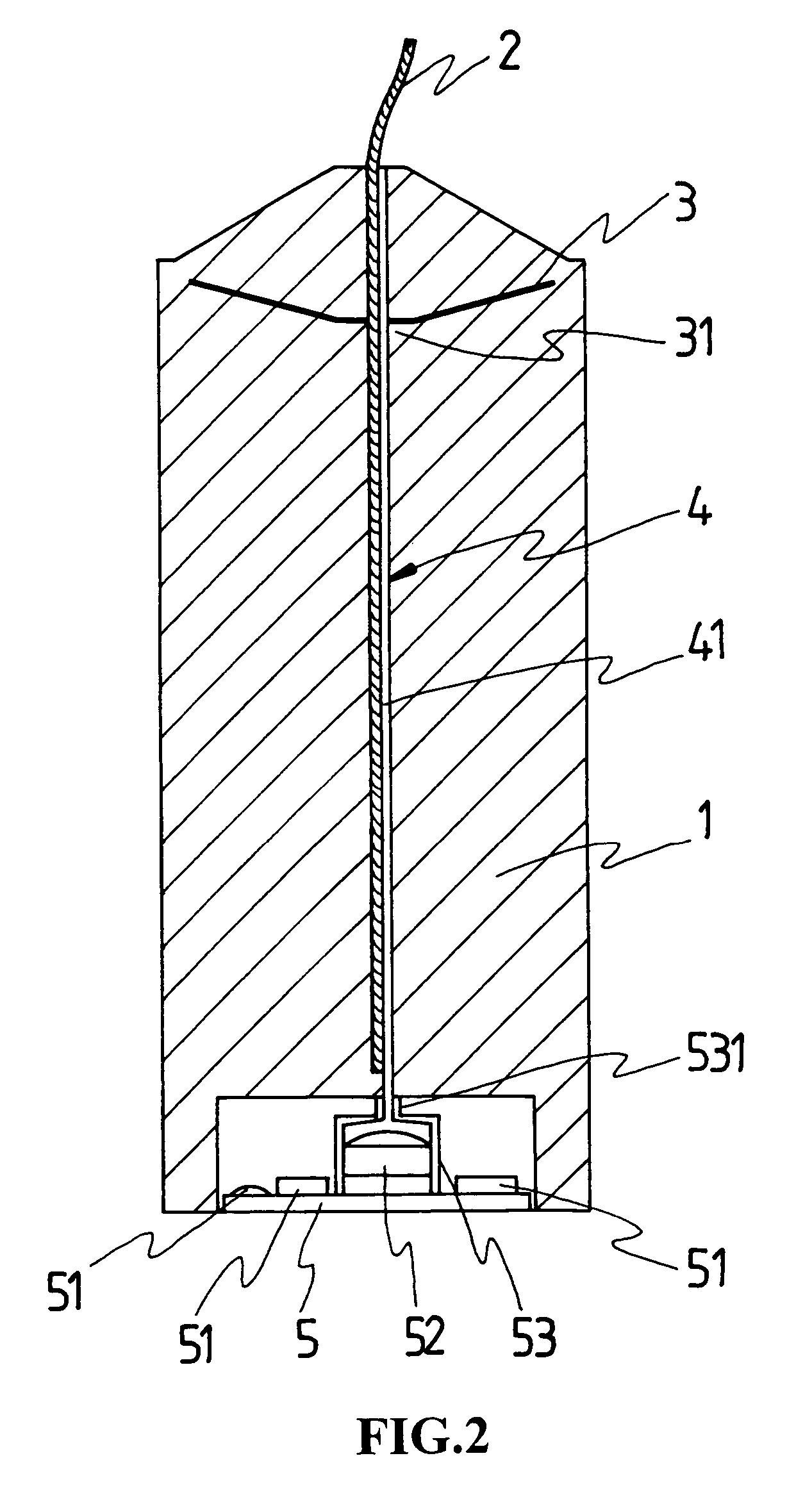

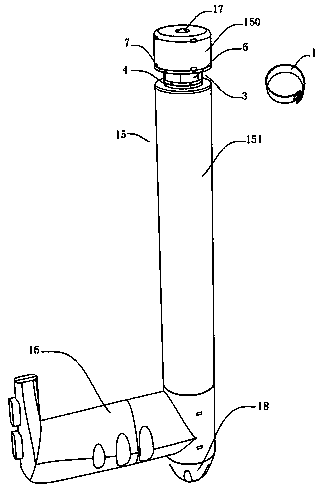

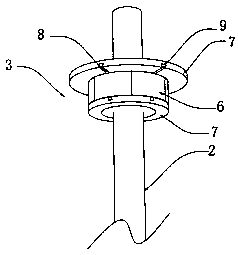

Electronic switch for drop-free candle

An electronic switch for a drop-free candle is comprised of a candle, a wick, a metal disk, a conductor and a circuit board; the metal disk being buried in the candle; the conductor being provided in the form of an optical fiber or a magnet twisted pair cable; the conductor being provided along the wick to control the operation of the circuit board provided at the bottom of the candle to realize the function of an electronic switch while preventing drops of the fatting substance of the candle.

Owner:YU SHUNG LUN

Electronic switch for drop-free candle

InactiveUS6960076B2Eliminate dropImprove securityFuel lightersCapillary burnersElectrical conductorElectronic switch

An electronic switch for a drop-free candle is comprised of a candle, a wick, a metal disk, a conductor and a circuit board; the metal disk being buried in the candle; the conductor being provided in the form of an optical fiber or a magnet twisted pair cable; the conductor being provided along the wick to control the operation of the circuit board provided at the bottom of the candle to realize the function of an electronic switch while preventing drops of the fatting substance of the candle.

Owner:YU SHUNG LUN

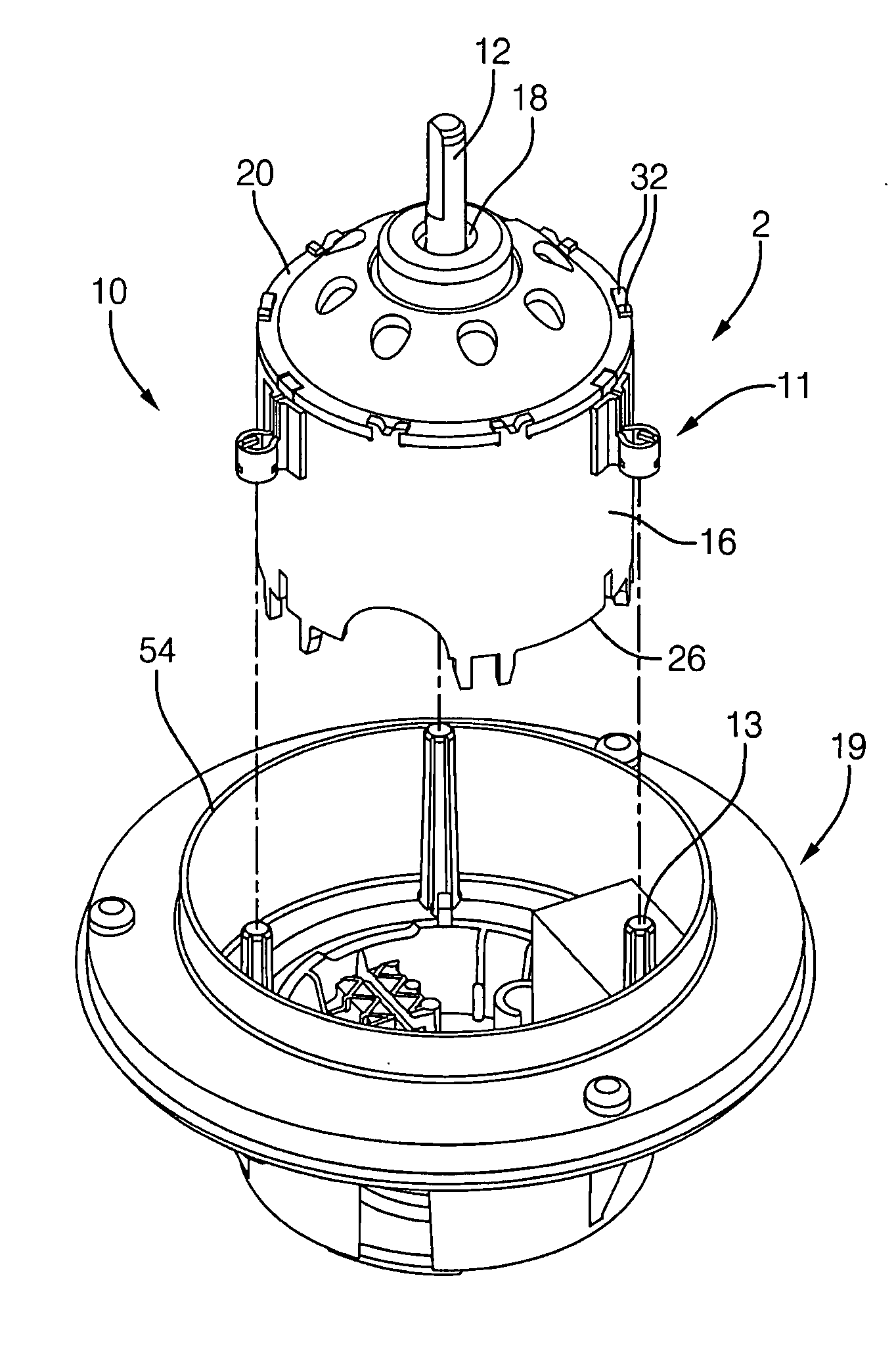

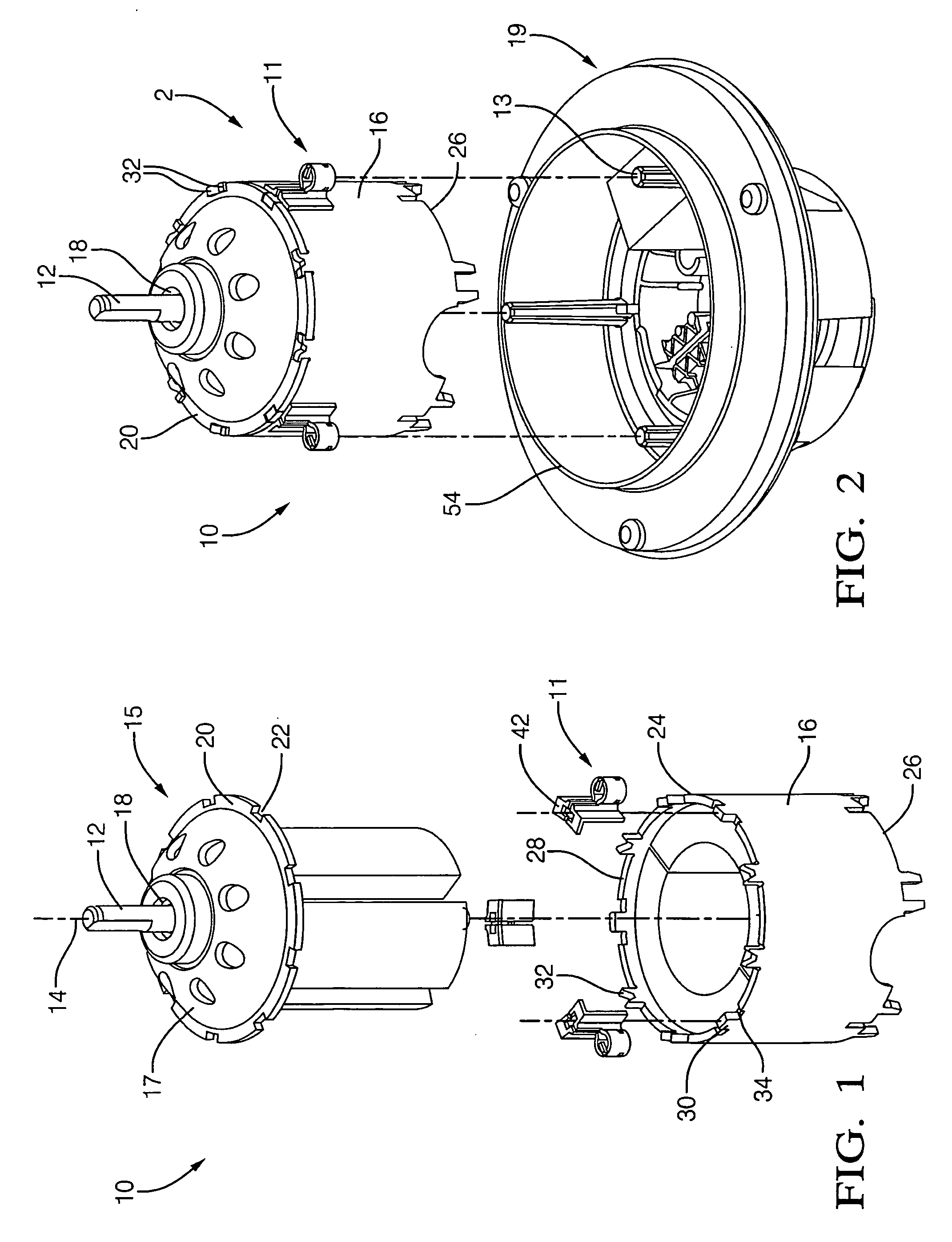

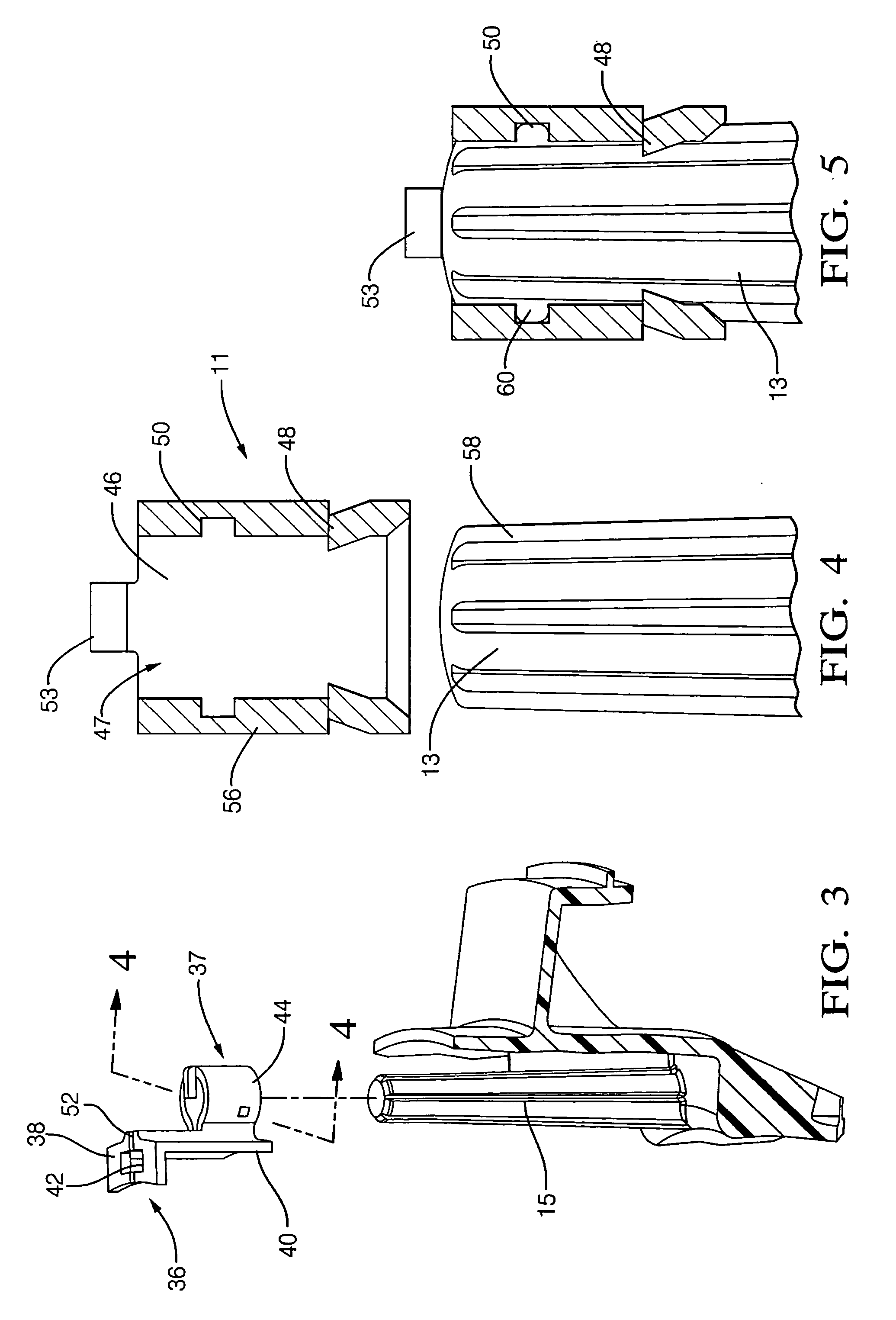

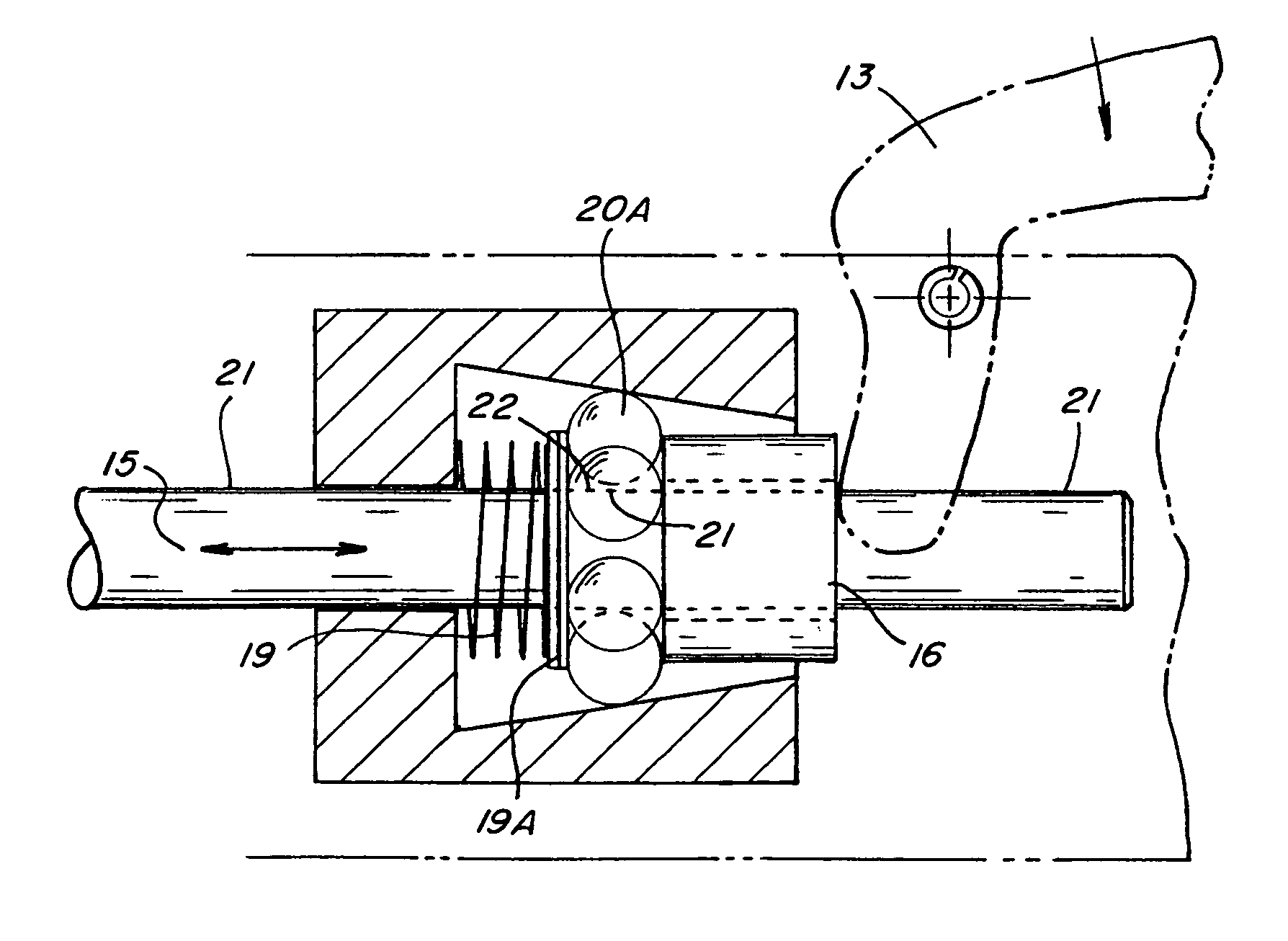

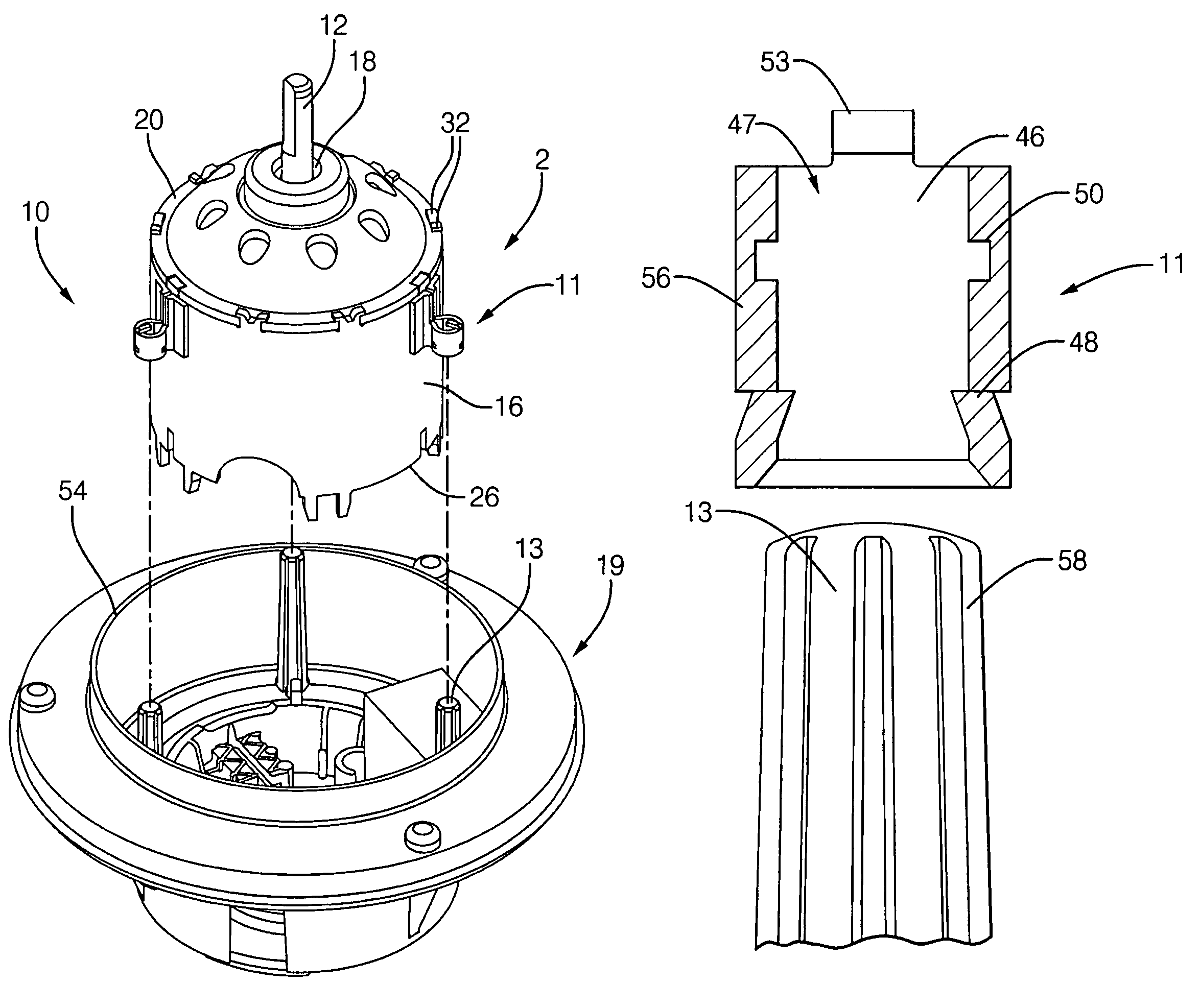

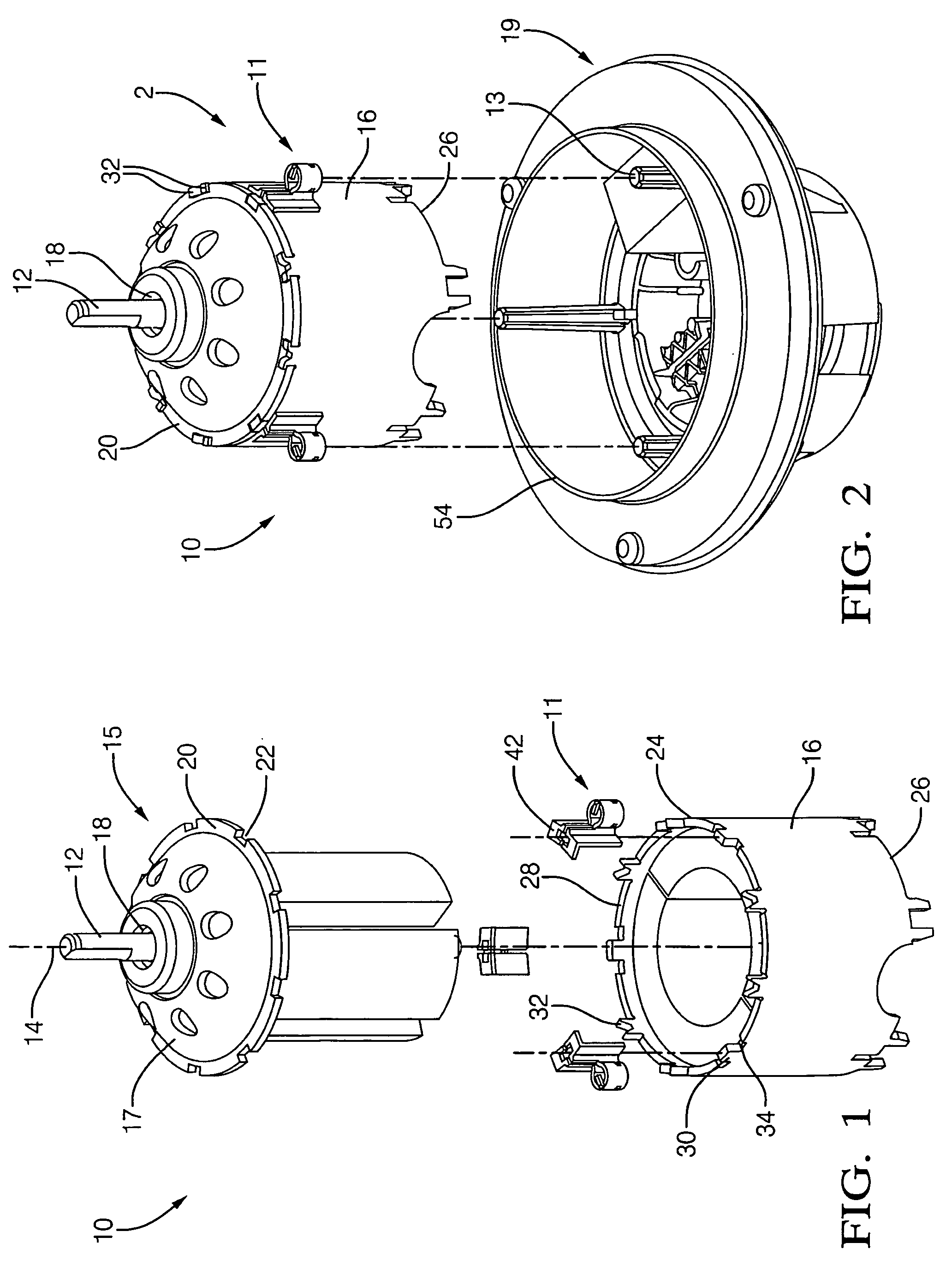

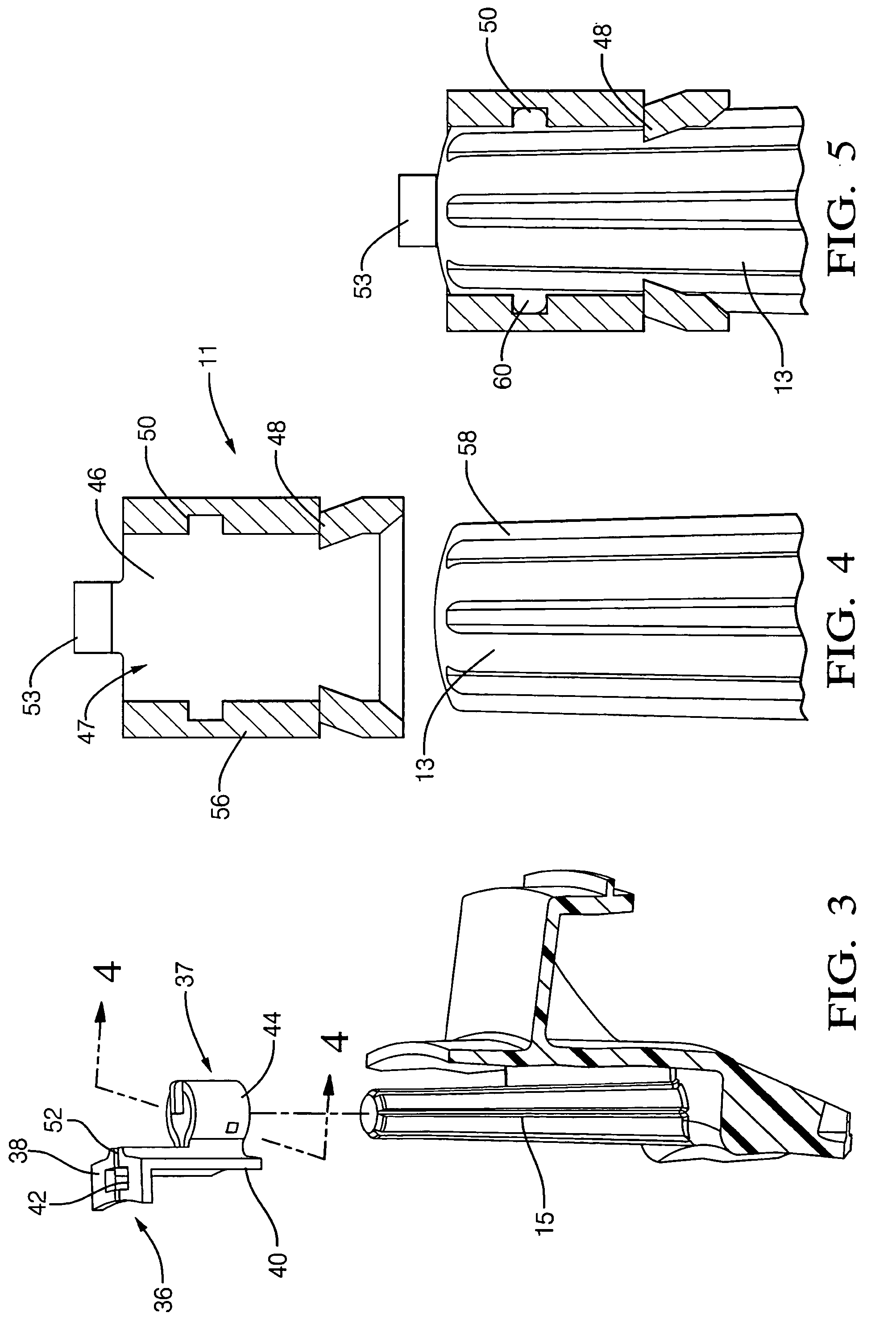

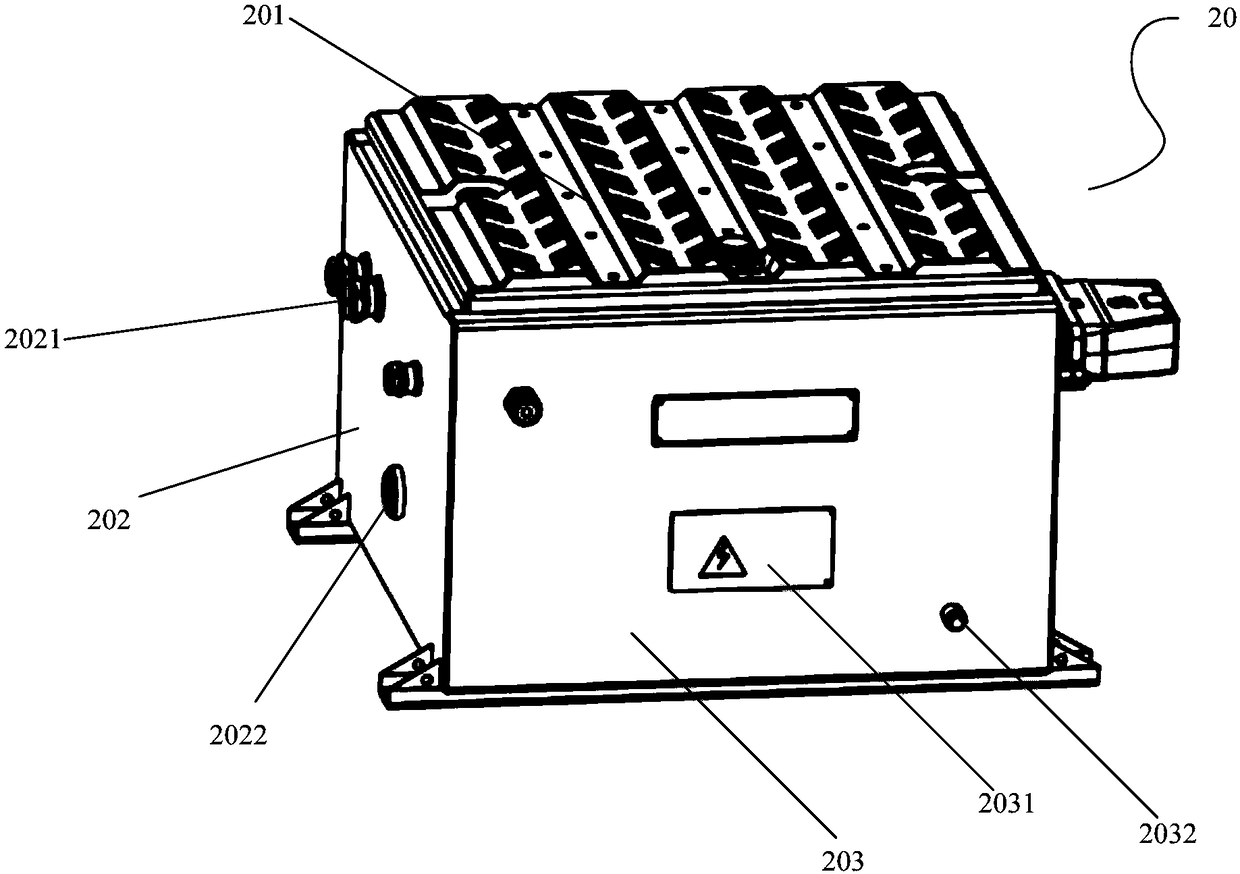

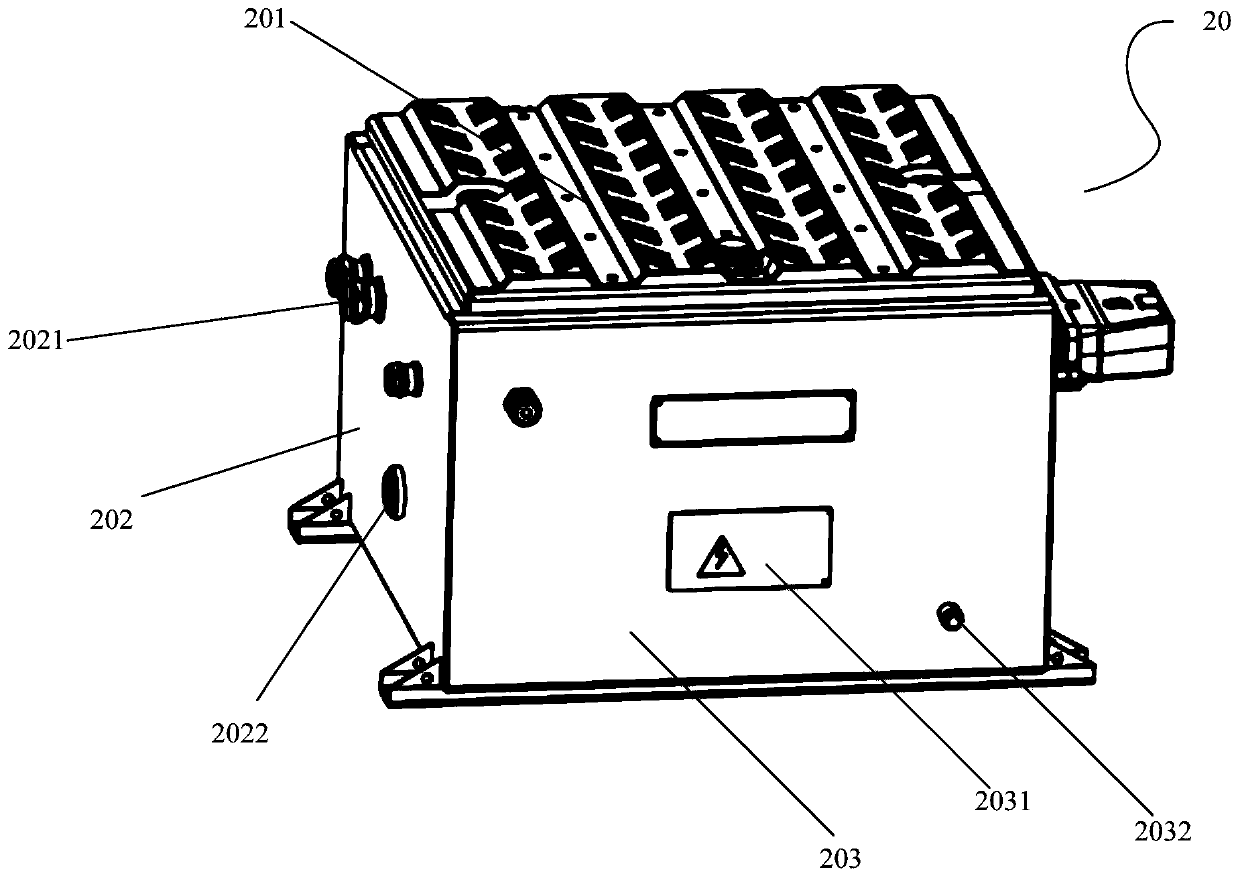

Motor attachment assembly for plastic post isolation system

InactiveUS20090058203A1Eliminate dropReduce complexityPump componentsNon-rotating vibration suppressionVibration isolationIsolation system

The invention provides for a motor attachment assembly that includes an electric motor having spring clips adapted to securely lock onto the isolation posts of a plastic post vibration isolation system. The motor includes an end cap that has notches which cooperate with locator tabs of the motor housing to lock the cap onto the housing with the spring clips therebetween. Each clip includes an axial slot that is expandable in an open direction to receive an isolation post and biased in the closed direction to retain the isolation post. Each clip also has an inner surface with barbs protruding into the channel to allow insertion of the isolation post into the channel in the direction of the output shaft and to resist movement of the isolation post in a direction opposite to the output shaft. The inner surface has a retention groove to receive plastically deformed portions of the isolation post.

Owner:MAHLE INT GMBH

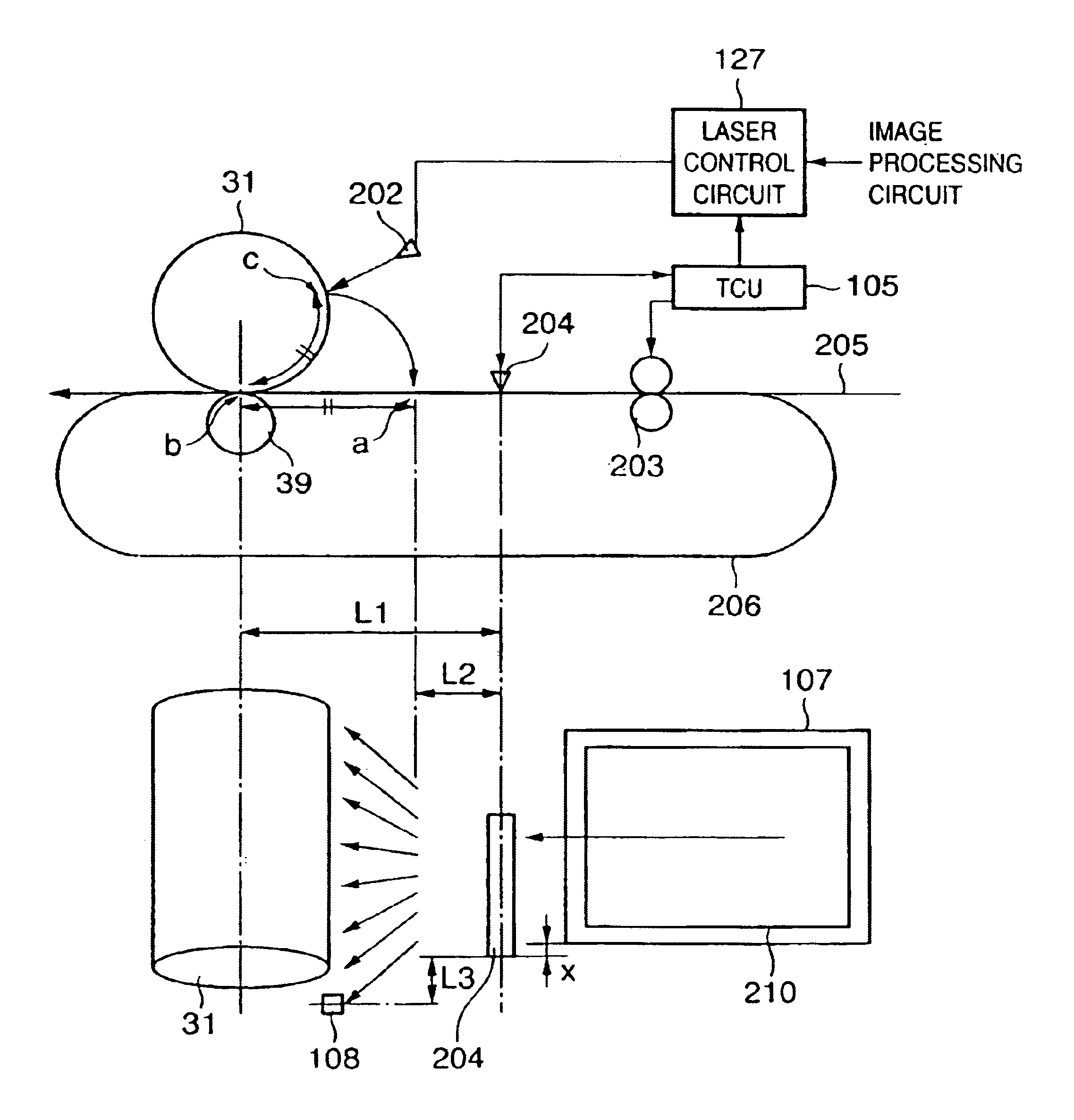

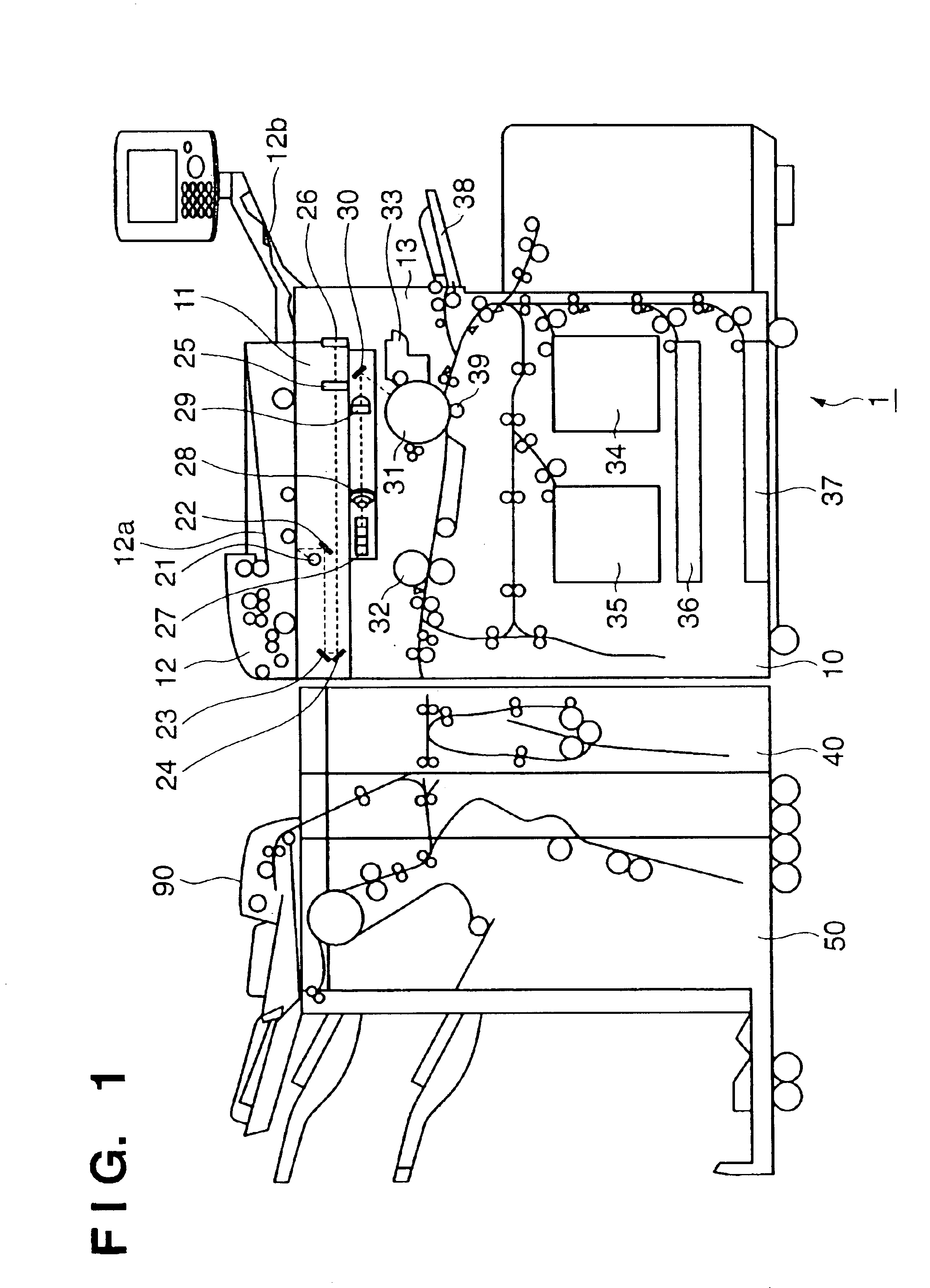

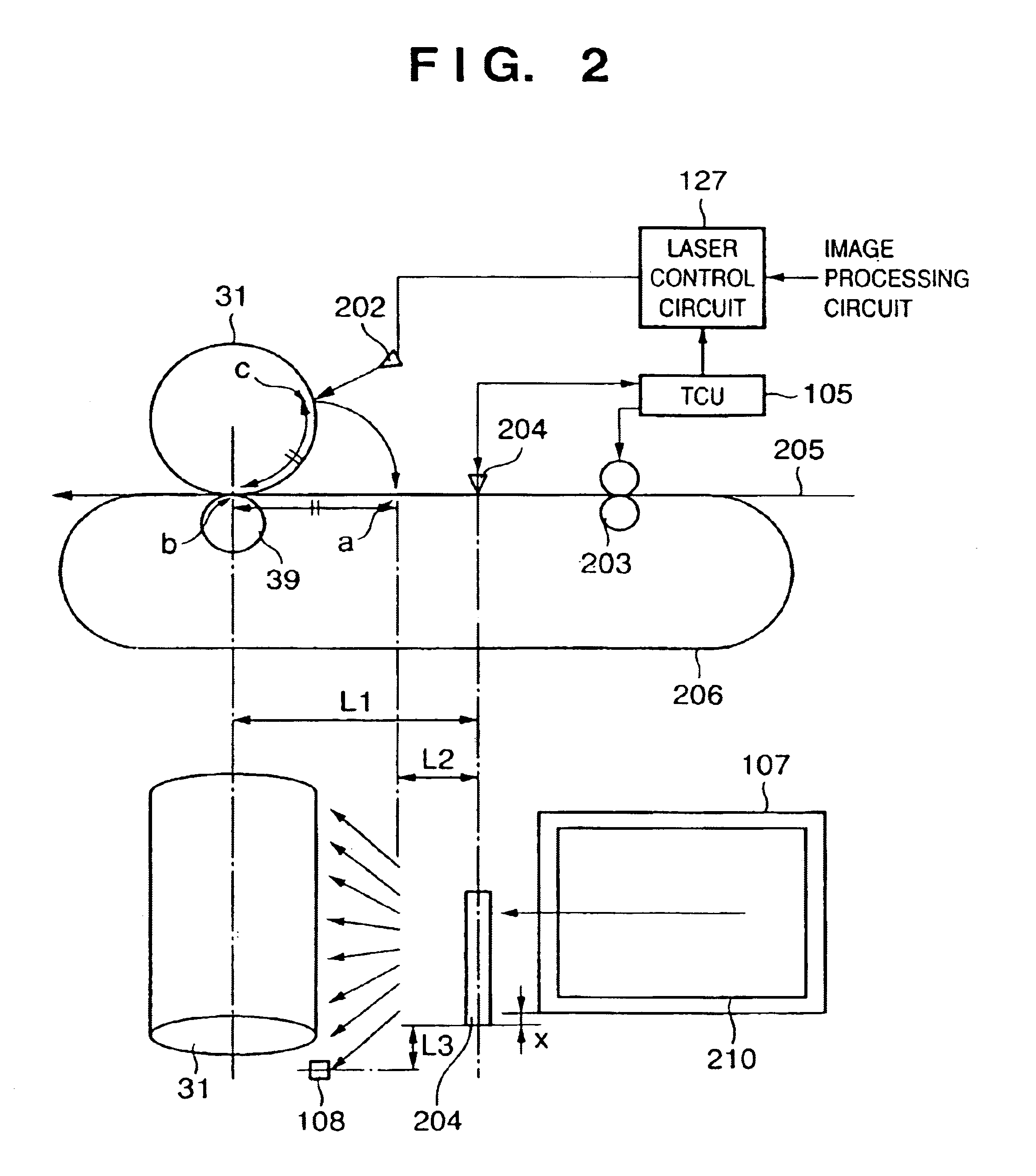

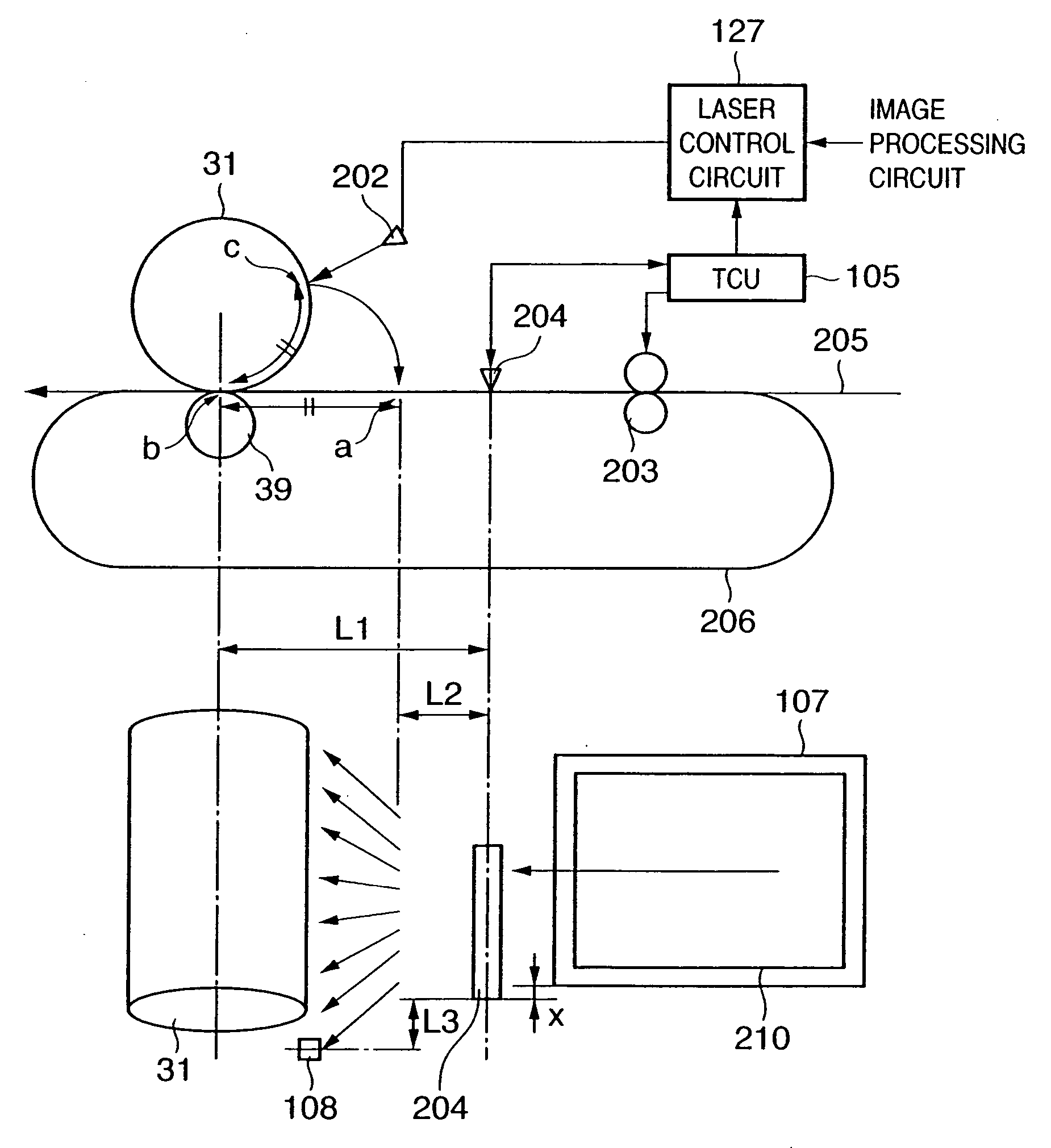

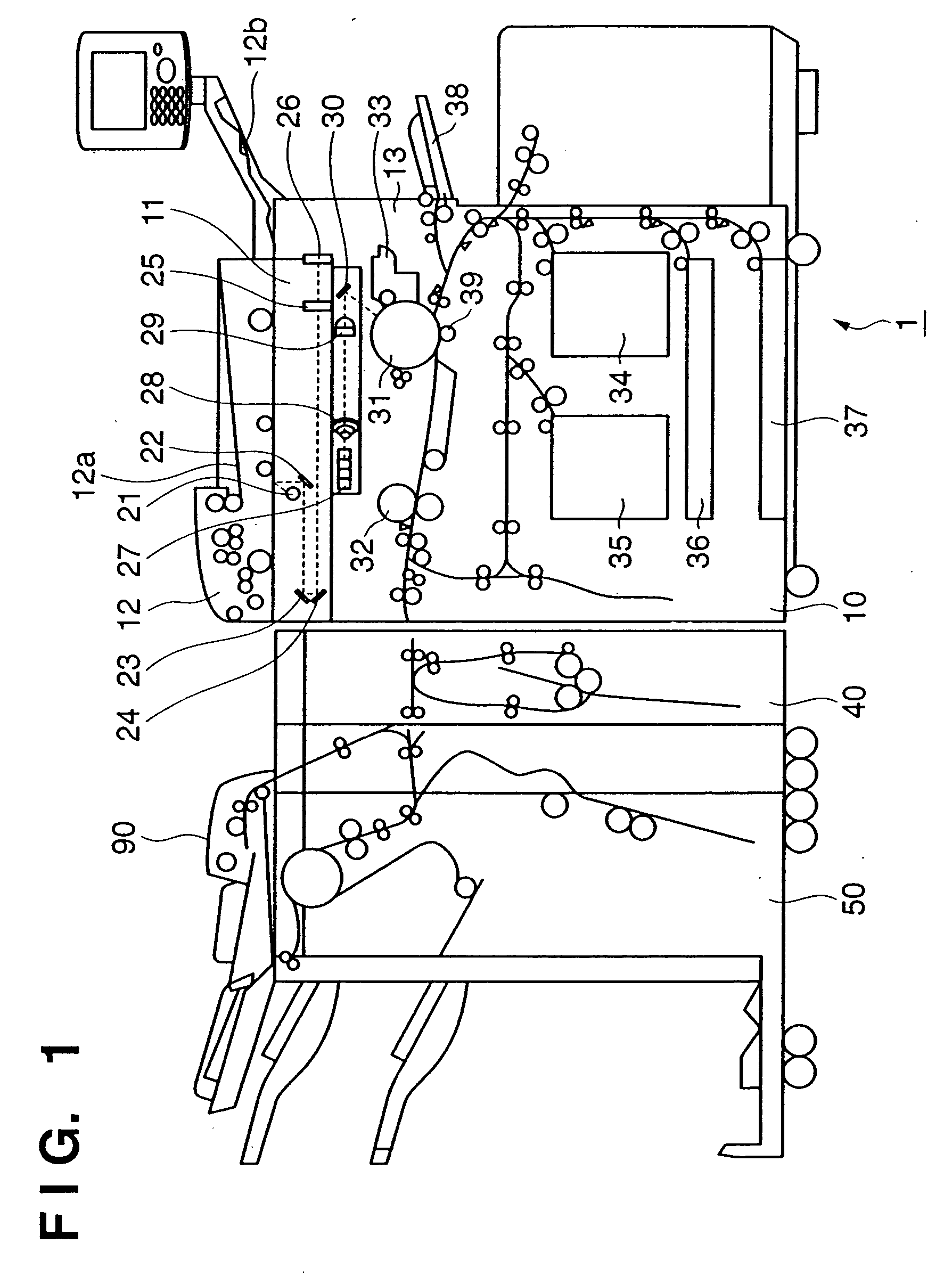

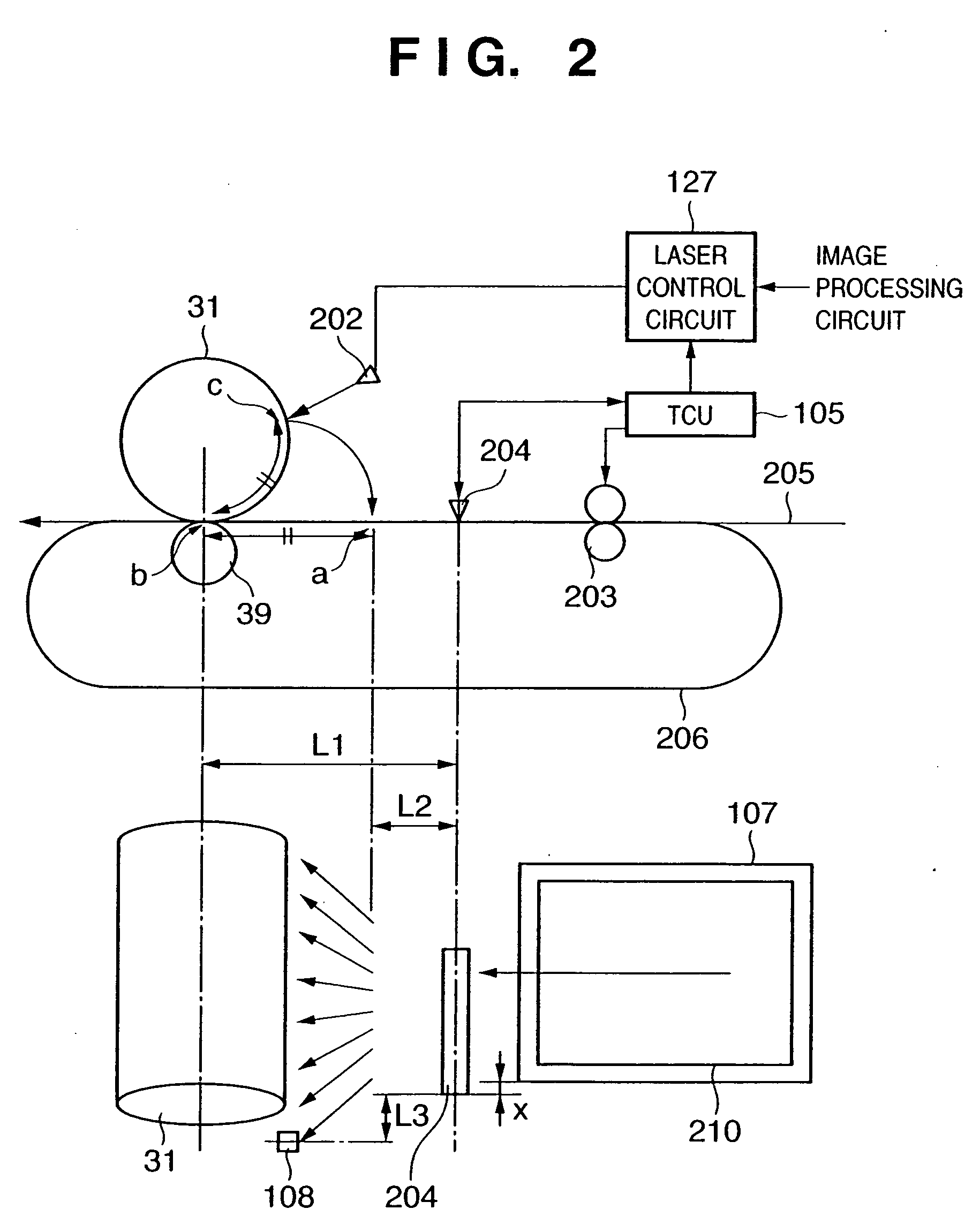

Image forming apparatus and image formation control method

InactiveUS6934504B2Eliminate dropEasy to adjustRegistering devicesElectrographic process apparatusContact image sensorStart time

A frame image (210) with 5-mm wide margins is formed on a paper sheet on the basis of the leading end and widthwise end positions of the paper sheet (107) detected by a contact image sensor (CIS) (204) in an adjustment mode. After that, this paper sheet (107) is circulated to a feed position via a circulating path (206) and paper convey path (205), and the CIS (204) detects the frame image position formed on the circulated paper sheet and its paper end portion so as to detect errors from the 5-mm wide margins. Correction values which can cancel these errors are stored in a correction parameter storage unit (71), and forming start timing control is made using these correction values upon forming an image in an actual job. In this way, an image forming apparatus which can detect the paper feed timing with high precision, can eliminate deterioration of the image position precision due to mounting errors and durability of components, and can always precisely adjust the image position is provided.

Owner:CANON KK

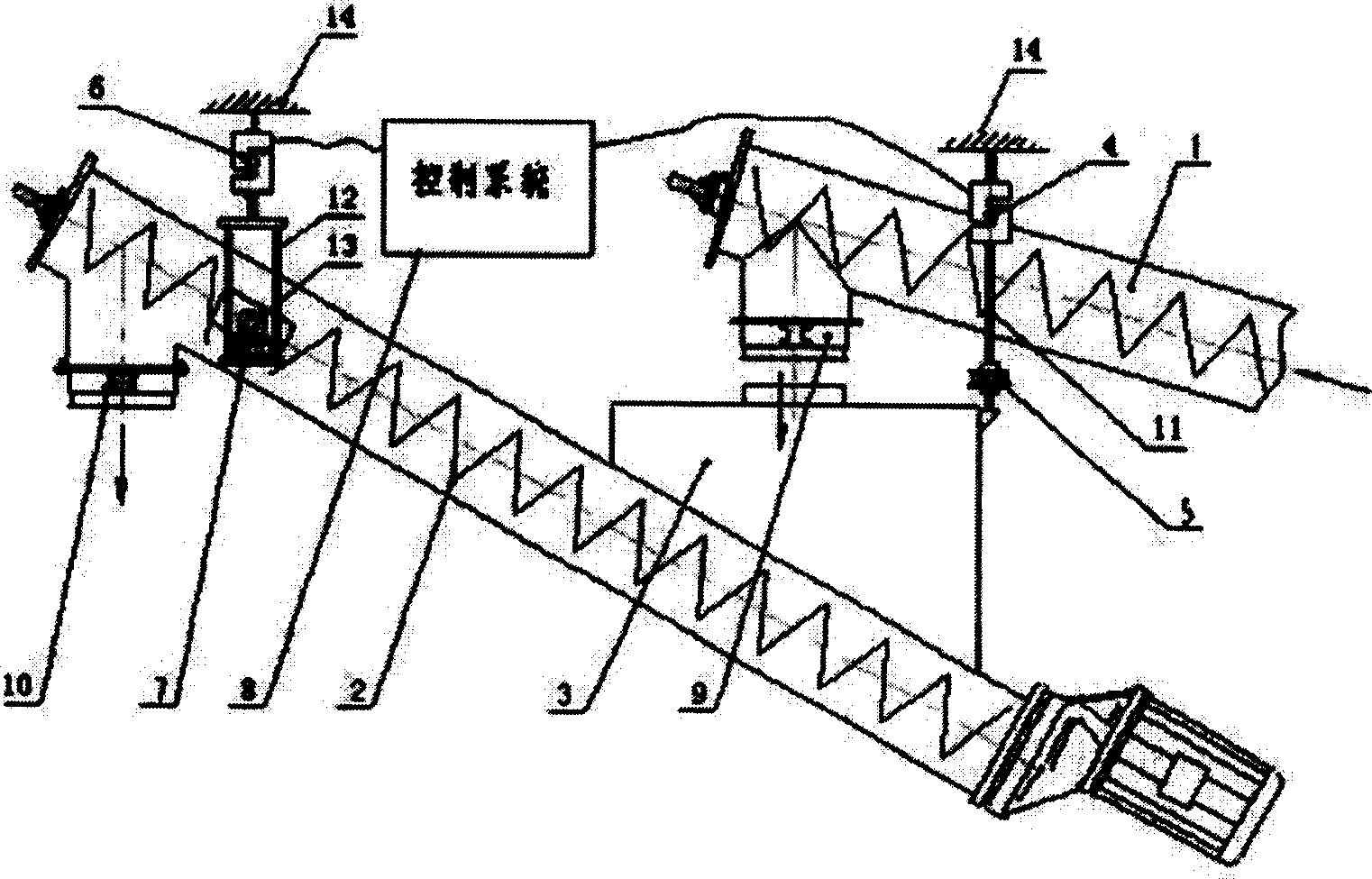

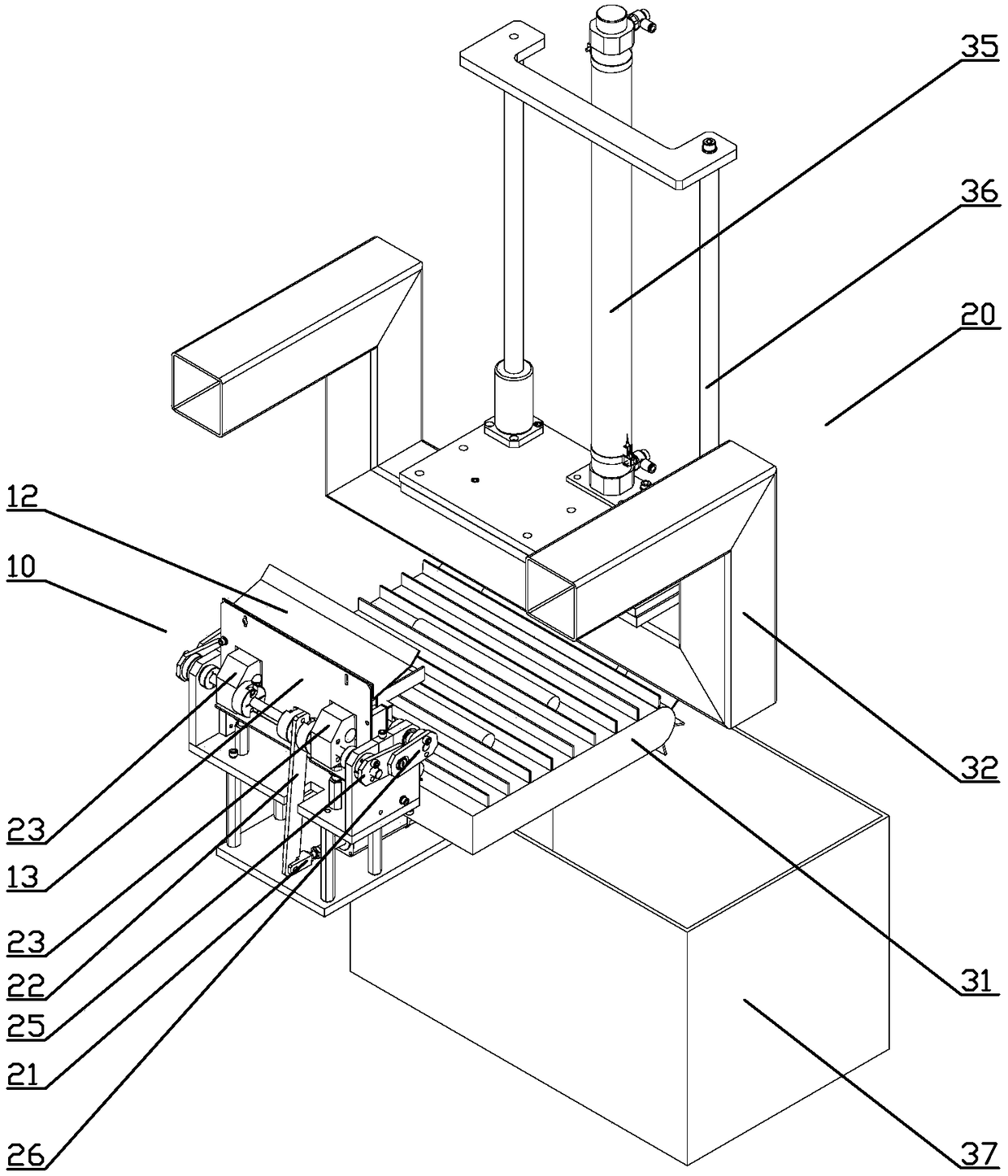

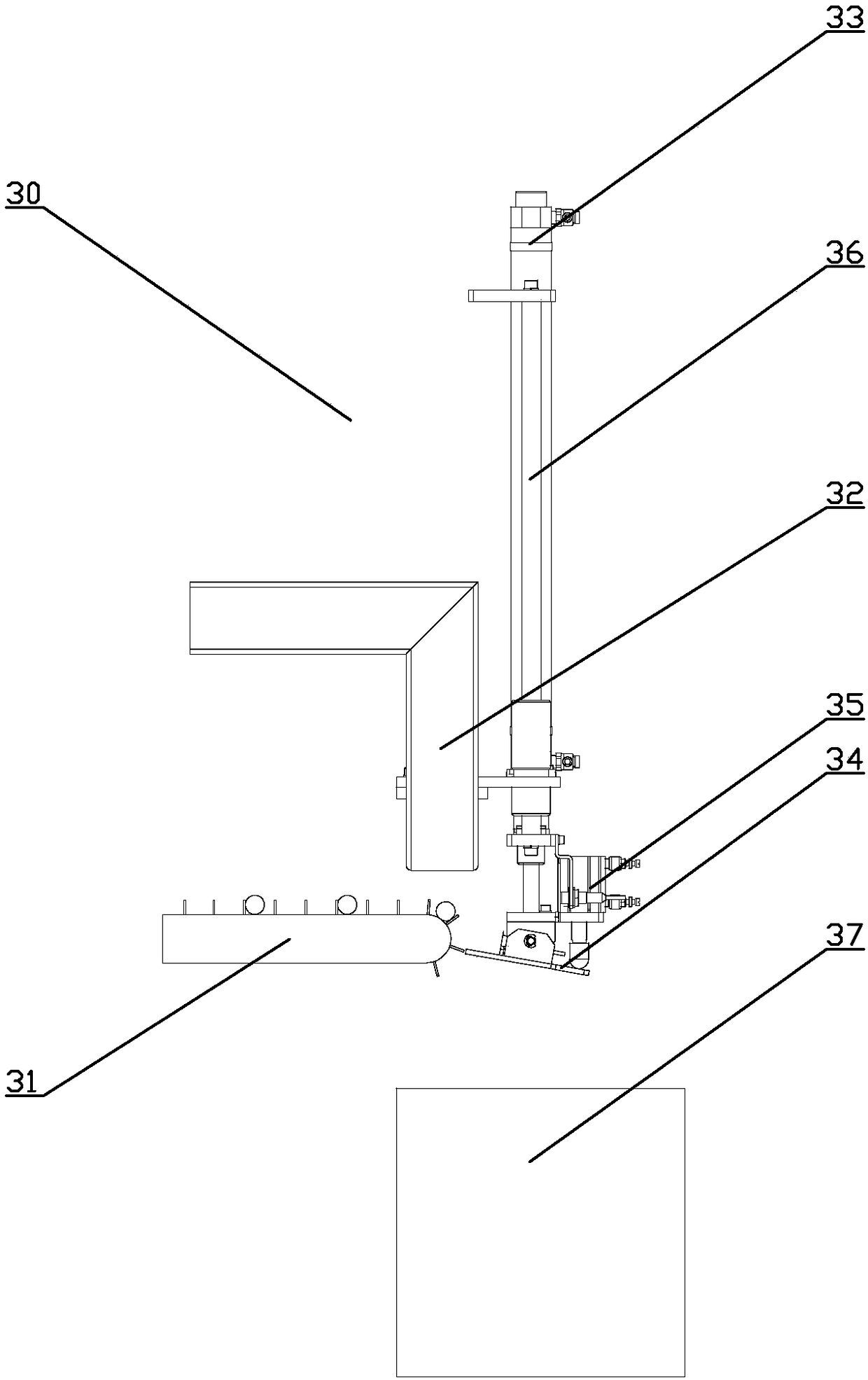

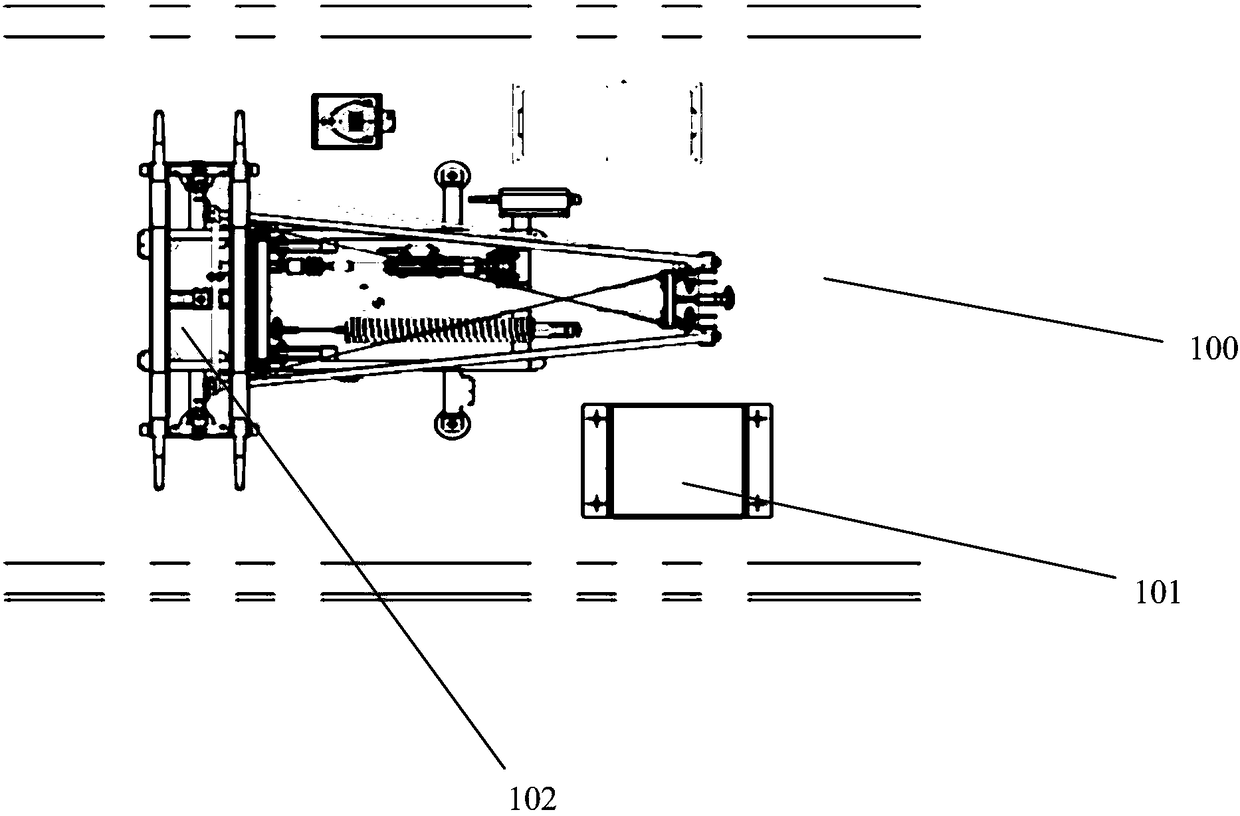

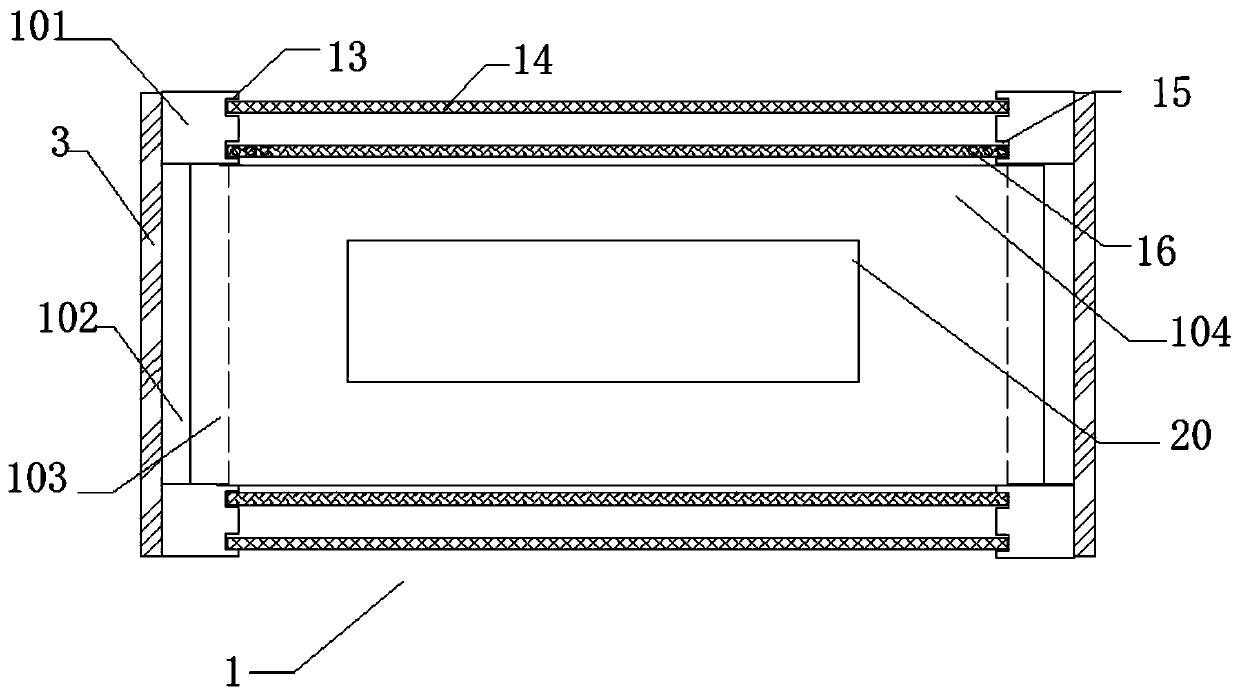

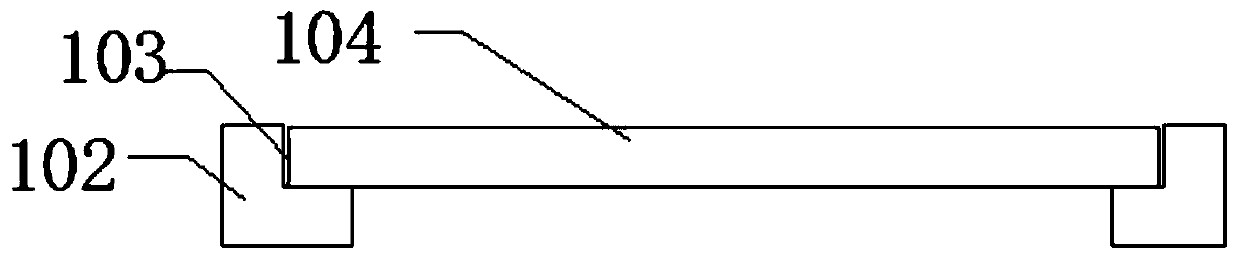

Weighing device for mortar car powder material and its method

InactiveCN100999109AFeed amount controlAccurate collectionSold ingredients supply apparatusControl systemVibration absorption

The present invention discloses a mortar carriage powder material weighing and metering equipment and method. Said equipment adopts two-stage obliquely-arranged first-stage spiral conveyor and second-stage spiral conveyor, on the feeding part of second-stage spiral conveyor a powder material hopper for receiving and temporarily storing dried powder is set, on the powder material hopper and discharging part are set front and rear hanger rod components which are respectively equipped with sensor, in the described front and rear hanger rod components the position connected with weighing sensor and the position connected with second-stage spiral conveyor are respectively equipped with vibration absorptive block for making vibration absorption, and said weighing sensor is electrically connected with upper-position machine. Said invention also provides its working principle and its concrete operation method.

Owner:SANY HEAVY IND CO LTD (CN)

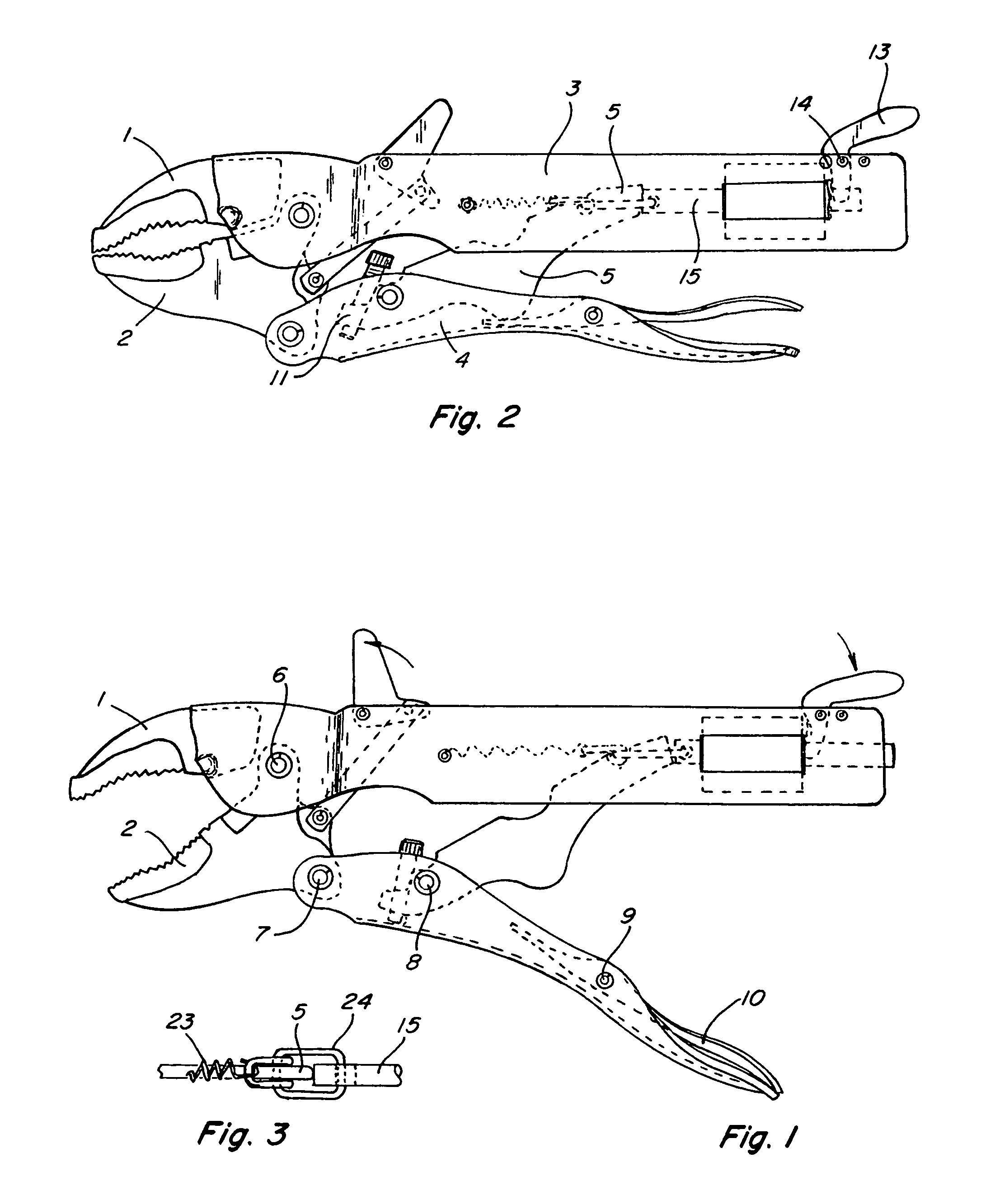

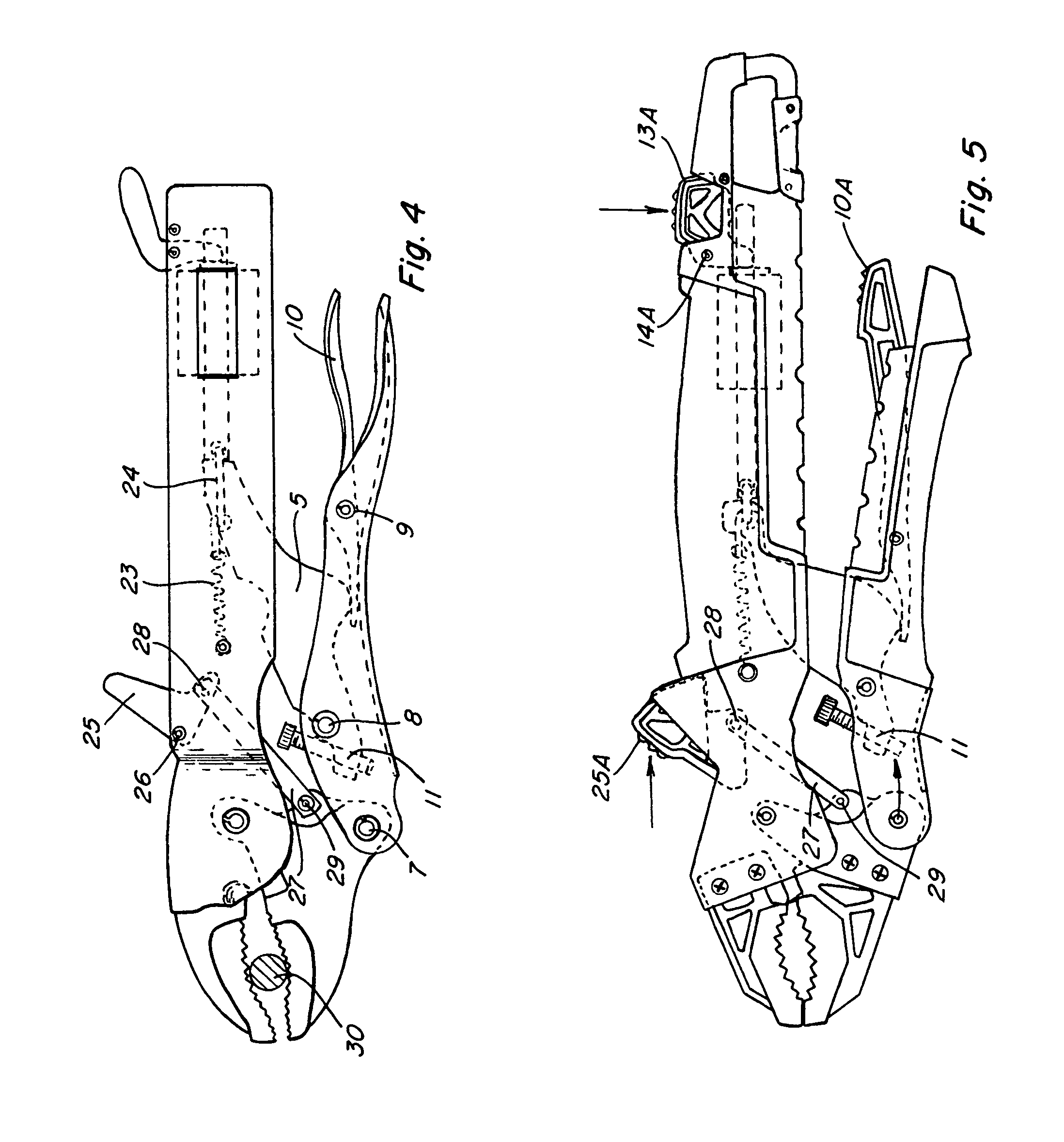

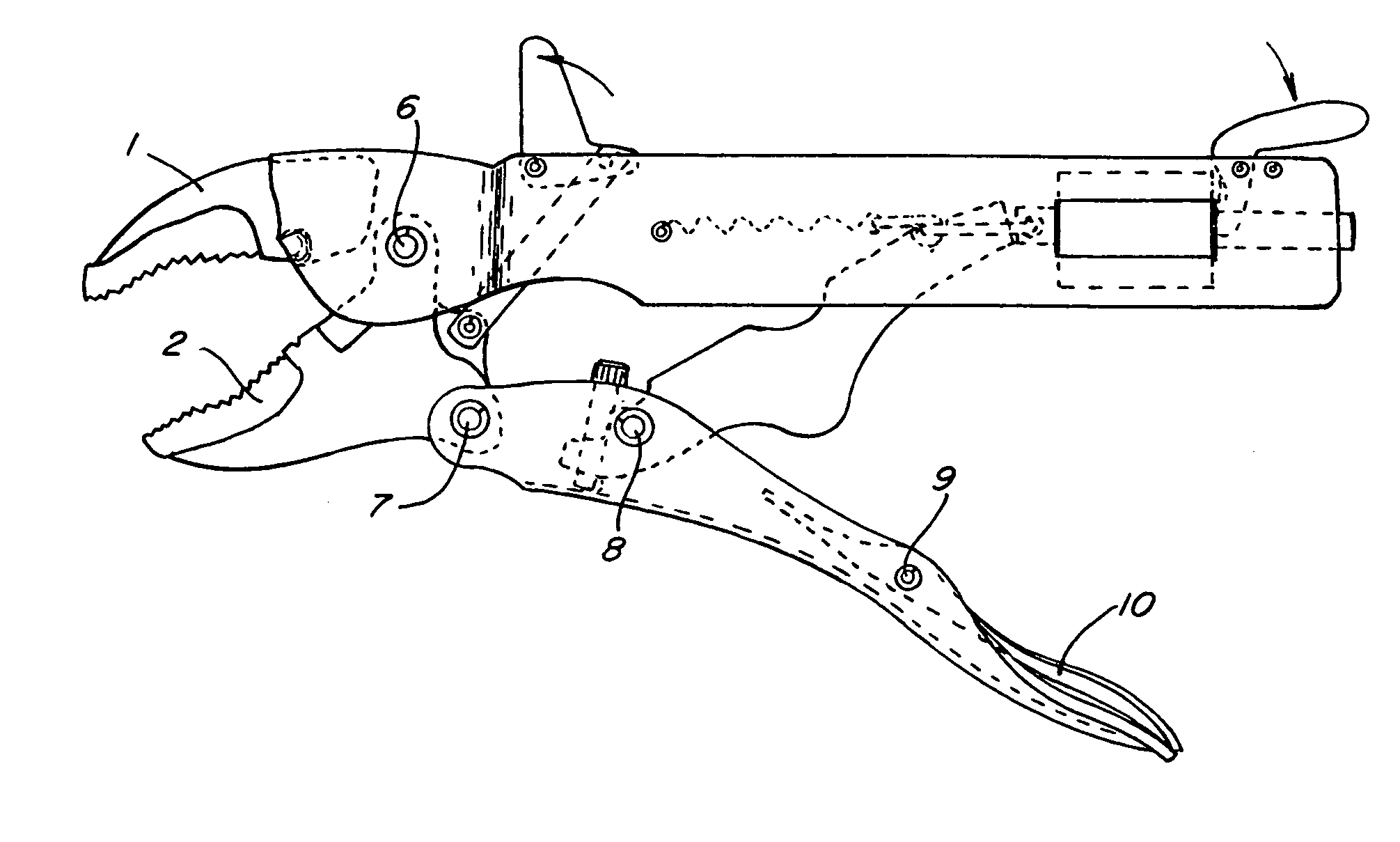

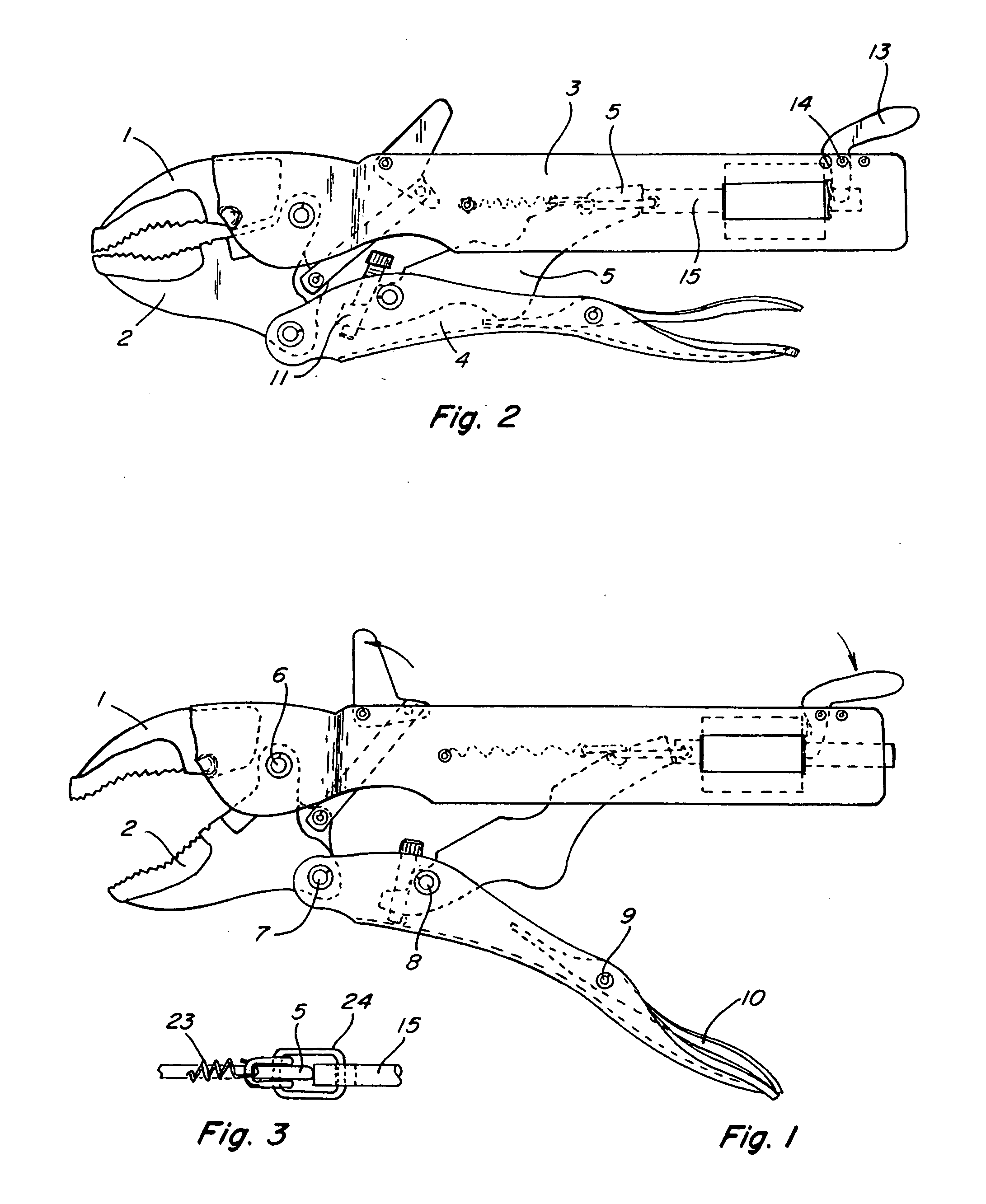

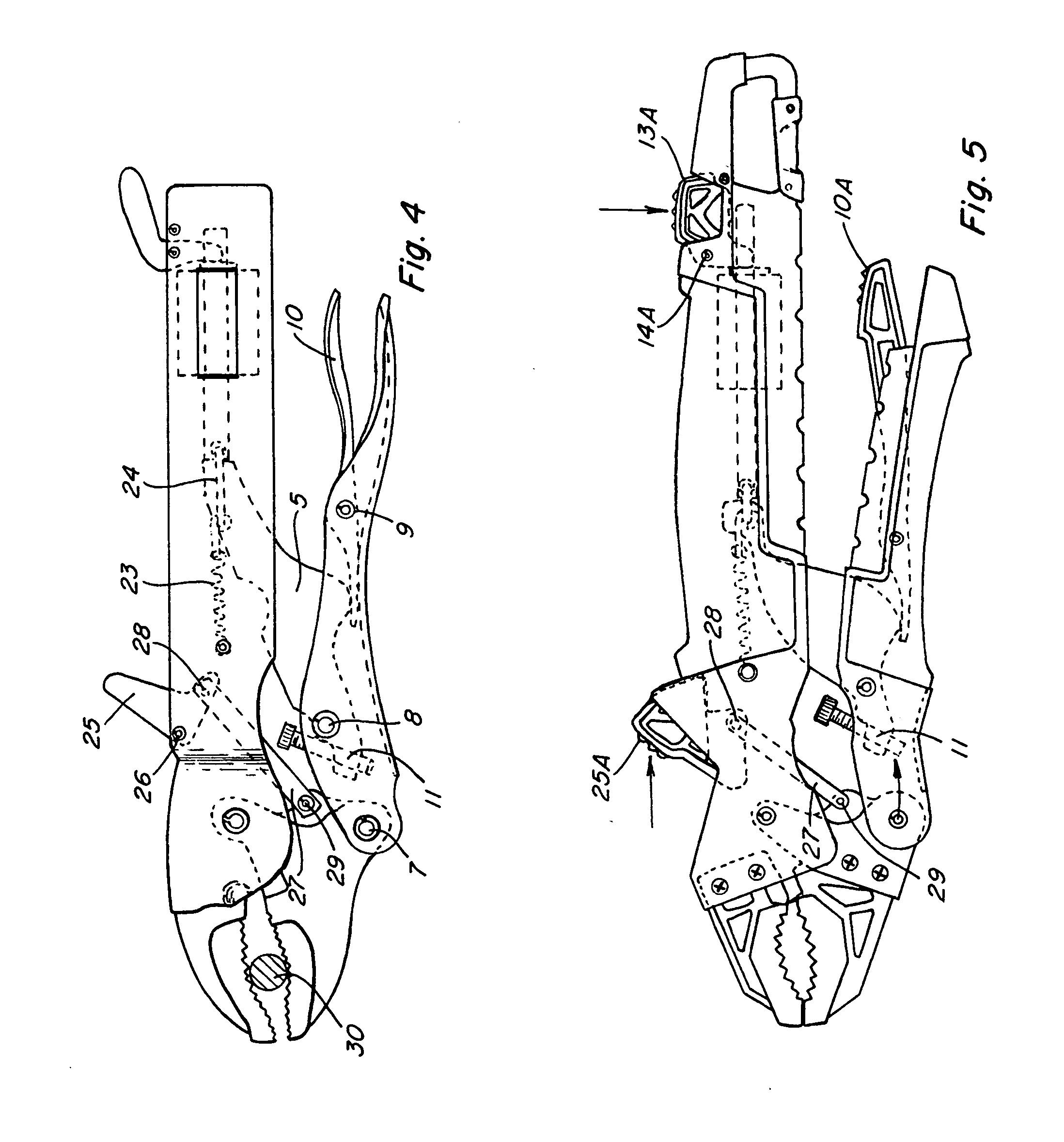

Automatic sizing one-handed locking pliers

An automatically adjustable locking pliers or tool includes a jaw fixed to a first handle and a jaw that pivots about the first handle. The pivoting jaw is connected to a lower tightening handle. A lever connects the tightening handle and first handle. A self-adjusting sizing and locking mechanism includes a thumb jaw sizing piece located near the jaws and movable to open the jaws so that they can be sized around a workpiece. When the thumb jaw sizing piece is released, the jaws automatically size and clamp lightly around the workpiece. The locking mechanism uses balls between a locking rod and a tapered surface. Locking occurs when the balls wedge between the rod and the tapered surface. A release cylinder is connected to a release paddle movable to unlock the mechanism. The sizing piece and locking mechanism are operable to automatically size and lock the pliers or tool.

Owner:HUNTER MARC W

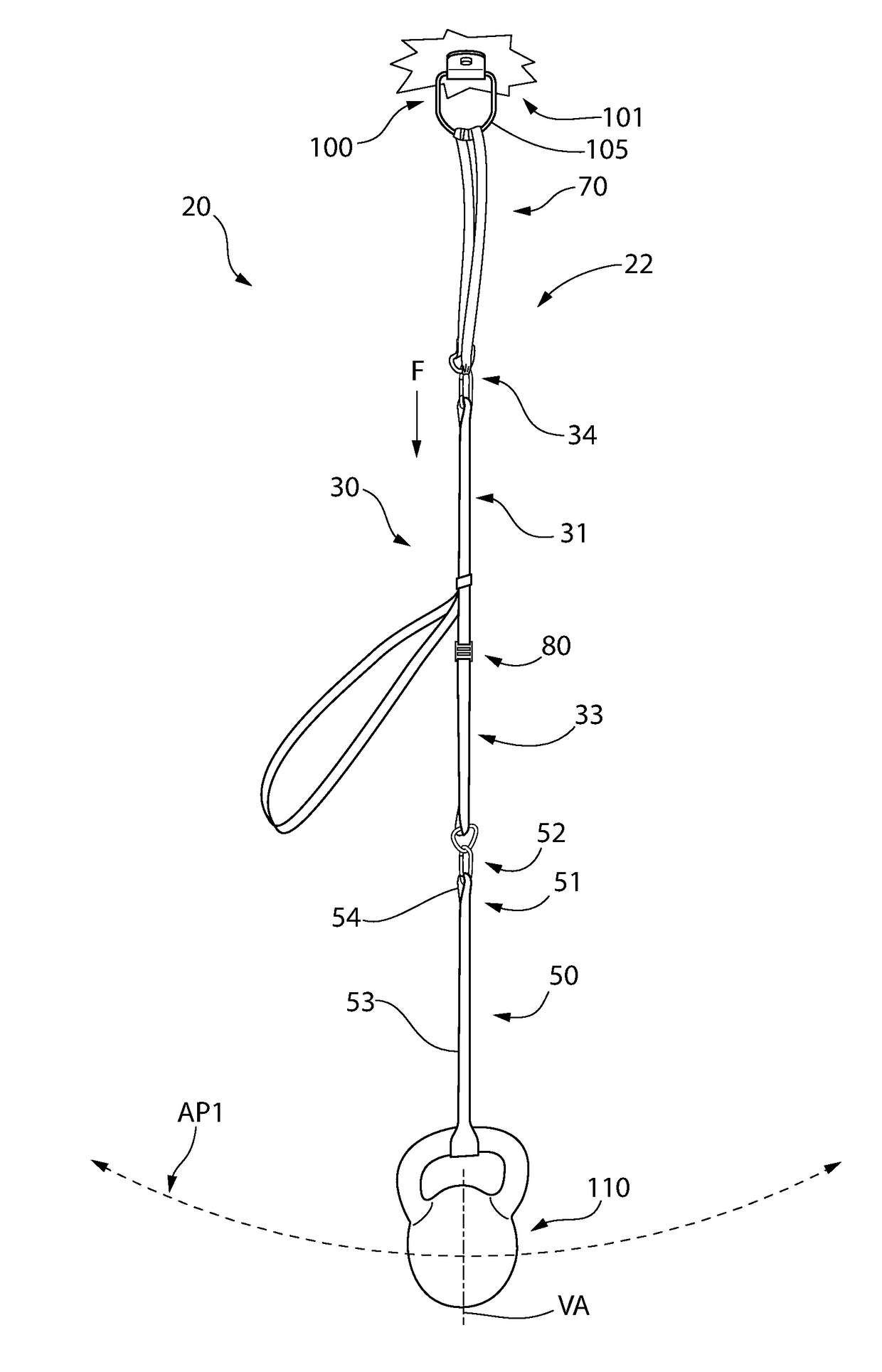

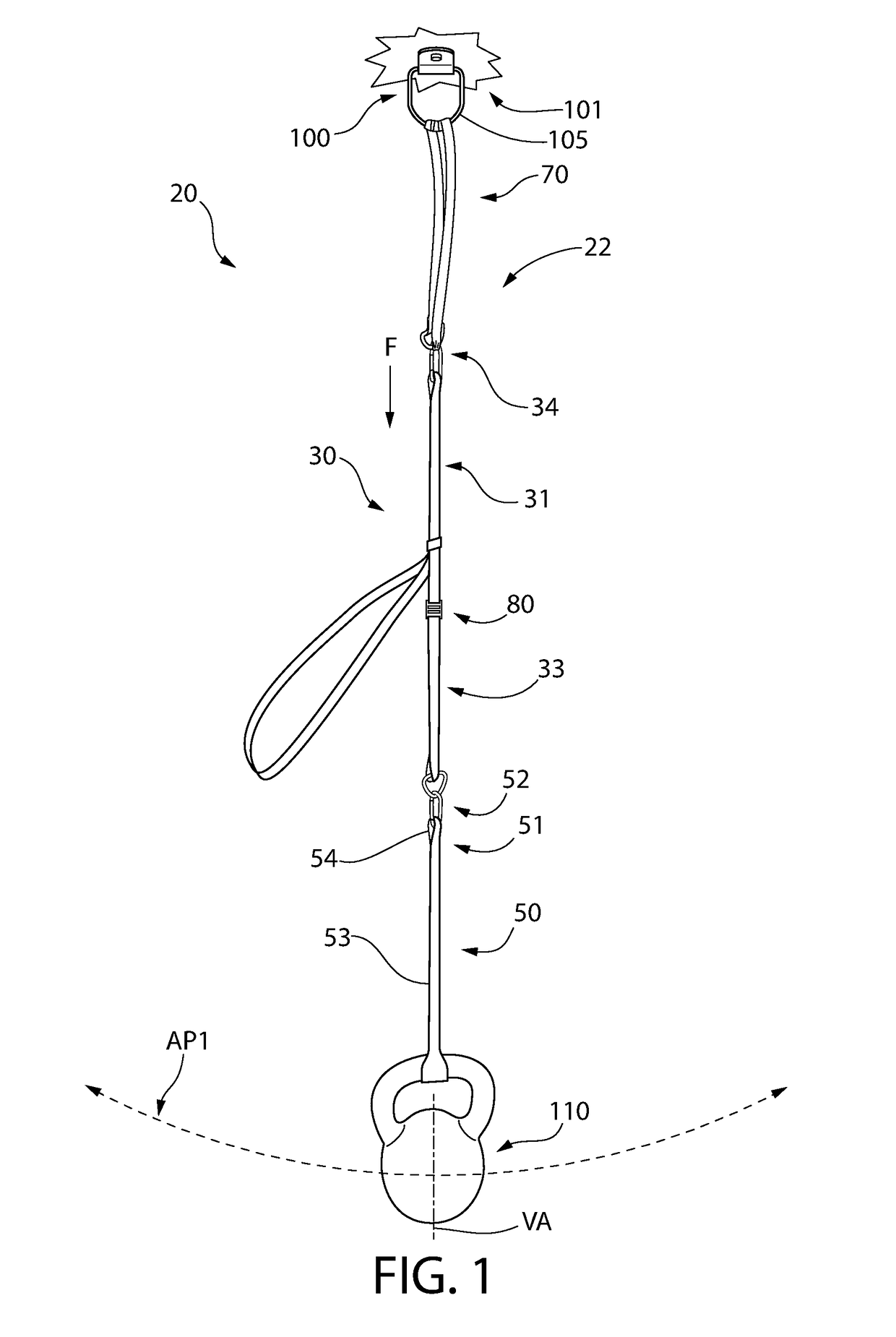

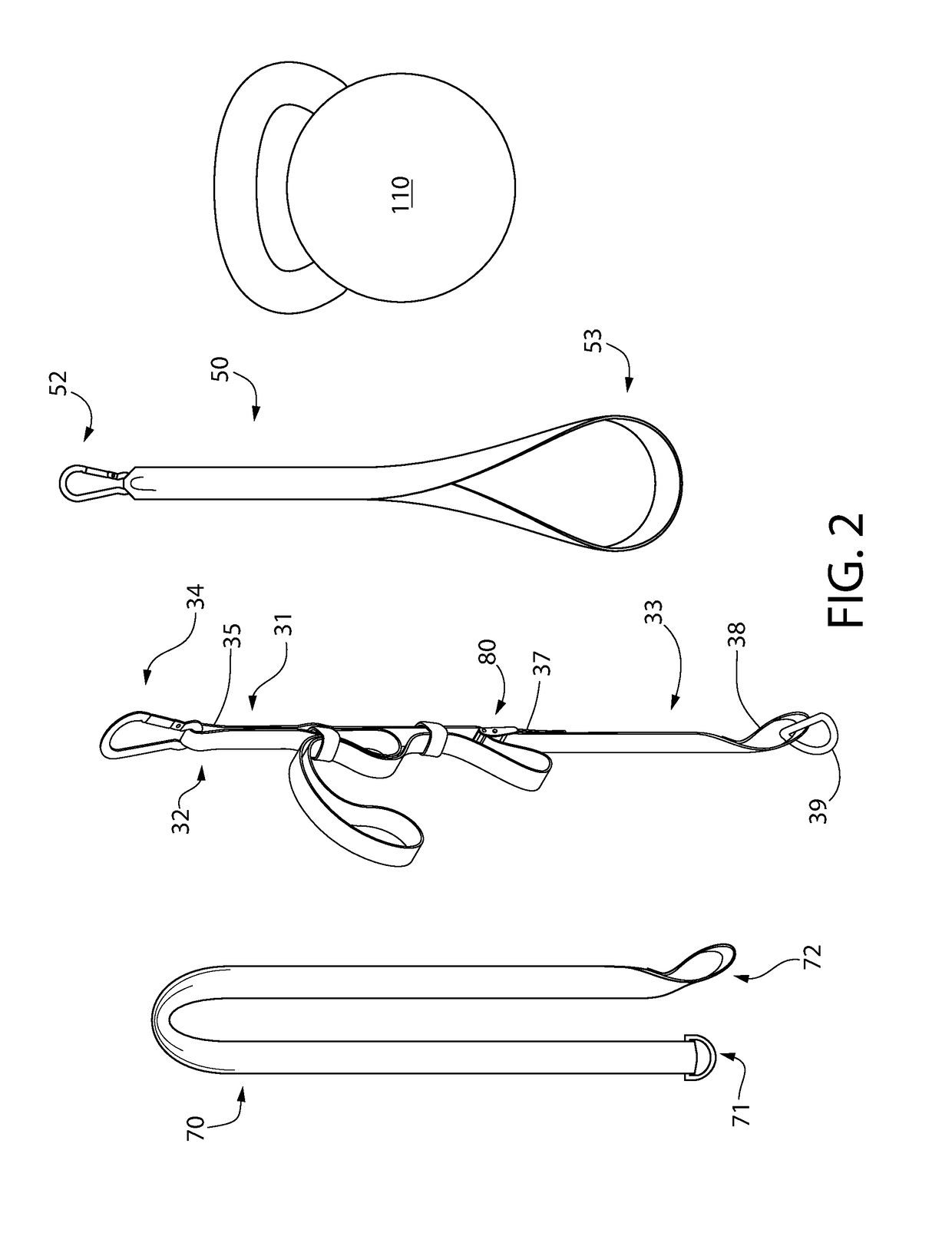

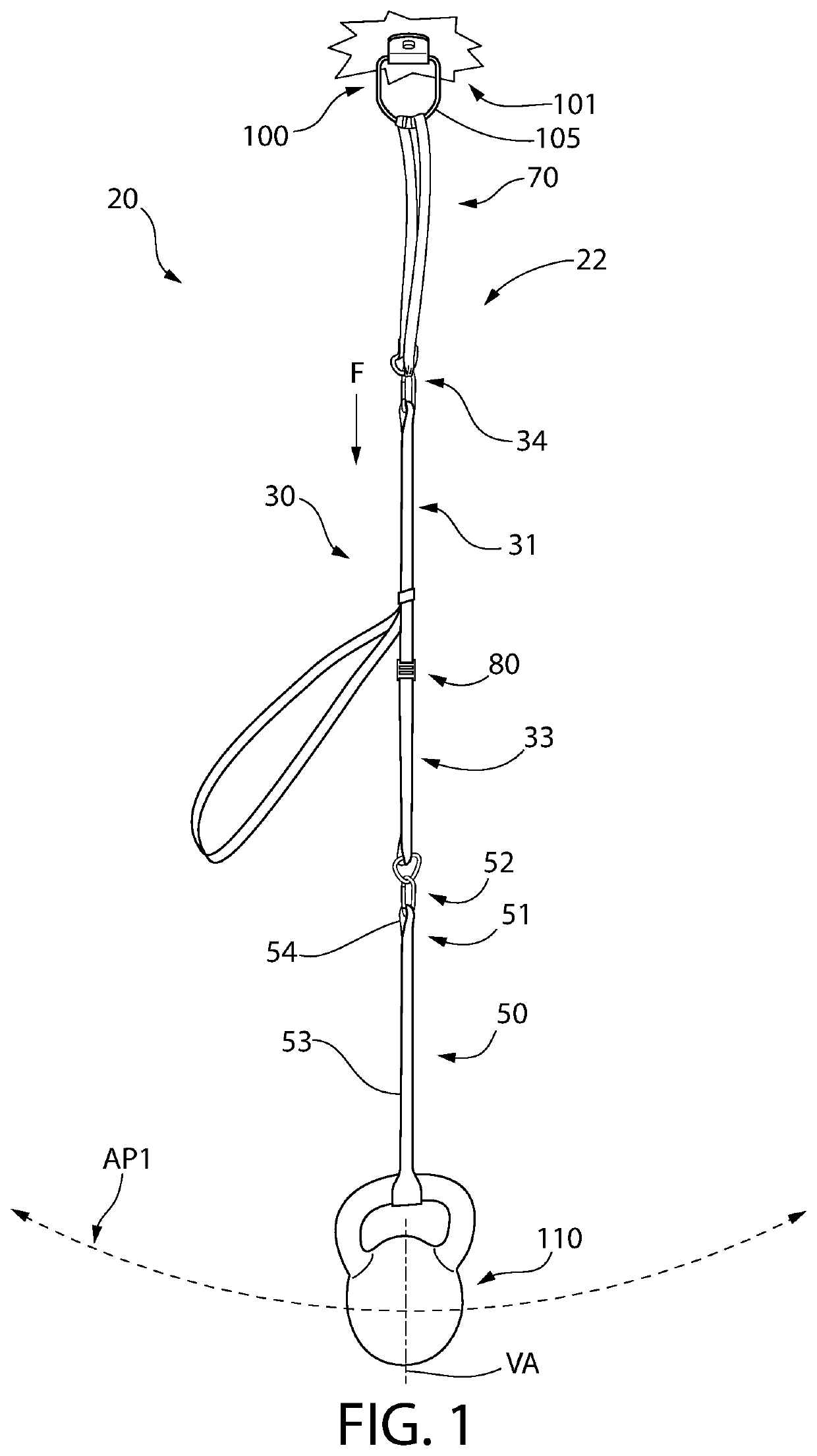

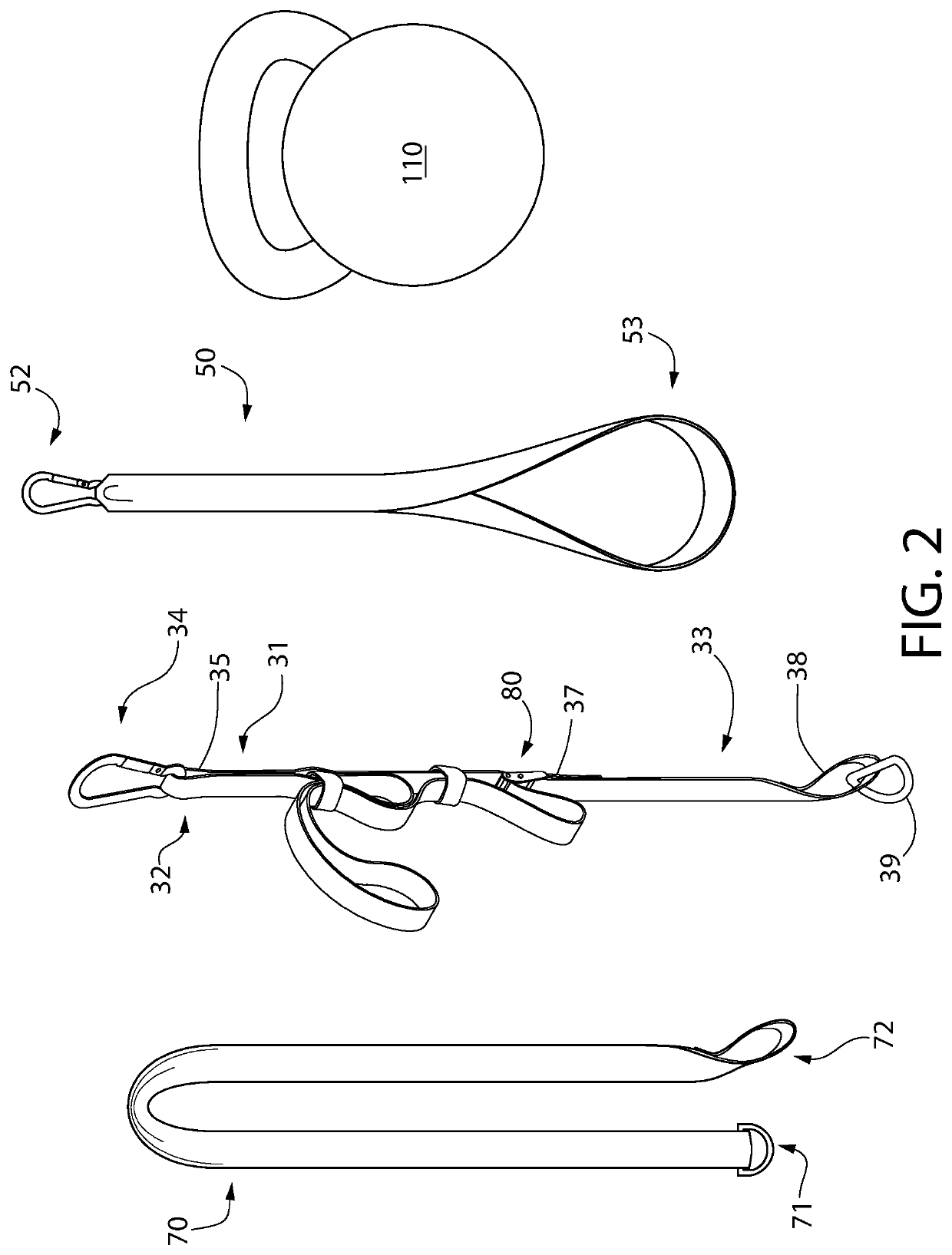

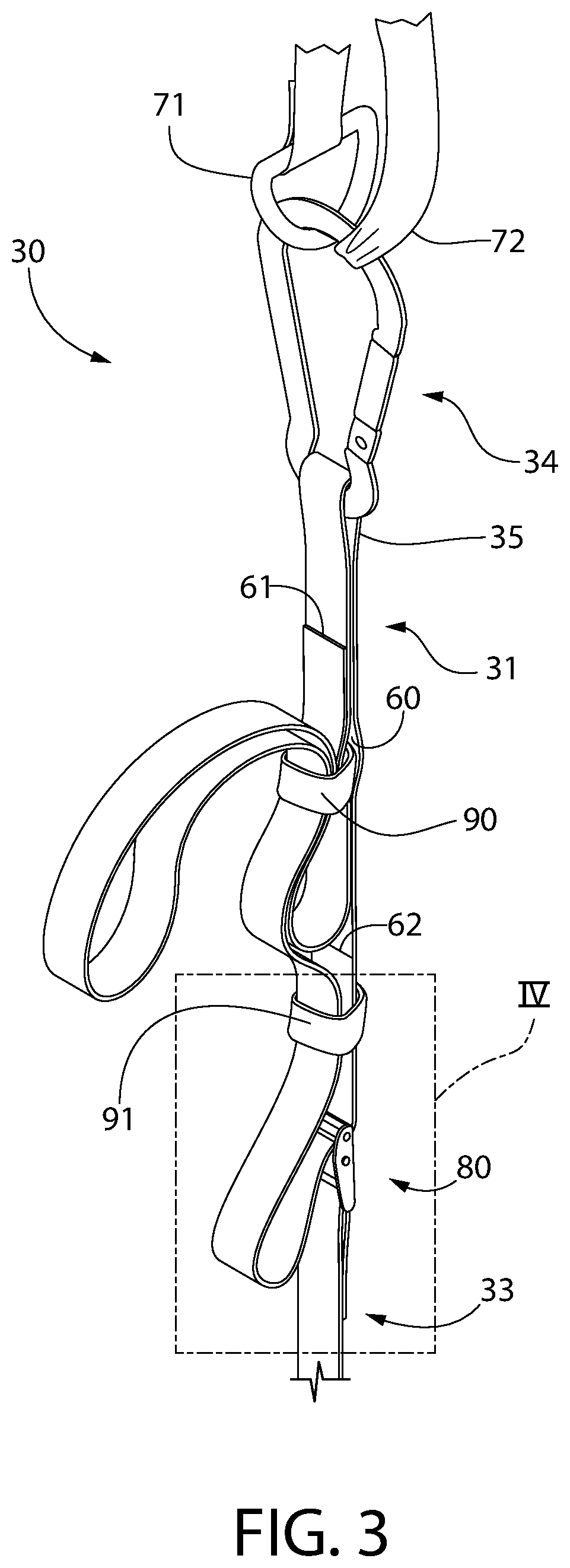

Adjustable exercise suspension system and related methods

ActiveUS20180290007A1Reduce the risk of injuryIncrease or decrease weightDumb-bellsFreely-suspended gymnasticsPull forceEngineering

An adjustable exercise suspension system and related methods of use and exercise are disclosed. The system includes a length-adjustable suspension strap assembly attached at one end to a fixed overhead support structure and at an opposite end to a weight element. The strap assembly comprises a plurality of straps detachably connected together. The weight element is suspended from the overhead support structure creating a tensile force in the strap assembly establishing a taut condition. The weight element is manually movable by a user during the exercise routine along an arcuate path in a plane of stable motion while the tensile force maintains the taut condition of the strap assembly. The strap assembly advantageously provides guided and stabilized motion of the weight element for the user thereby minimizing risk of injury. The resistance force of the system is user-variable by attaching different size weight elements to the strap assembly.

Owner:DV LV LTD

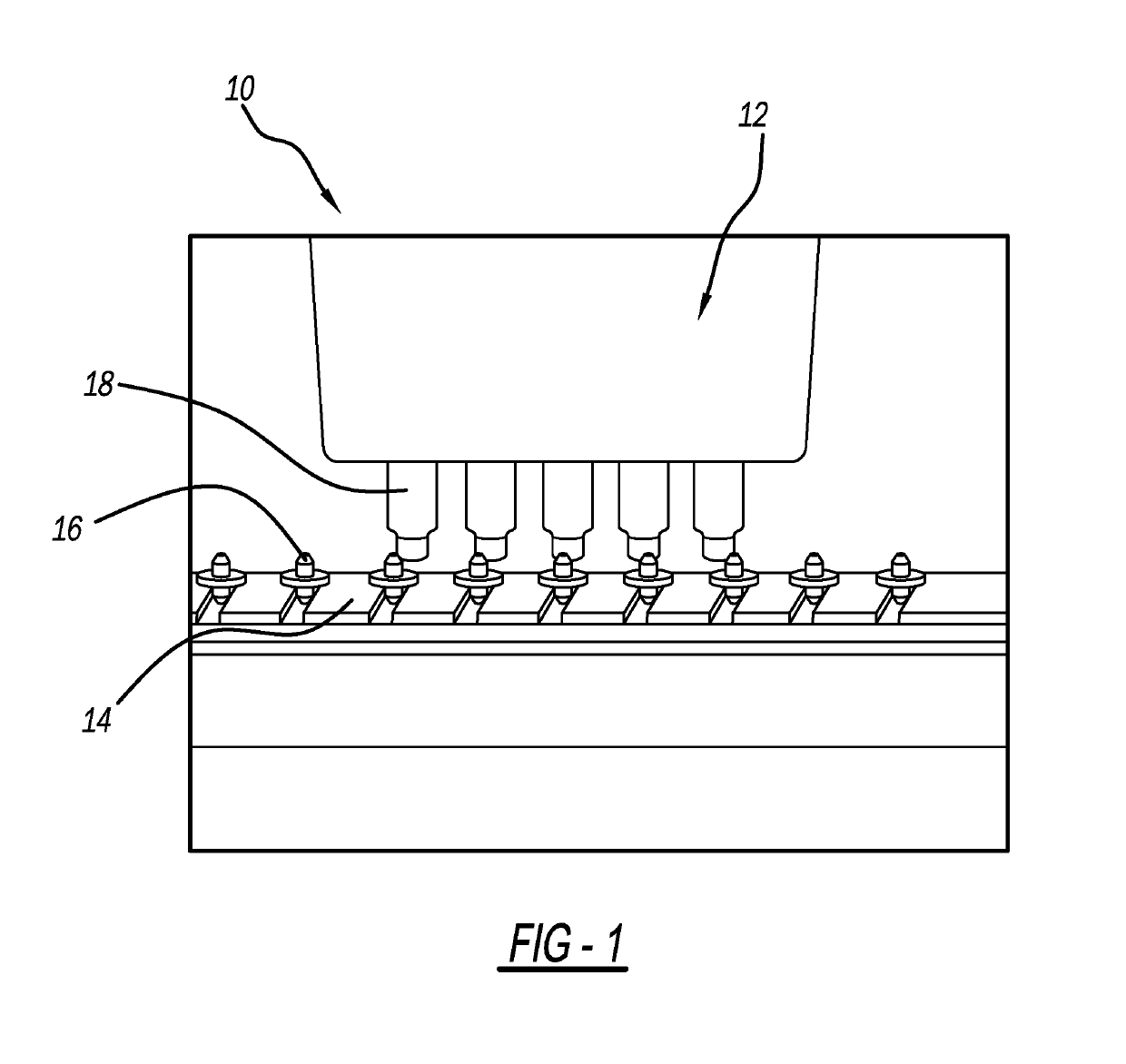

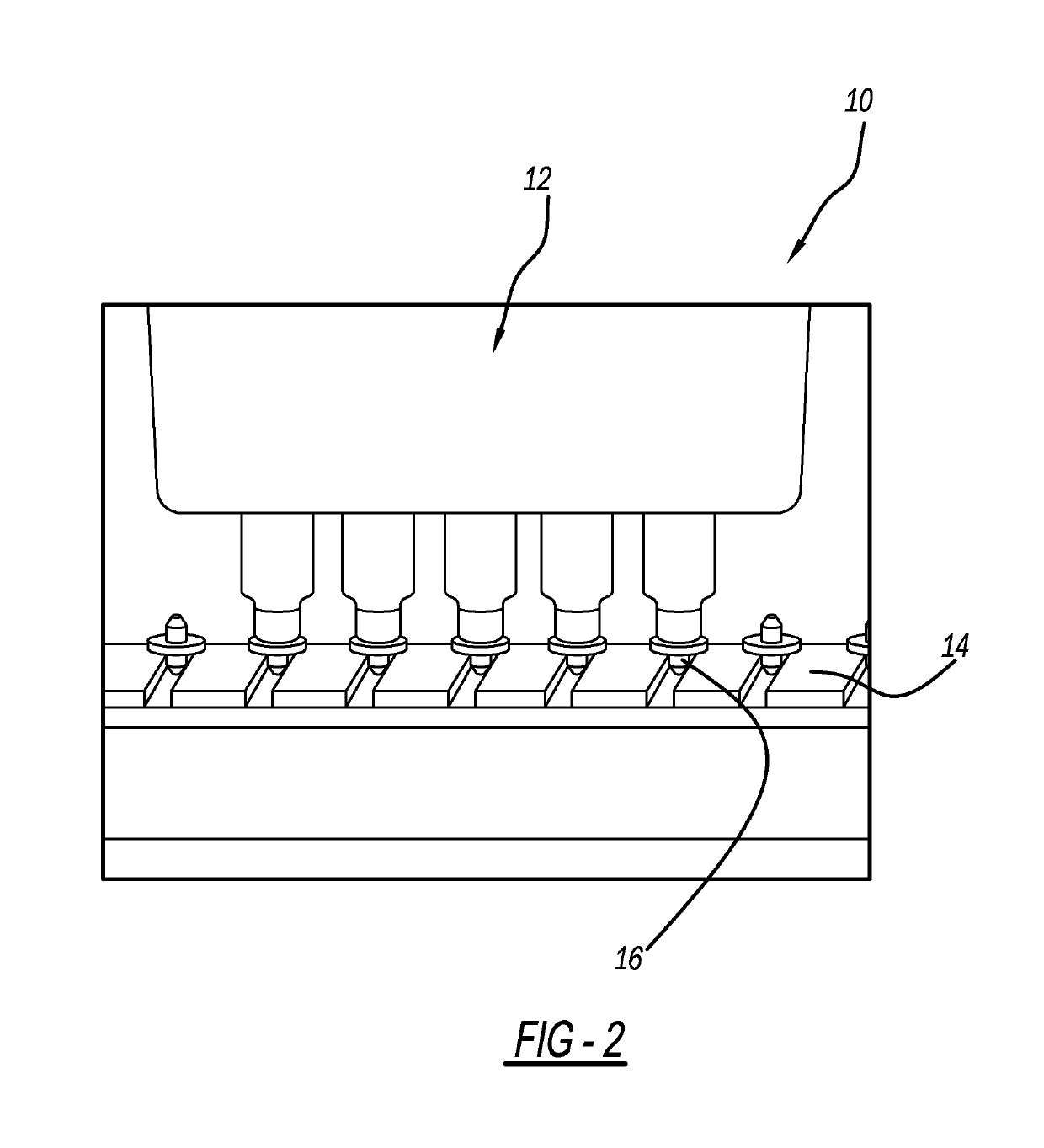

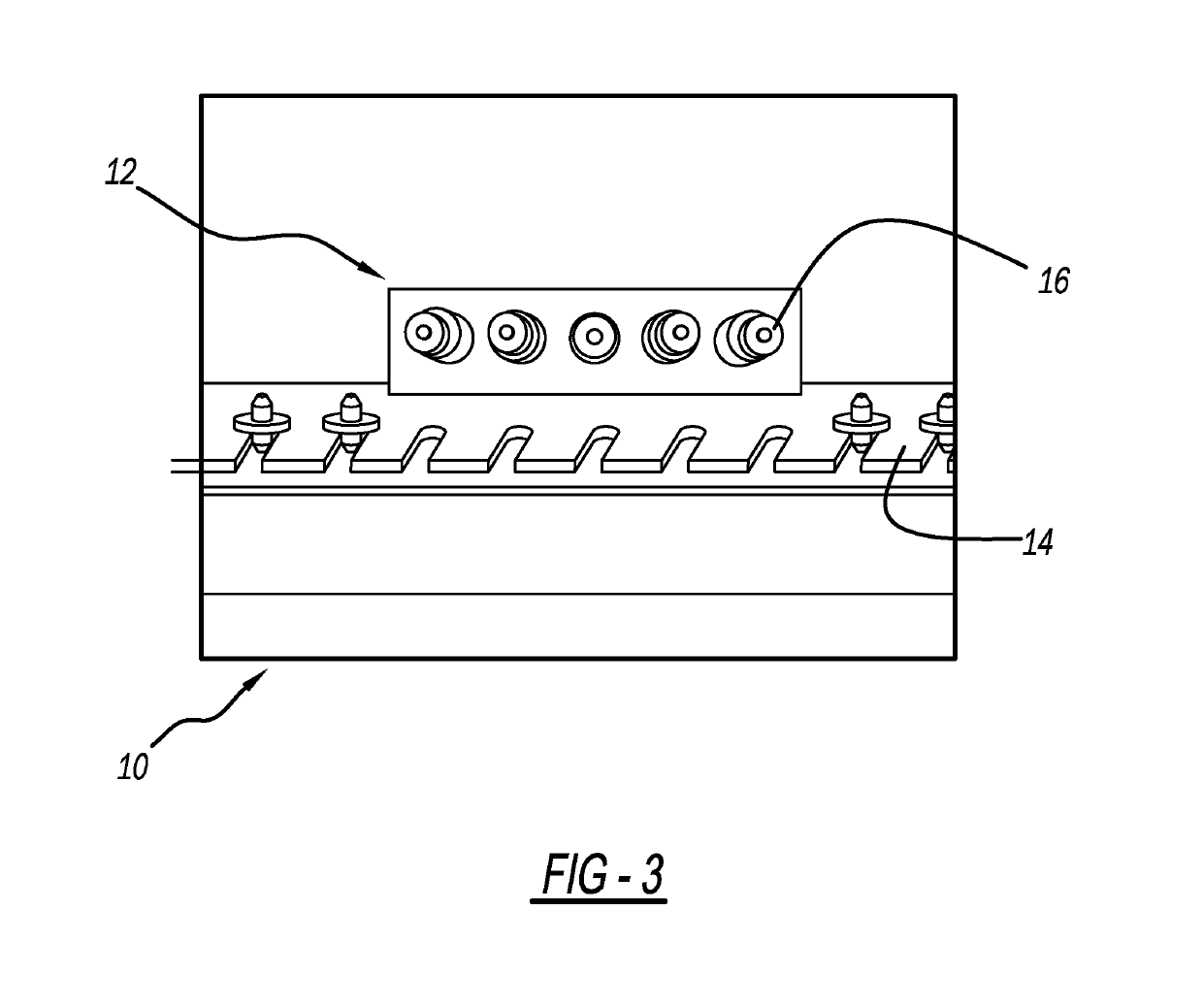

Motor attachment assembly for plastic post isolation system

InactiveUS7893572B2Eliminate dropReduce complexityPump componentsNon-rotating vibration suppressionEngineeringVibration isolation

The invention provides for a motor attachment assembly that includes an electric motor having spring clips adapted to securely lock onto the isolation posts of a plastic post vibration isolation system. The motor includes an end cap that has notches which cooperate with locator tabs of the motor housing to lock the cap onto the housing with the spring clips therebetween. Each clip includes an axial slot that is expandable in an open direction to receive an isolation post and biased in the closed direction to retain the isolation post. Each clip also has an inner surface with barbs protruding into the channel to allow insertion of the isolation post into the channel in the direction of the output shaft and to resist movement of the isolation post in a direction opposite to the output shaft. The inner surface has a retention groove to receive plastically deformed portions of the isolation post.

Owner:MAHLE INT GMBH

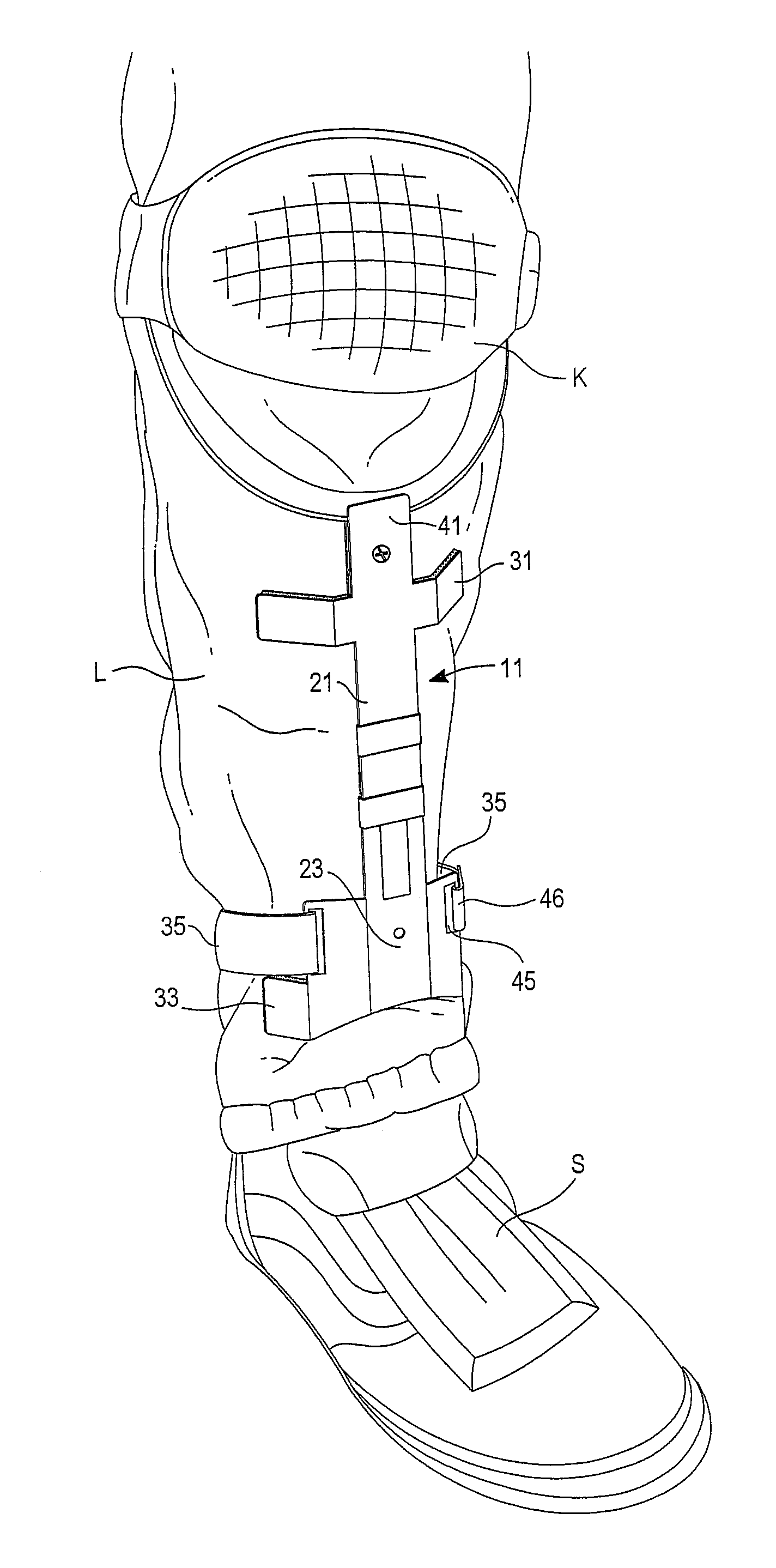

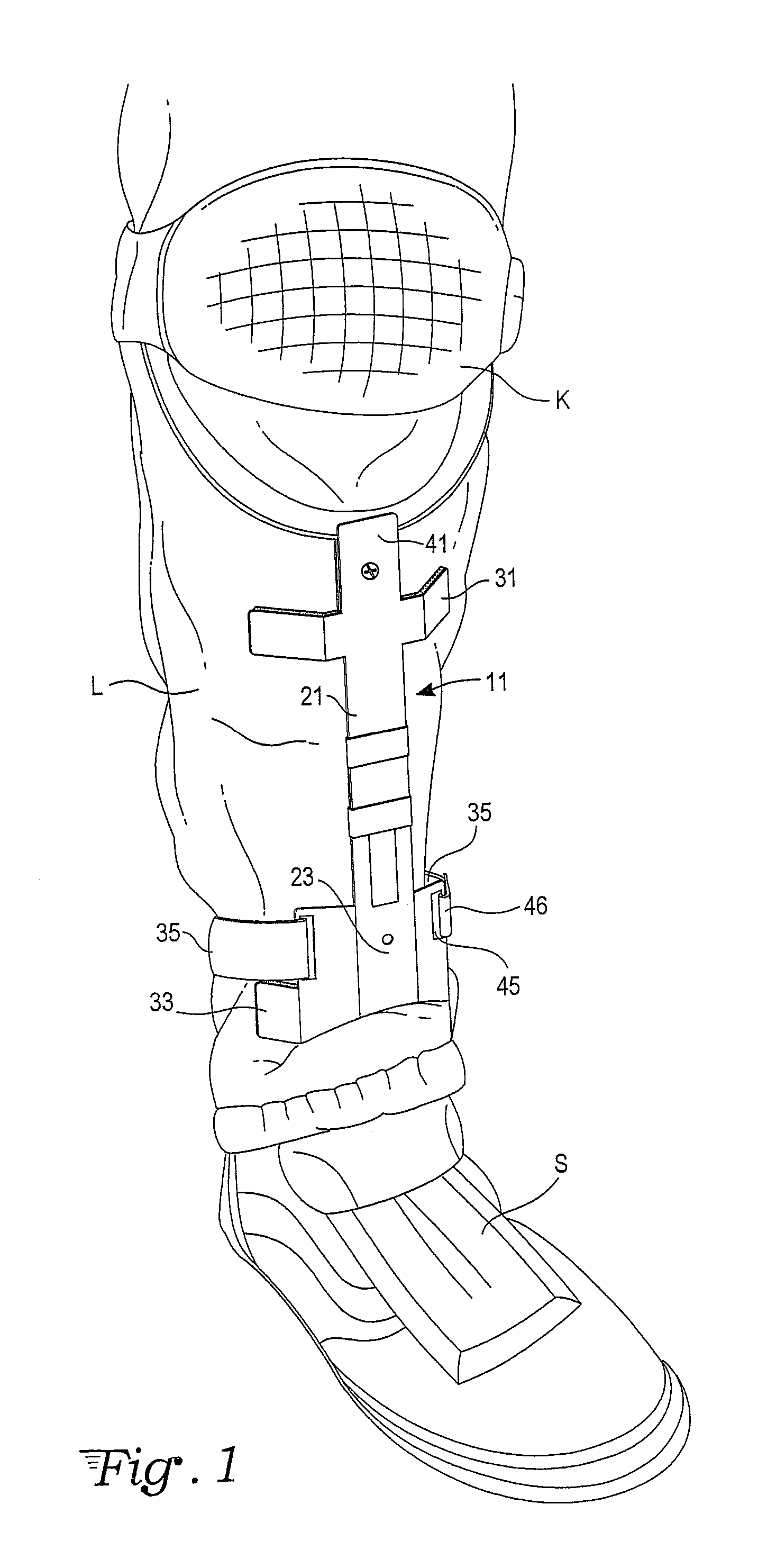

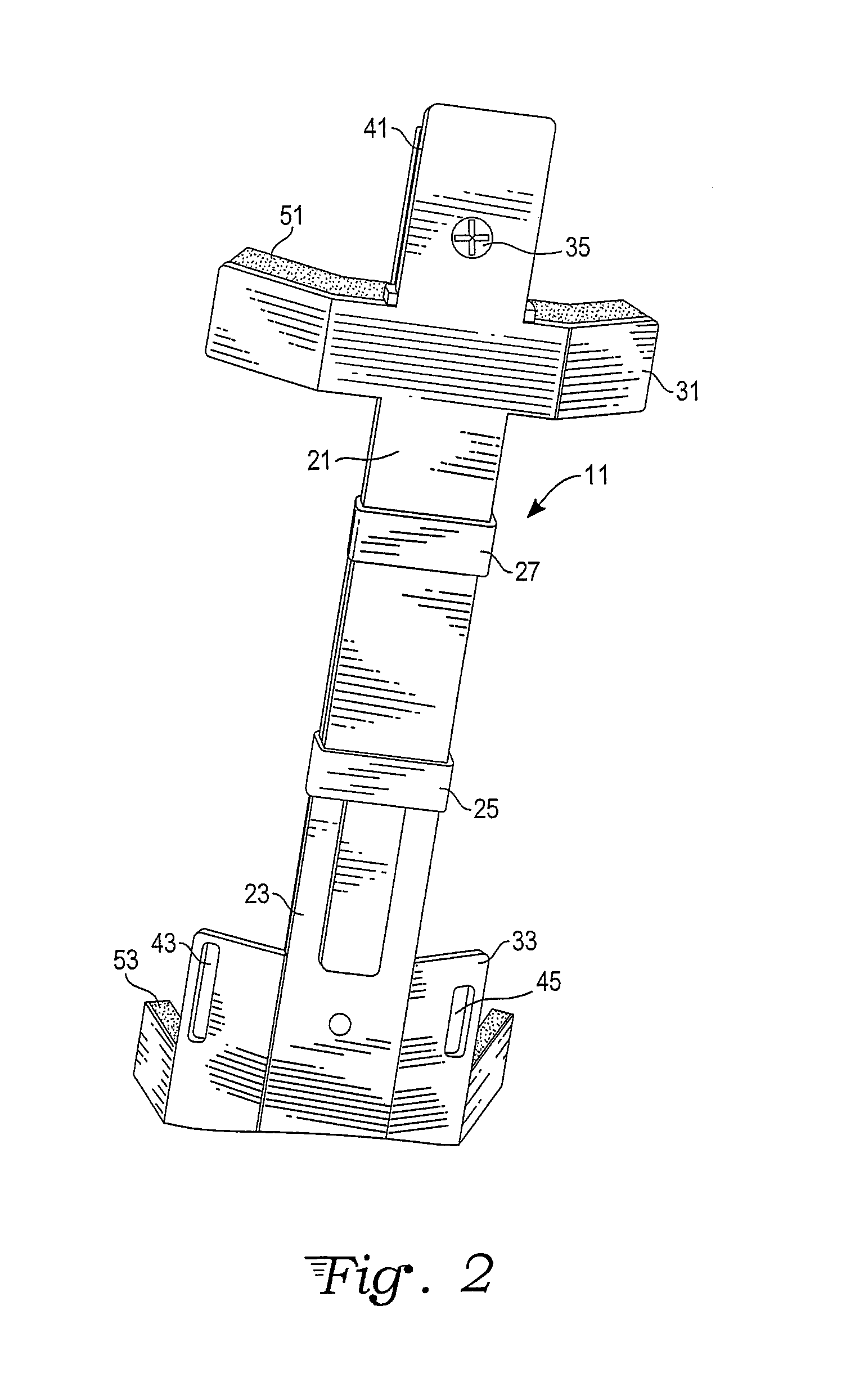

Positioning brace for a kneepad

ActiveUS8752214B1Eliminates dropEliminate dropProtective garmentFixed positionElectrical and Electronics engineering

An adjustable kneepad support that is a brace formed by a pair of elongated, flexible, overlapping thin beam members that are movable relative to each other for lengthwise adjustment. Flexing of the beam members allows operation of a flex-latch that can release a fixed position of the beam members to allow sliding of the members to a newly adjusted lengthwise position.

Owner:MALDONADO MIGUEL

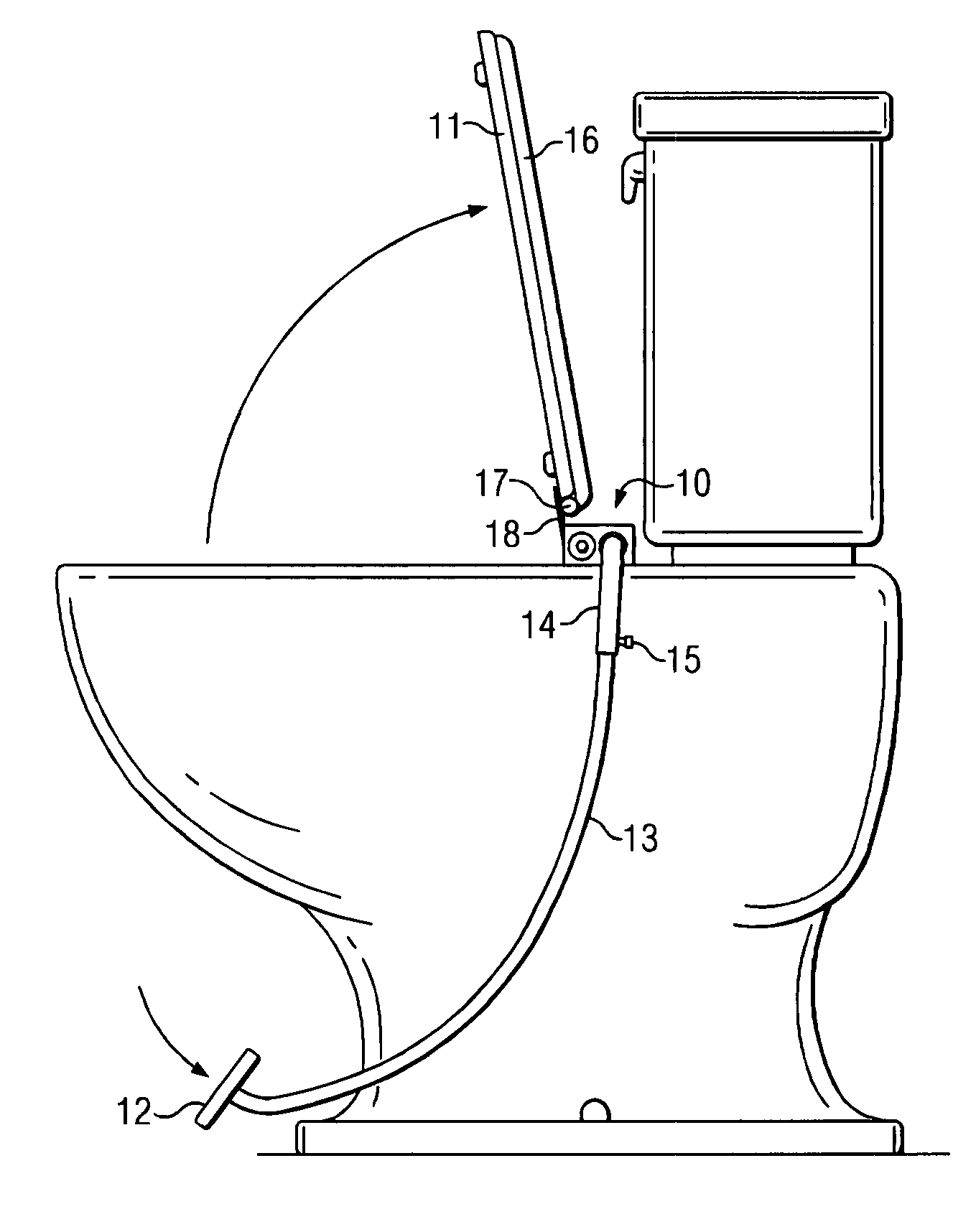

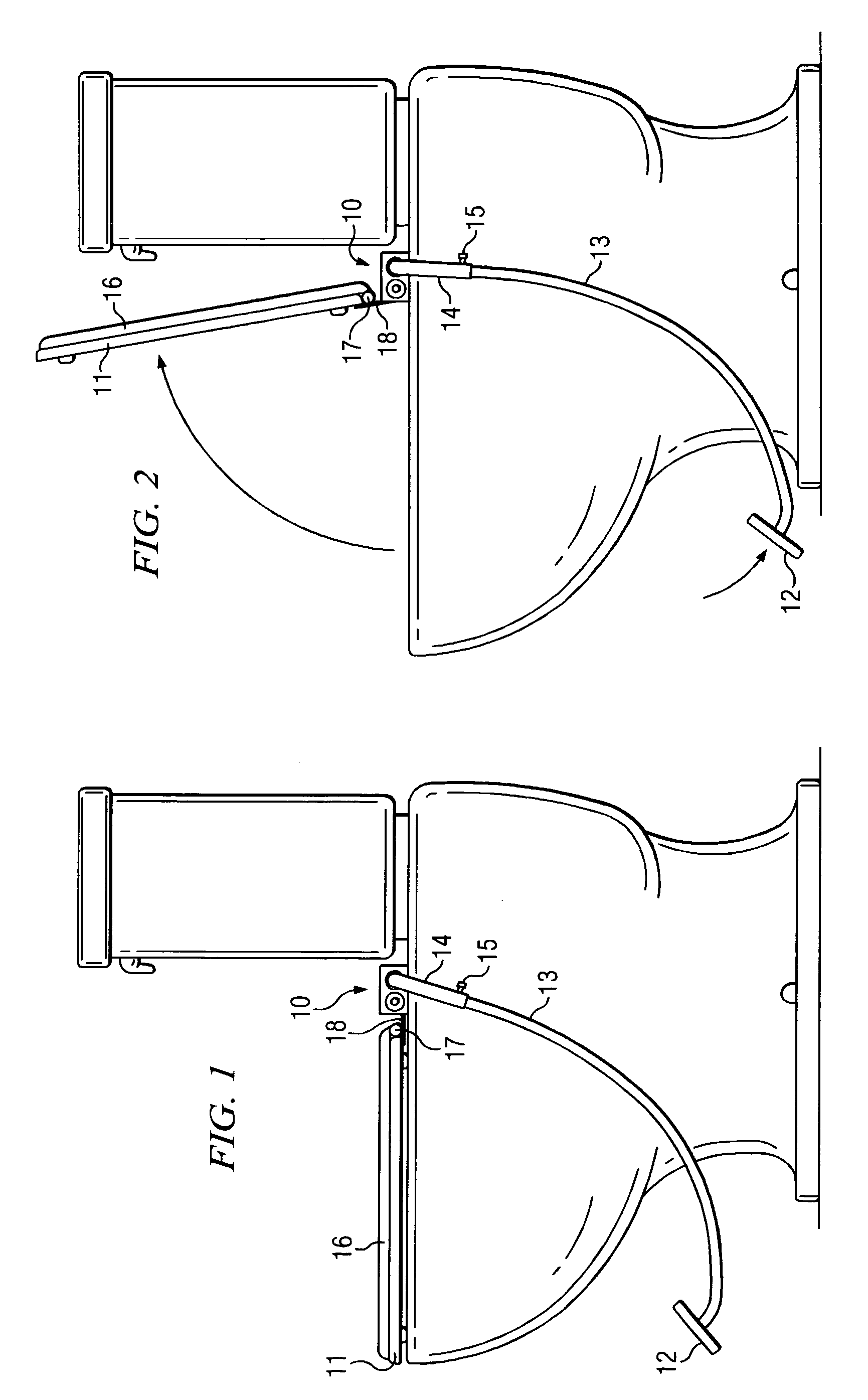

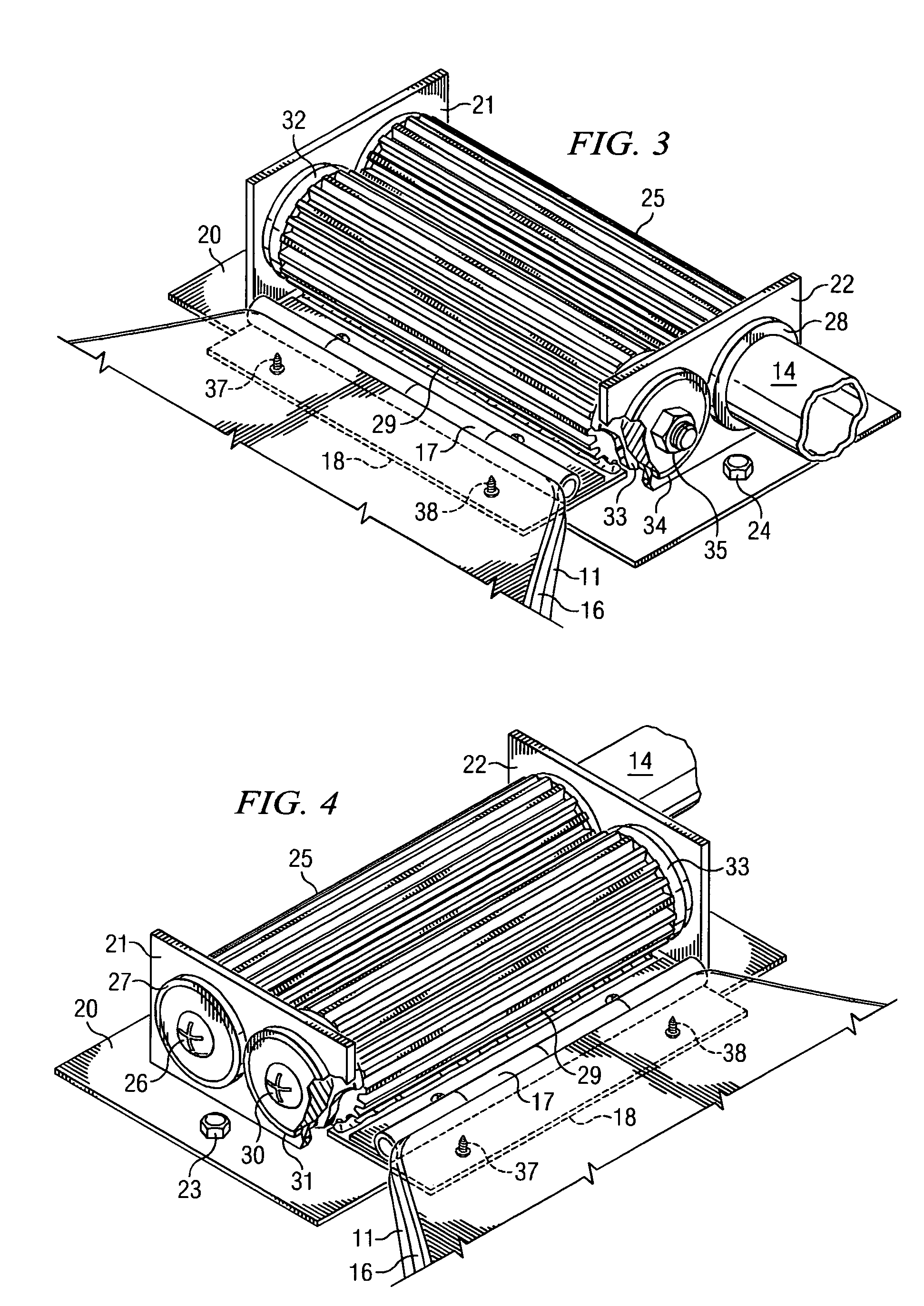

Foot-operated toilet seat

A mechanism for raising a toilet seat includes two geared shafts that are cooperatively engaged while mounted on a toilet. A foot-operated lever attached to a first of the geared shafts provides torque thereto, causing a rotation of the first geared shaft upon depressing the lever. This, in turn, causes a rotation of the second of the geared shafts. The second geared shaft includes a metal flange or other connector that secures a toilet seat thereto over the bowl of the toilet. As the two geared shafts rotate, the toilet seat raises and lowers with the movement of the metal flange on the second geared shaft.

Owner:STEWART STEVE

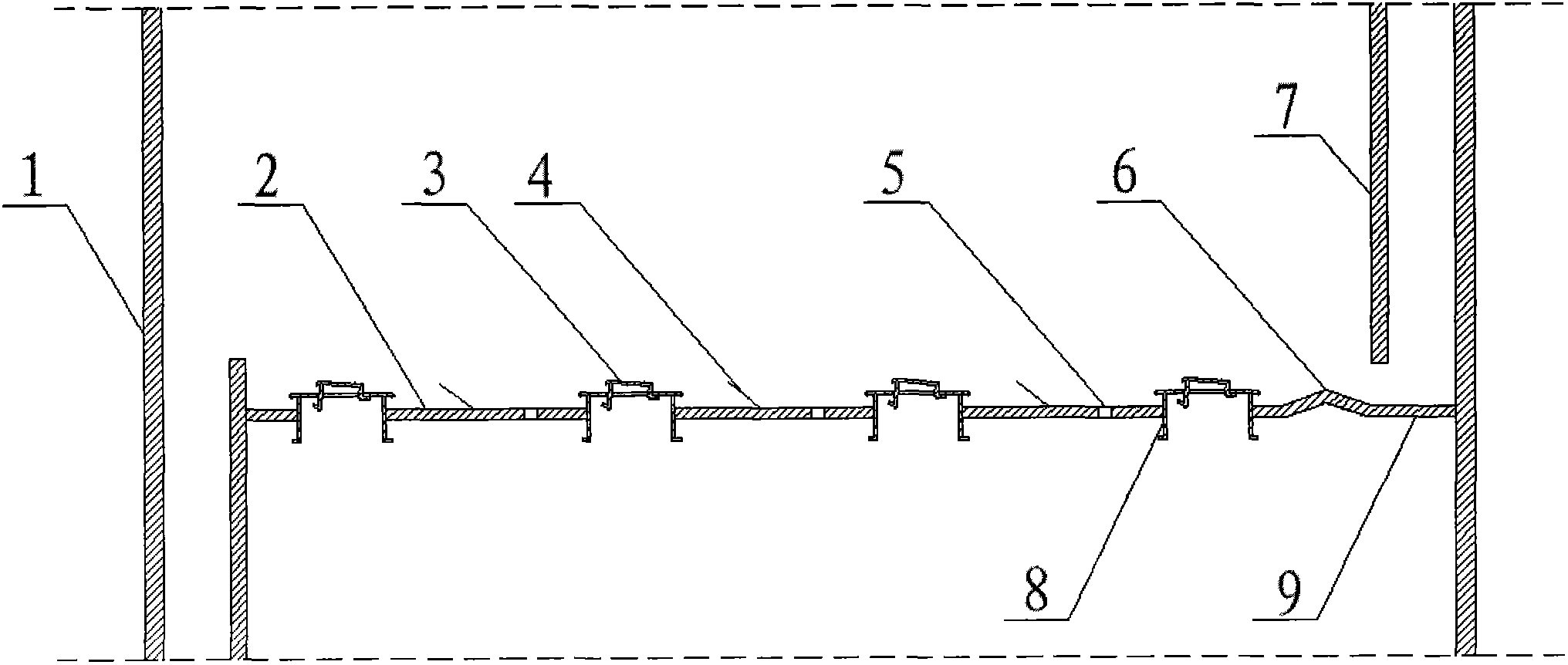

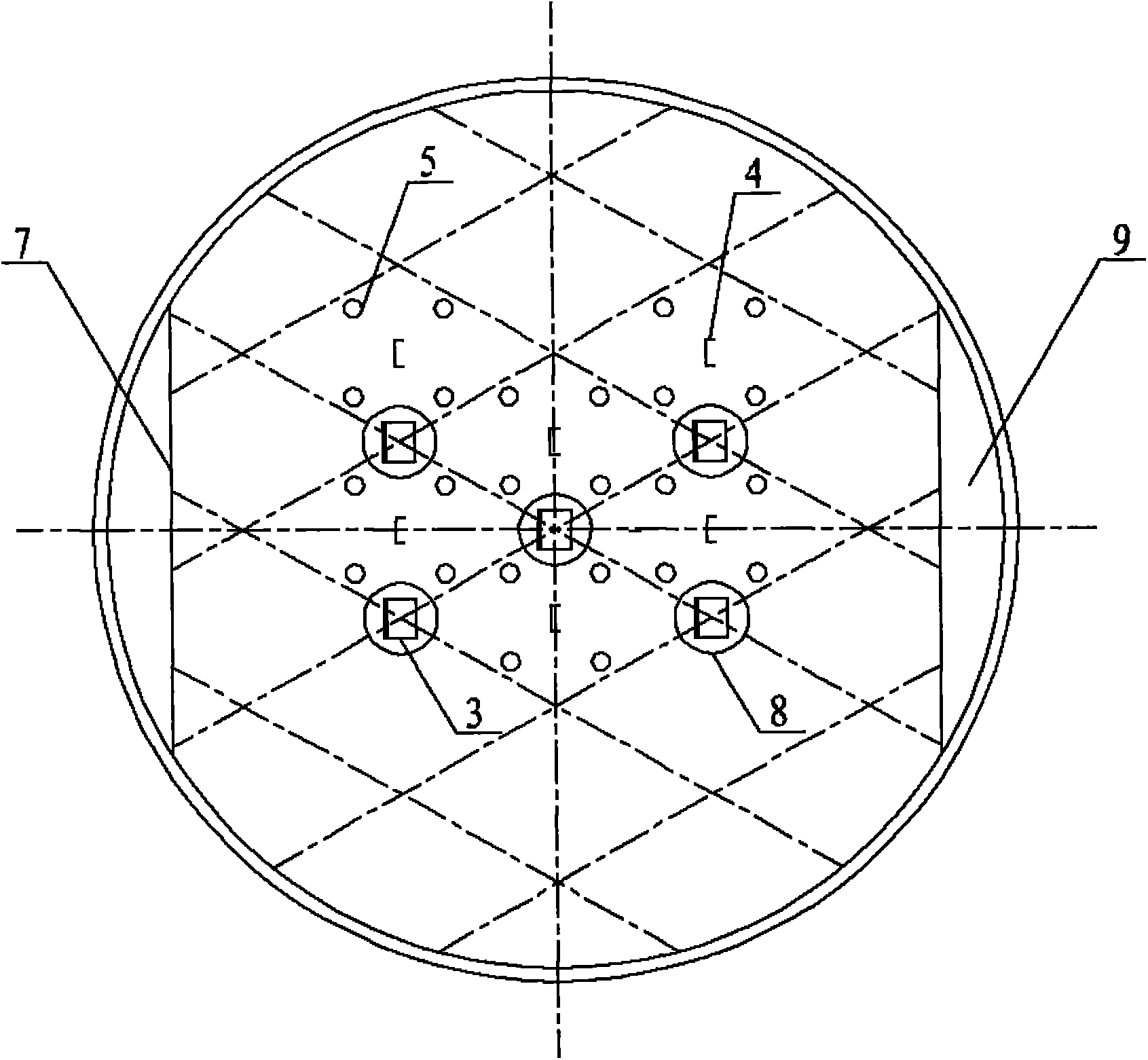

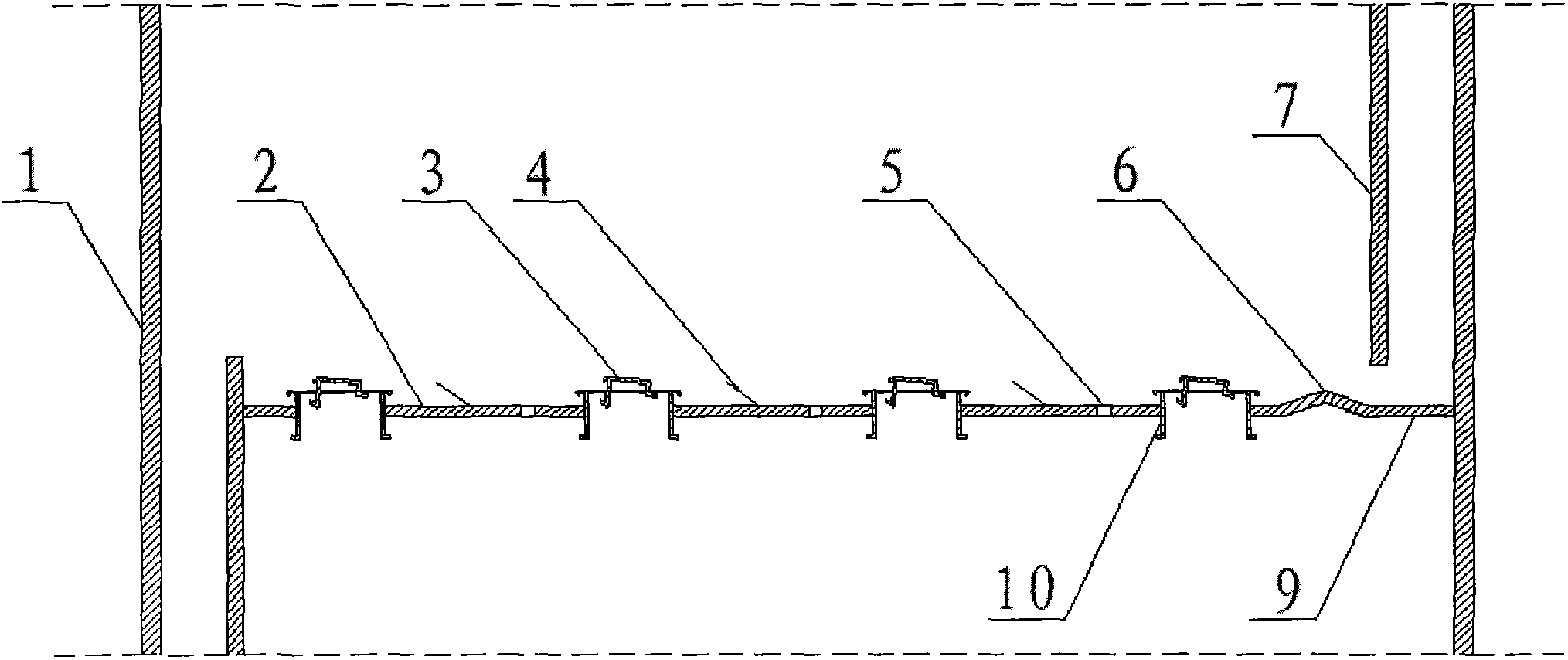

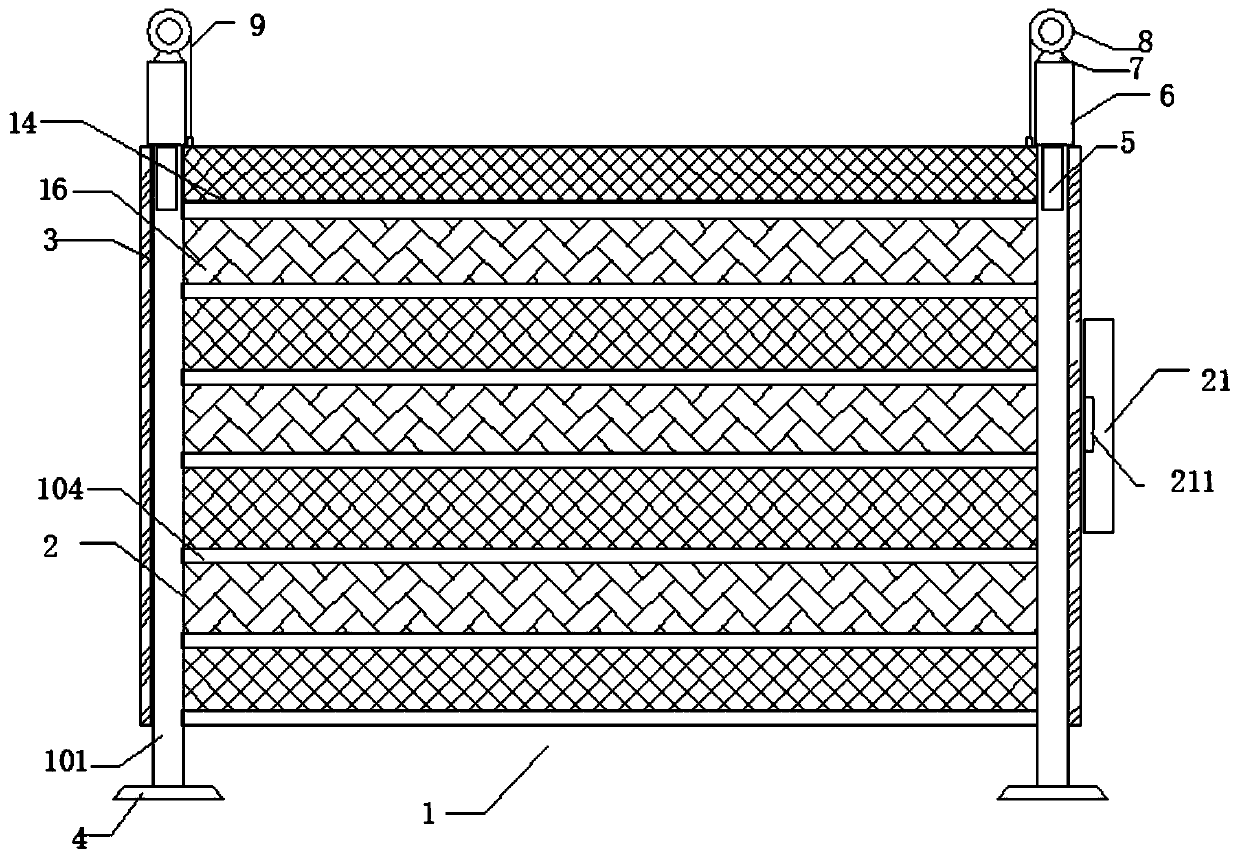

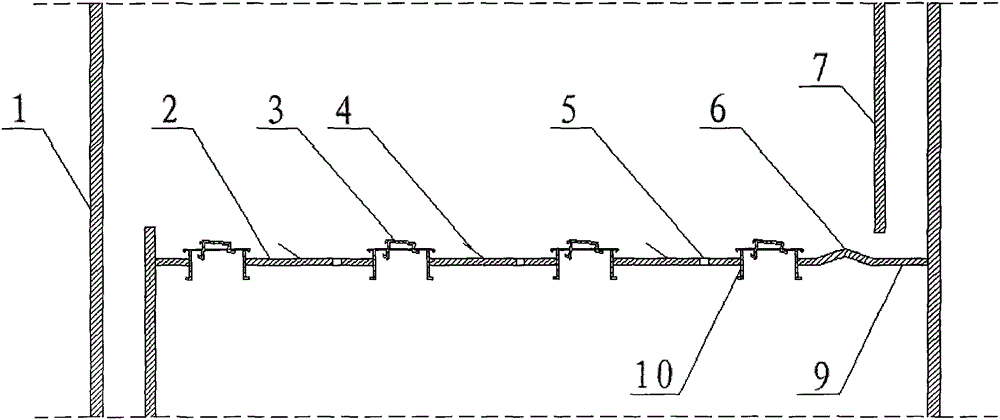

Guiding sieve plate float valve tower

The invention relates to a guiding sieve plate float valve tower, belonging to a gas-liquid mass-transfer separation plant in chemical process. The guiding sieve plate float valve tower disclosed herein mainly comprises a tower body (1), a tower plate (2), a down-flow plate (7), a seal pan (9), etc., wherein the liquid inlet of the tower plate (2) is provided with a bubbling promoter (6), the plate surface of the tower plate is provided with a floating tongue (3), a guiding pore (4), a sieve pore (5) and a float valve. According to the invention, when the gas velocity is low, the float valve on the tower plate is not open, gas only passes through the guiding pore (4), the sieve pore (5) and the floating tongue (3); when the gas velocity increases to a certain level, the float valve is open, and the opening height of the float valve increases gradually with the increase of the gas velocity. The guiding sieve plate float valve tower disclosed herein has the advantages of simple structure, low cost, and greatly raised operation flexibility and separation efficiency.

Owner:河北化大科技有限公司

Adjustable exercise suspension system and related methods

ActiveUS10675501B2Reduce the risk of injuryIncrease or decrease weightDumb-bellsFreely-suspended gymnasticsPhysical medicine and rehabilitationEngineering

An adjustable exercise suspension system and related methods of use and exercise are disclosed. The system includes a length-adjustable suspension strap assembly attached at one end to a fixed overhead support structure and at an opposite end to a weight element. The strap assembly comprises a plurality of straps detachably connected together. The weight element is suspended from the overhead support structure creating a tensile force in the strap assembly establishing a taut condition. The weight element is manually movable by a user during the exercise routine along an arcuate path in a plane of stable motion while the tensile force maintains the taut condition of the strap assembly. The strap assembly advantageously provides guided and stabilized motion of the weight element for the user thereby minimizing risk of injury. The resistance force of the system is user-variable by attaching different size weight elements to the strap assembly.

Owner:DV LV LTD

Uterine cancer vaginal canal resection operation instrument

PendingCN109875676AEliminate dropSimple and reliable processSurgical instruments for heatingCancer cellCorpus Uteri Cancer

The invention discloses a uterine cancer vaginal canal resection operation instrument, belonging to the technical field of medical instruments. The uterine cancer vaginal canal resection operation instrument specifically comprises a fixing unit and a cutting unit. A vaginal inner circumcision type is proposed for the first time, and the vaginal canal is fixed on the inner wall of the vaginal canal. On the one hand, the vaginal canal has closed the uterus before resection; on the other hand, the uterus to be resected is prefixed on a device and can be directly pulled and moved out by the deviceafter the resection operation is completed without additionally placing a forceps clip for clamping and traction, the process is simple and reliable, and the possibility of cancer cells falling is eliminated fundamentally. In addition, the resection operation is directly completed in the vaginal canal, which is different from a traditional mode of resection from the outer wall of the vaginal canal, and the operation convenience is clear at a glance.

Owner:武欣 +1

Intermittent rod part collection device

The invention discloses an intermittent rod part collection device. The intermittent rod part collection device comprises a distribution mechanism achieving one-by-one sorting and a collection mechanism achieving intermittent collection. The distribution mechanism comprises a conveying channel assembly and an intermittent distribution assembly. The conveying channel assembly comprises a supportingplate, a limiting baffle, a left channel plate, a right channel plate, a flow guide plate and a support. The collection mechanism comprises a conveying belt and a vertical conveying assembly. The vertical conveying assembly comprises a fixed support, a second air cylinder and a rod supporting plate. The device further comprises a controller, and a first air cylinder, the conveying belt and the second air cylinder are all electrically connected with the controller. According to the intermittent rod part collection device, rod part products of a production line are arranged, workpieces are arranged in a containing box in order through the vertical conveying assembly, the fall of rod parts is eliminated, and damage generated when the workpieces fall into the containing box directly from theconveying belt is avoided; and control is simple, and automatic control of the whole device can be achieved through single variables.

Owner:TIANJIN SAIXIANG M&E ENG CO LTD

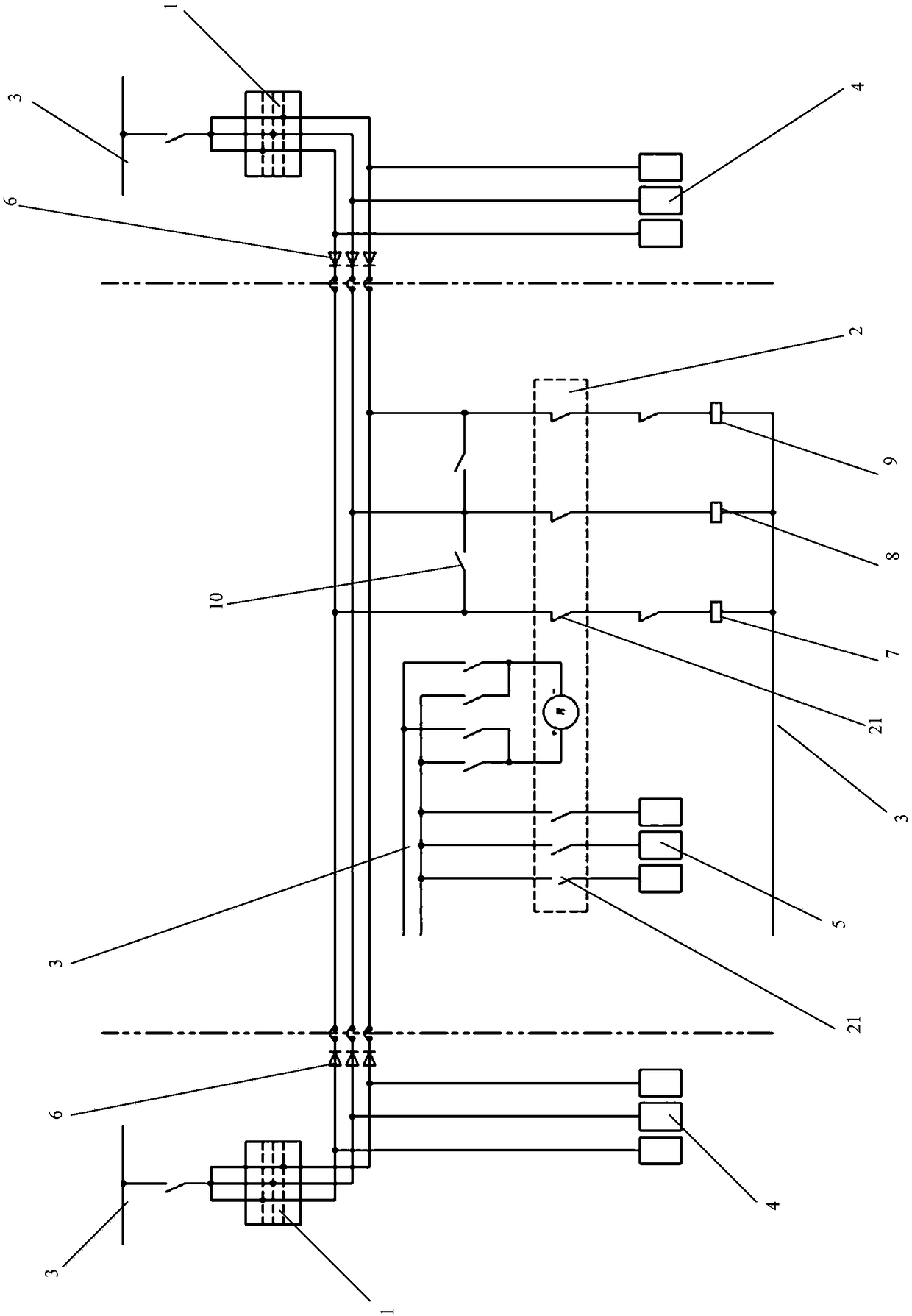

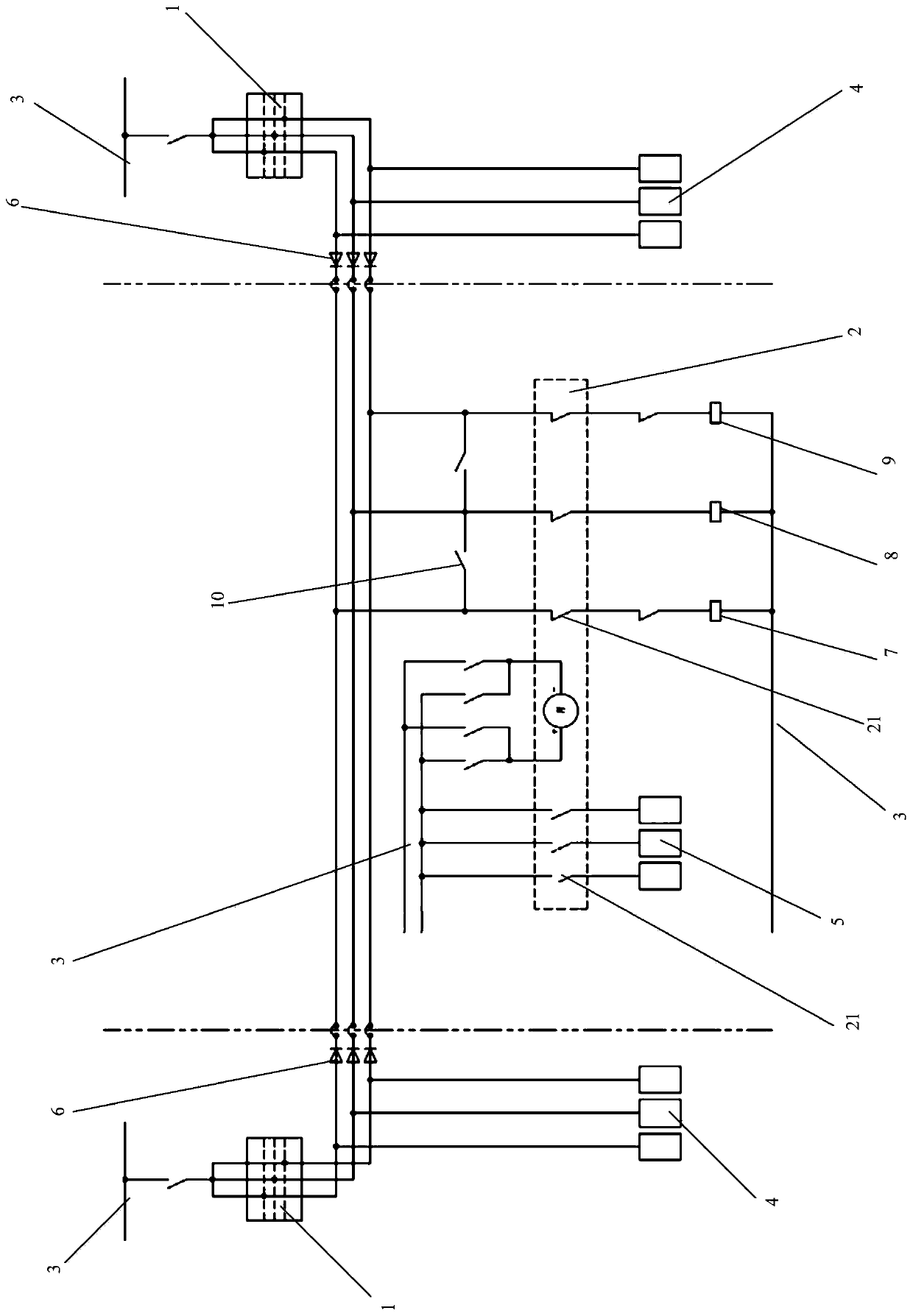

Three-position switch control system and control method

ActiveCN108313074AReduce configurationEliminate dropElectric switchesLocomotivesElectricityControl system

The invention provides a three-position switch control system and control method. The control system comprises a control knob arranged in a cab and a three-position switch device arranged on the car roof, the three-position switch device is electrically connected with the control knob, and the three-position switch device and the control knob are both connected with a vehicle-mounted power supply.The three-position switch device is internally provided with limiting switches corresponding to different control positions separately, and turning-on or turning-off of the limiting switches of the different control positions is driven by the rotation of the control knob. The three-position switch control system allows a driver to realize control over the three-position switch device on the car roof in the cab, the operation is simple and fast, operation by climbing to the roof is not needed, the allocation of manpower and material resources and related resources is reduced, and potential safety hazards such as falling or electric shocking during the operation of an operator climbing to the roof are eliminated.

Owner:CRRC TANGSHAN CO LTD

Automatic sizing one-handed locking pliers

An automatically adjustable locking pliers or tool includes a jaw fixed to a first handle and a jaw that pivots about the first handle. The pivoting jaw is connected to a lower tightening handle. A lever connects the tightening handle and first handle. A self-adjusting sizing and locking mechanism includes a thumb jaw sizing piece located near the jaws and movable to open the jaws so that they can be sized around a workpiece. When the thumb jaw sizing piece is released, the jaws automatically size and clamp lightly around the workpiece. The locking mechanism uses balls between a locking rod and a tapered surface. Locking occurs when the balls wedge between the rod and the tapered surface. A release cylinder is connected to a release paddle movable to unlock the mechanism. The sizing piece and locking mechanism are operable to automatically size and lock the pliers or tool.

Owner:HUNTER MARC W

Clip installation tool

ActiveUS20190337103A1Eliminate dropProgramme-controlled manipulatorEngine sealsEngineeringMechanical engineering

Clip installation tooling and method for installing clips including a magazine for holding a plurality of clips and clip end of arm tooling for picking up at least one clip at a time. The magazine stops at predetermined intervals for spacing each respective clip into openings on the magazine. The clip end of arm tooling has at least one body connected to a plurality of cylinders each with an inlet / outlet port receiving vacuum / air blow off. The clip end of arm tooling picks up one or more clips from the magazine at a time. The vacuum generation to the port(s) assists in holding the clip(s) and eliminates dropping clip(s) prior to placement for installation of the clip(s). After the clip(s) is / are placed, air blow off through the port(s) insures clip(s) are removed from the clip end of arm tooling and stay in the desired position(s).

Owner:MAGNA EXTERIORS INC

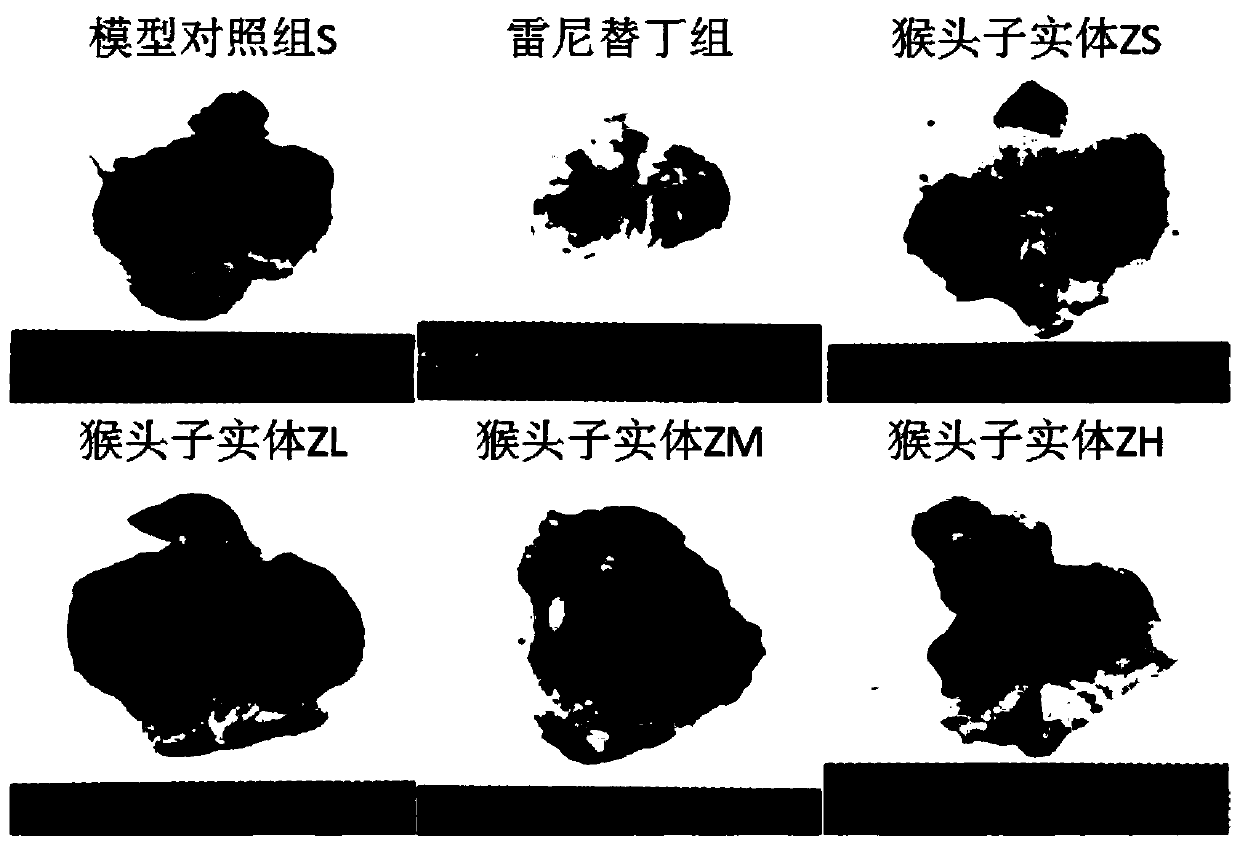

Hericium erinaceus tableting candy, and preparation method and application thereof

InactiveCN110326700AMeet food safety and quality standardsEliminate dropDigestive systemConfectioneryIsomaltooligosaccharideAdditive ingredient

The invention relates to the technical field of functional food processing, in particular to a hericium erinaceus tableting candy, and a preparation method and an application thereof. The invention provides the hericium erinaceus tableting candy which at least comprises the following ingredients in parts by weight: 40-60wt% of hericium erinaceus powder, 15-20wt% of lactose, 10-16wt% of isomaltooligosaccharide, 6-10wt% of maltodextrin, 4-8wt% of fructose and 0.5-1wt% of magnesium stearate. The hericium erinaceus does not contain any food prohibited auxiliary materials, and the tableting candy meets a food safety quality standard and has an active meaning in the application of preparing functional food and / or drugs capable of preventing and / or treating gastric mucosal lesion.

Owner:SHANGHAI LEIYUNSHANG PHARMA

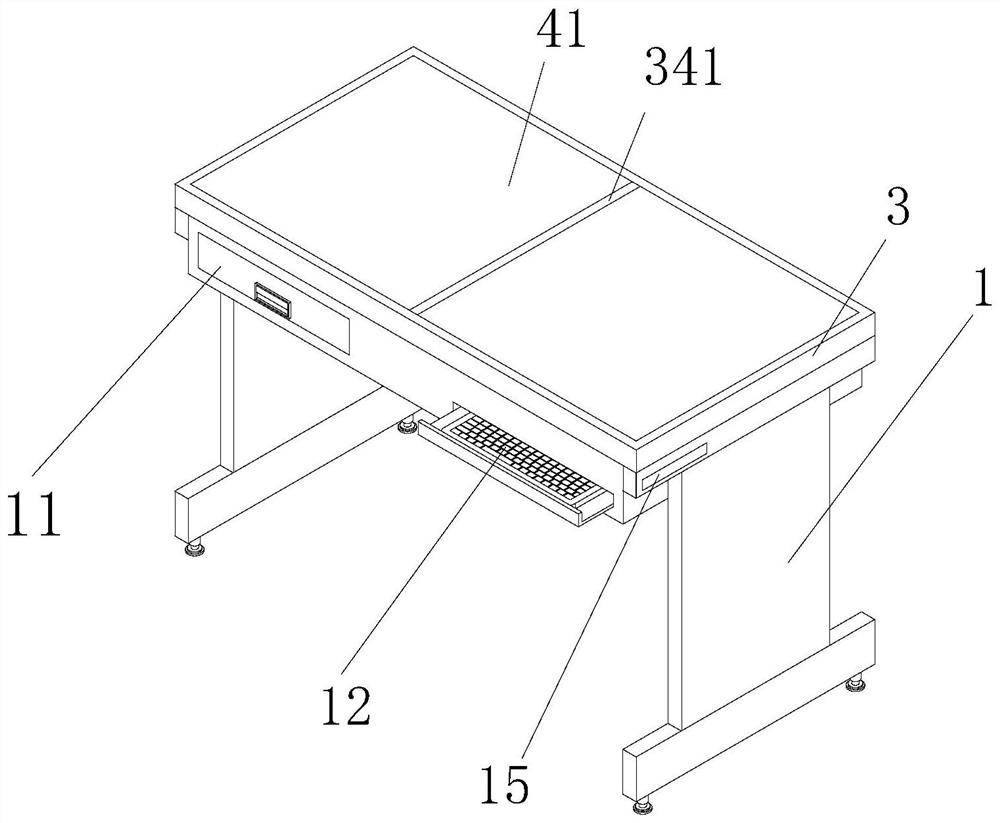

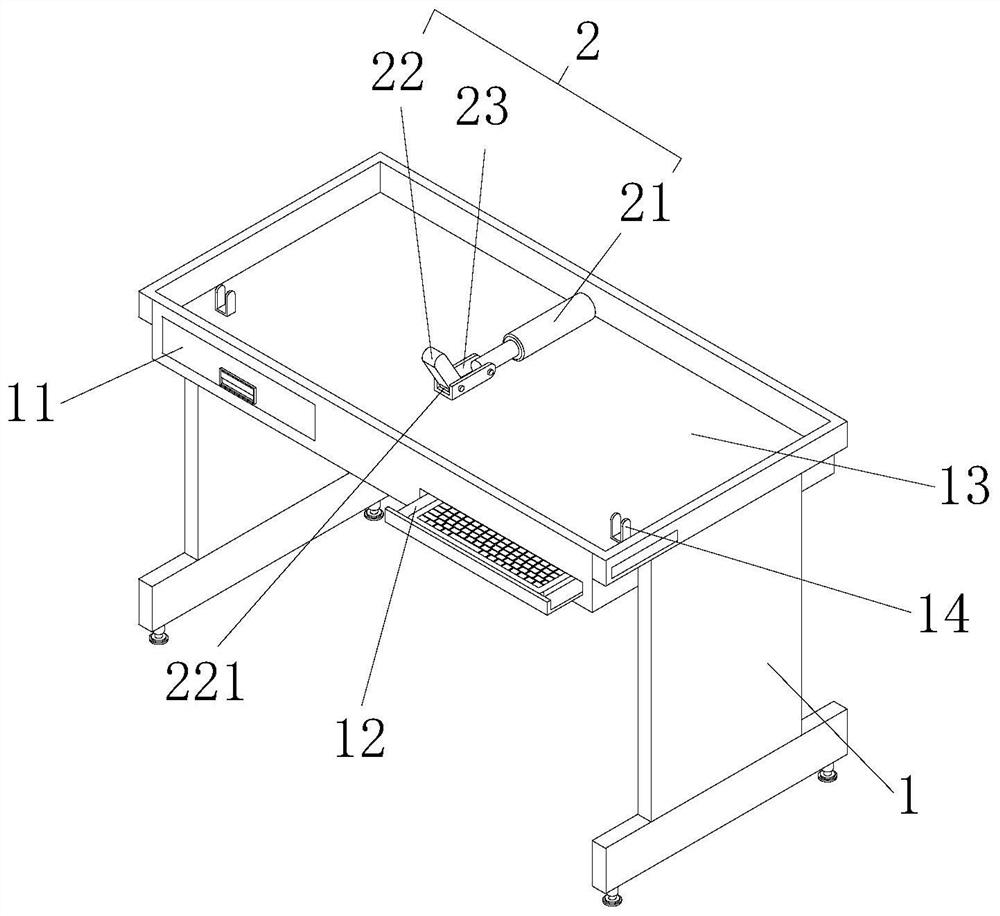

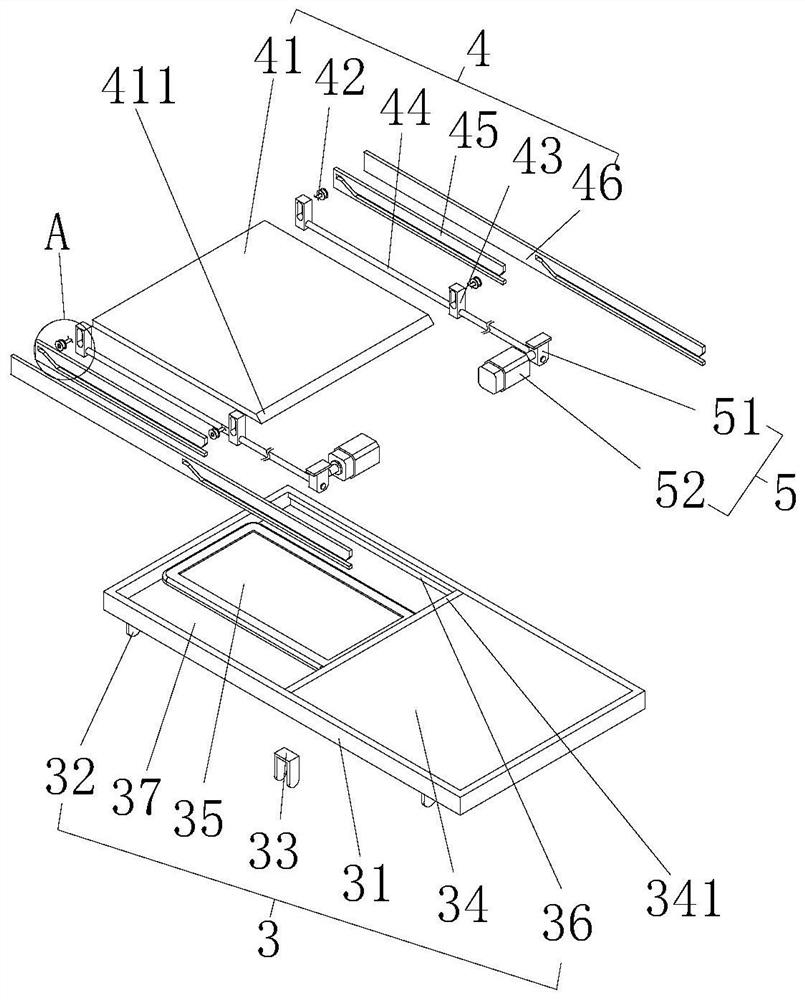

Territorial space planning and designing drawing system

ActiveCN112773090AImprove applicabilityEliminate dropOffice tablesExtensible tablesMechanical engineeringSystems engineering

The invention provides a territorial space planning design drawing system which comprises a support, an angle adjusting assembly is arranged at the top end of the support, the support is connected with a drawing assembly and a shielding assembly through the angle adjusting assembly, a groove is formed in the top end of the support, and symmetrically-arranged first hinge seats are fixed in a groove body of the groove. Through cooperation of the drawing assembly and the shielding assembly, the structure can be switched, the requirements of drawing personnel for computer drawing, manual drawing or combined drawing of the computer drawing and the manual drawing are met, and therefore the applicability of the drawing system is improved.

Owner:浙江金余规划设计有限公司

Image forming apparatus and image formation control method

InactiveUS20050214049A1Eliminate dropEasy to adjustRegistering devicesElectrographic process apparatusContact image sensorStart time

Owner:CANON KK

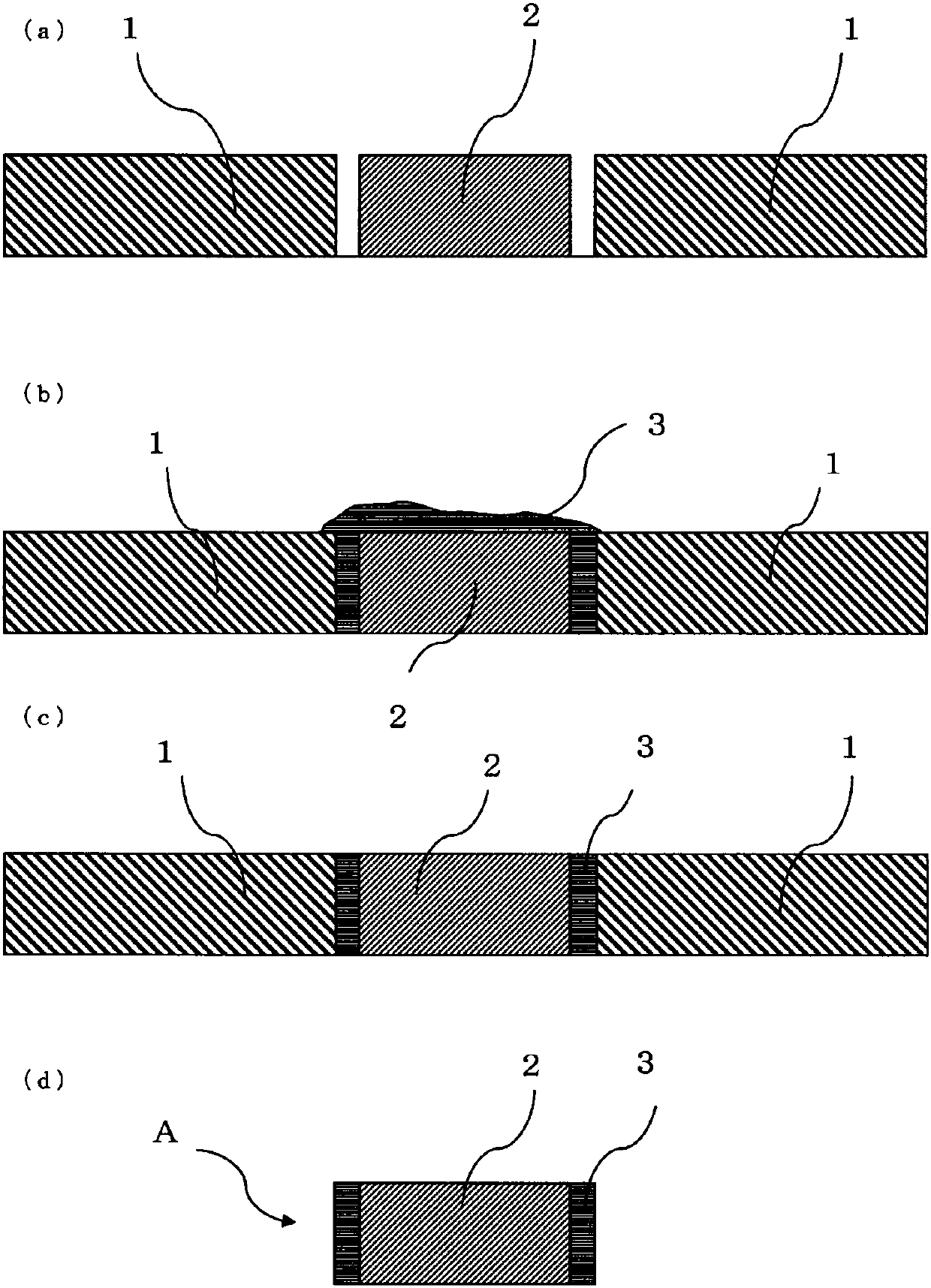

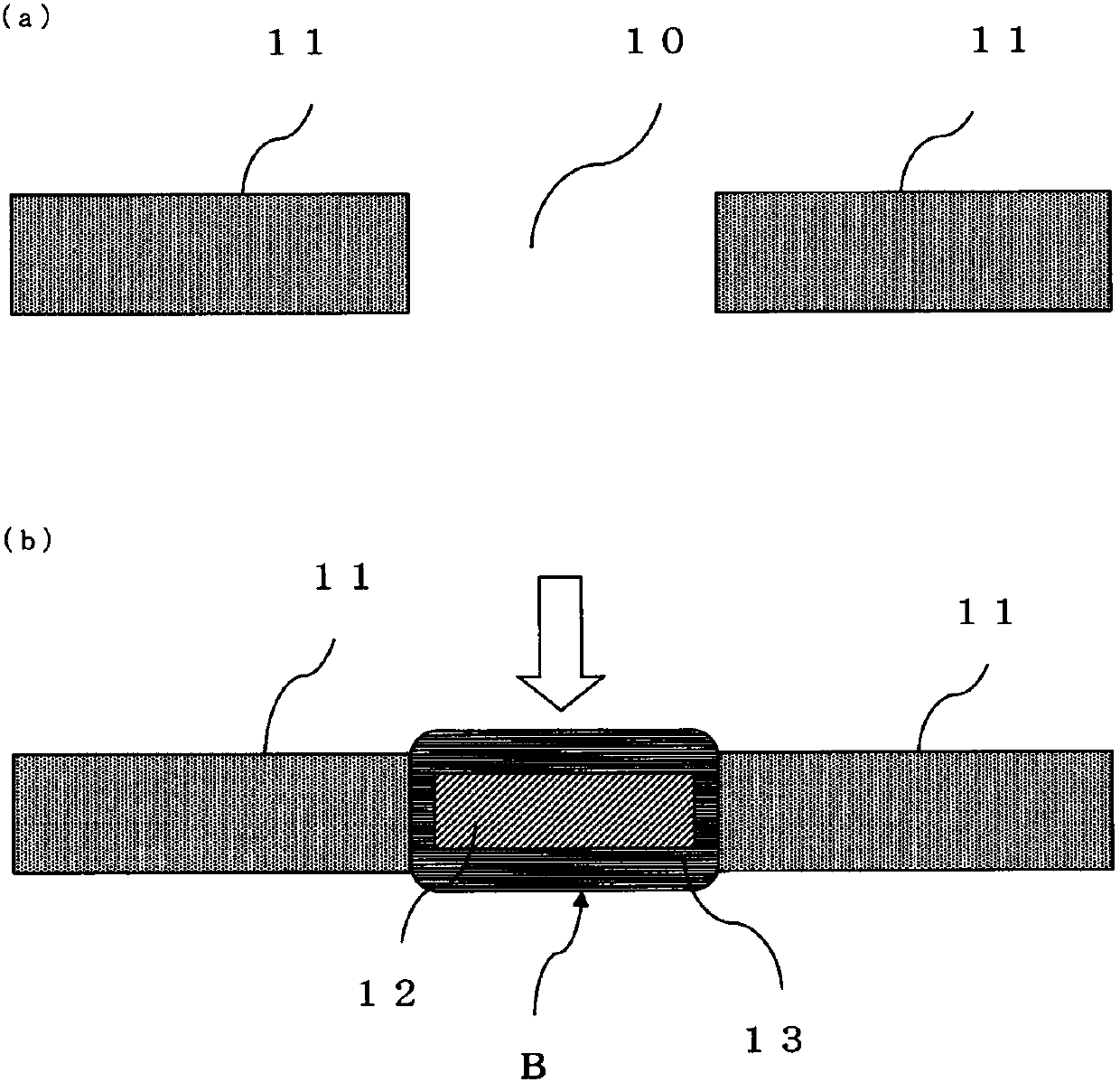

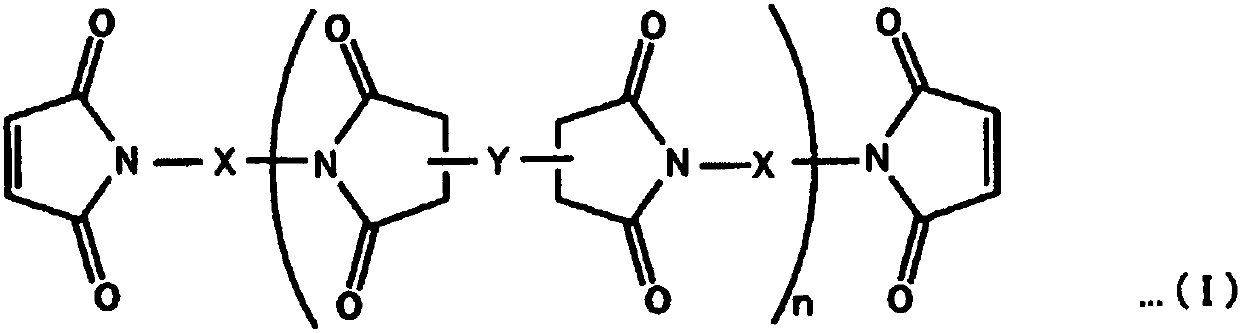

Heat dissipation material adhering composition, heat dissipation material having adhesive, inlay substrate, and method for manufacturing same

ActiveCN107709502AEasy to fixExcellent adhesionNon-macromolecular adhesive additivesFilm/foil adhesivesPolymer scienceAdhesive

Owner:TATSUTA ELECTRICWIRE & CABLE

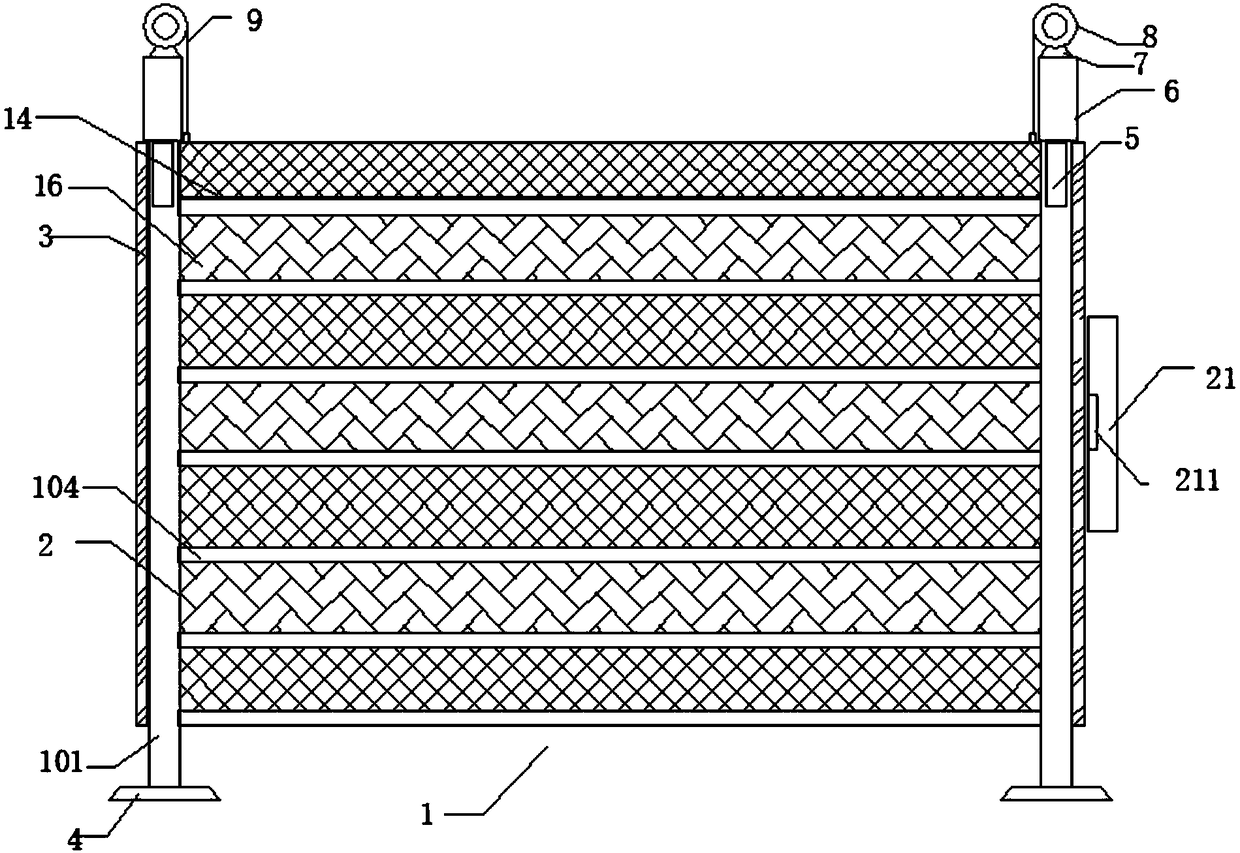

Automatic delivery express shelf for modern logistics

ActiveCN108394665AImprove the safety of useAvoid damageStorage devicesEngineeringLogistics management

Owner:沈阳递家物流股份有限公司

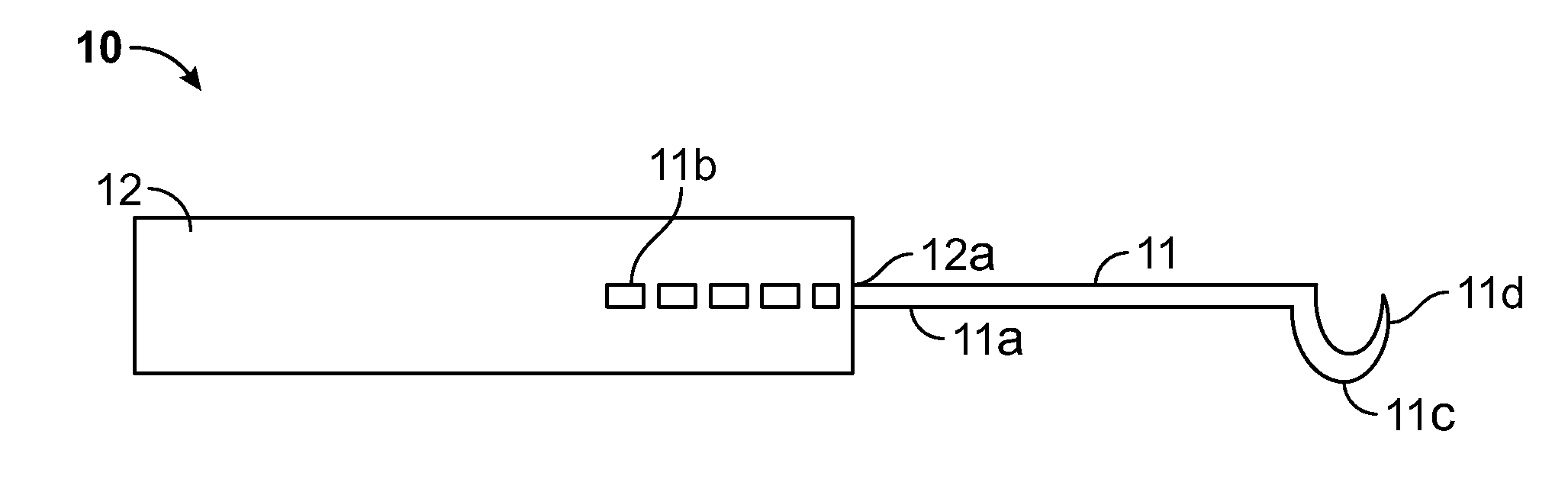

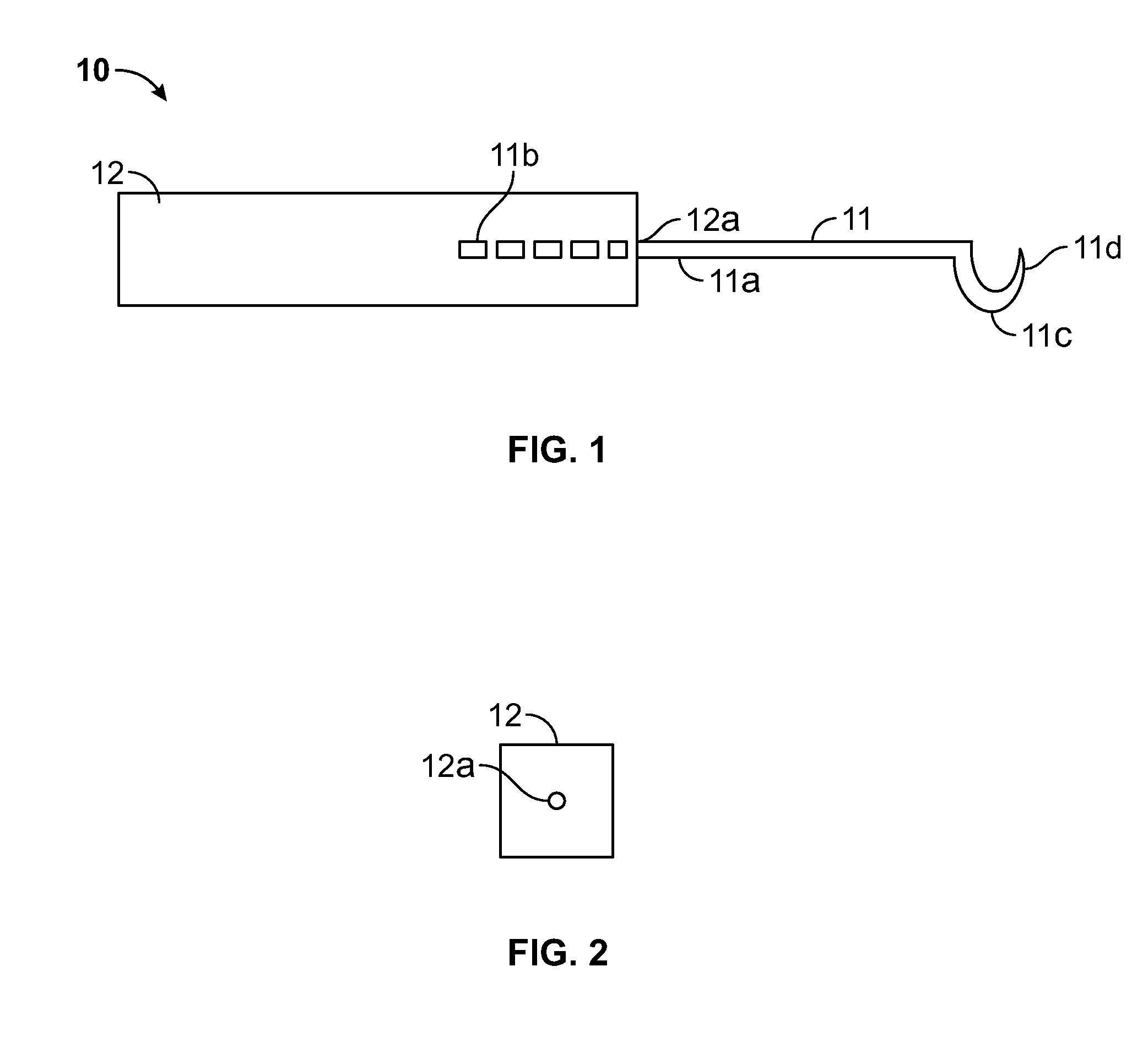

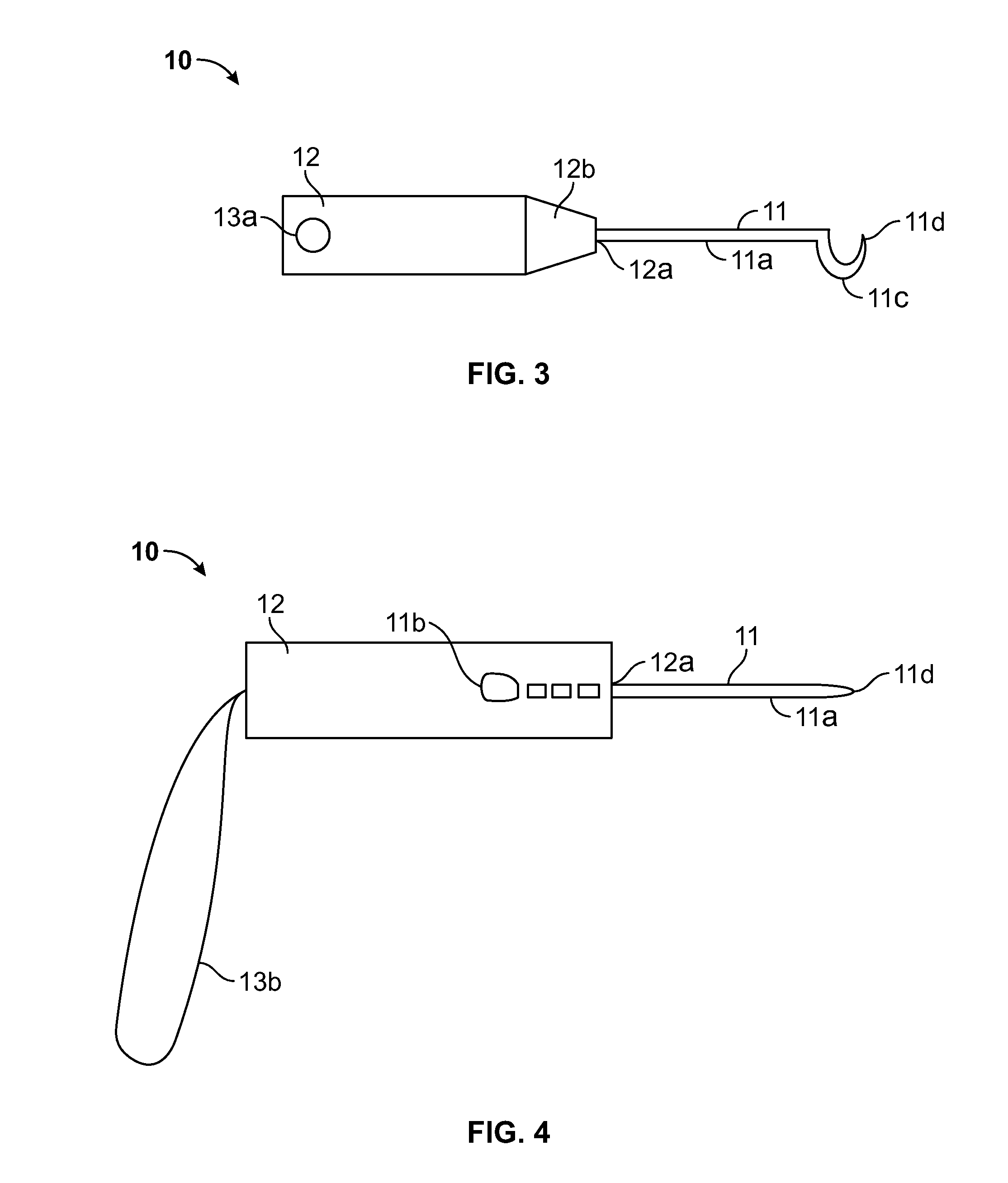

Flipping hook apparatus for manipulating food items

InactiveUS20150130198A1Reduce in quantityEliminating food droppingLifting devicesKitchen equipmentEngineeringFood item

A flipping hook apparatus for allowing a user to reduce the number of cooking utensils needed for a given job, eliminating food dropping, moving a user's hand further away from a heating element while manipulating food, minimizing arm and wrist twisting while manipulating food, and more safely lower food onto cooking surfaces. The flipping hook apparatus comprises a hook member having an elongated shaft and a hook portion permanently attached to an elongated handle. The hook portion is defined by a 90 degree bend in the elongated shaft, followed by a 1 inch diameter roll in a 150 to 160 degree angle. It is contemplated that the hook member is constructed out of stainless steel and the handle is constructed out of wood having up to three coats of polyurethane so as to seal and protect the wood.

Owner:CROOM TEDDY

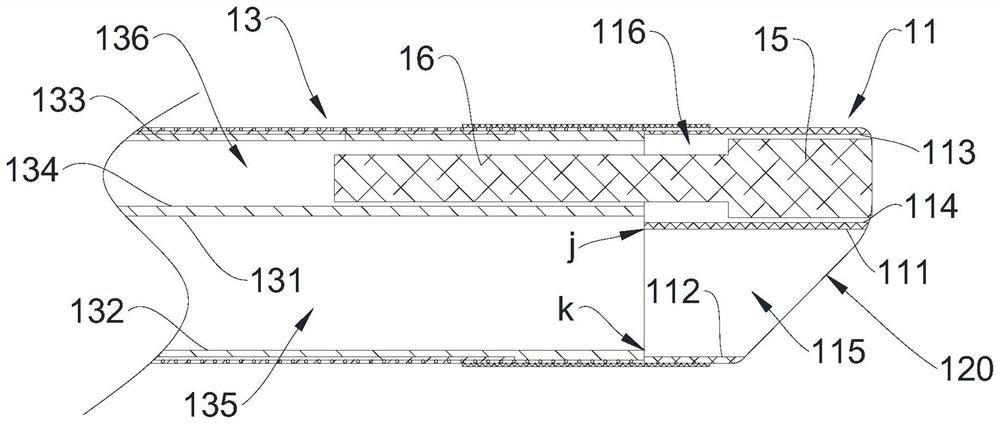

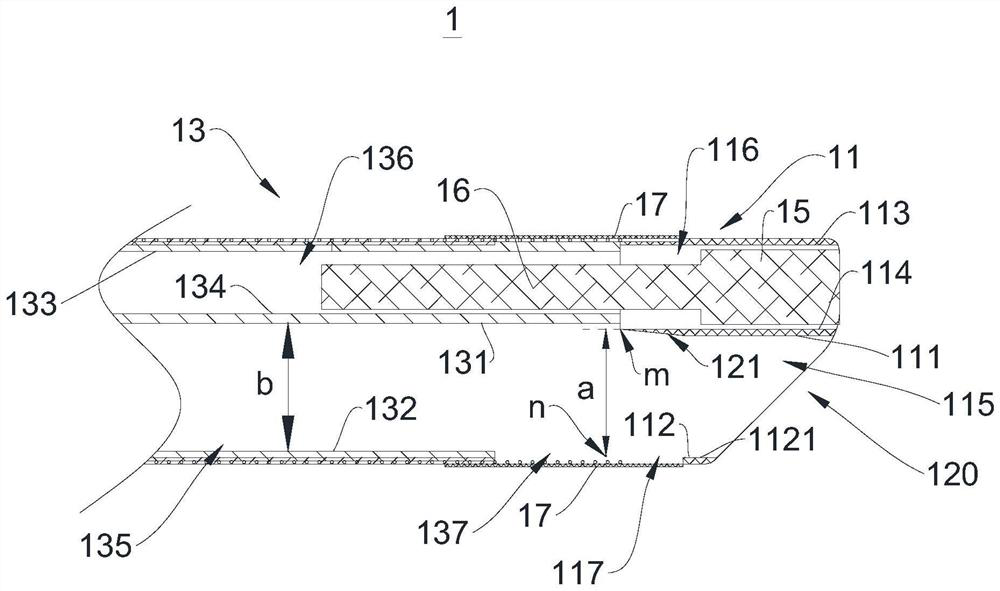

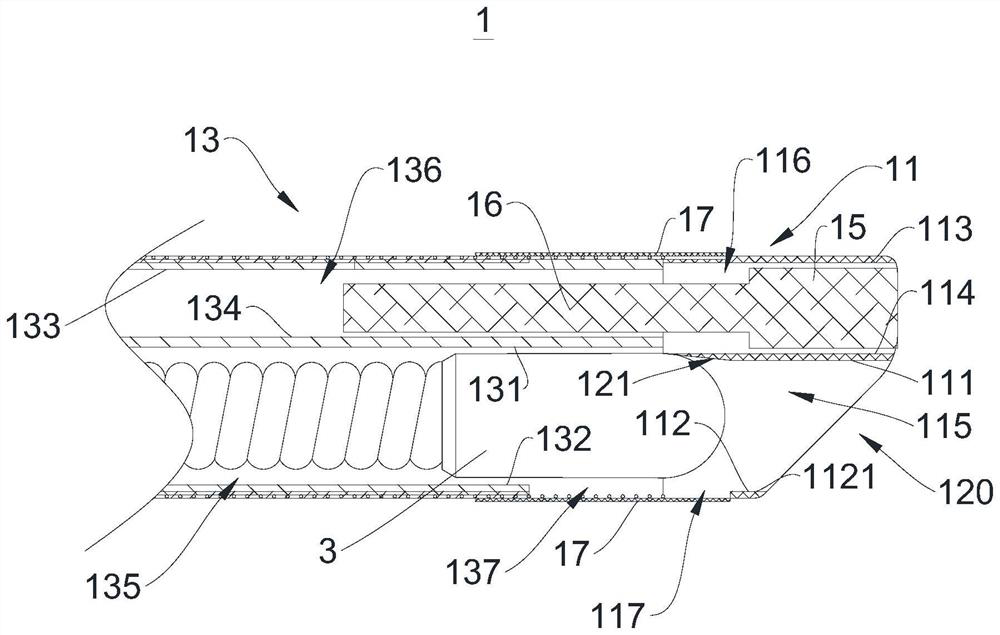

Imaging catheter, tip, catheter body and medical device

PendingCN113349705AWide range of outer diametersEliminate dropGastroscopesOesophagoscopesCatheterMedical device

The embodiment of the invention provides an imaging catheter, a tip, a catheter body and a medical device, and relates to the field of medical instruments.The imaging catheter comprises the catheter body and the tip, wherein the catheter body comprises a first shuttling wall and a second shuttling wall; a first cavity is formed between the first shuttling wall and the second shuttling wall; the tip comprises a first mounting wall and a second mounting wall; a second cavity is formed between the first mounting wall and the second mounting wall; the second cavity is communicated with the first cavity; the near end of the first mounting wall corresponds to the position between the first shuttling wall and the second shuttling wall; and the radial distance between the m point and the n point is a, the inner diameter of the first cavity is b, and a is more than or equal to b, so that the fall is eliminated, and an instrument can enter the second cavity from the first cavity. The instrument compatible with the imaging catheter has a large outer diameter range, so that more types of instruments can enter the second cavity from the first cavity.

Owner:MICRO TECH (NANJING) CO LTD

A kind of automatic delivery express shelf for modern logistics

ActiveCN108394665BImprove the safety of useAvoid damageStorage devicesLogistics managementBraced frame

Owner:沈阳递家物流股份有限公司

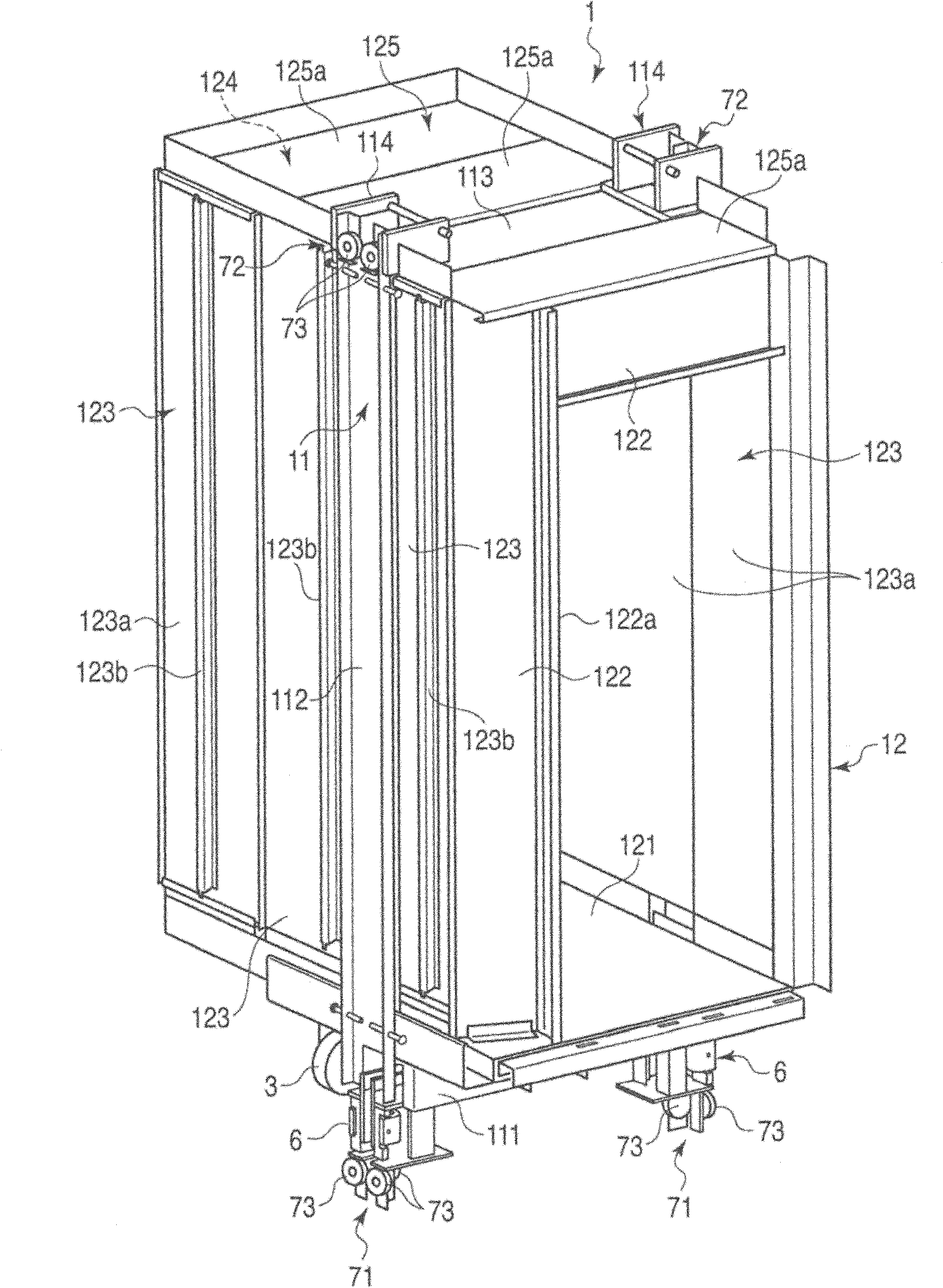

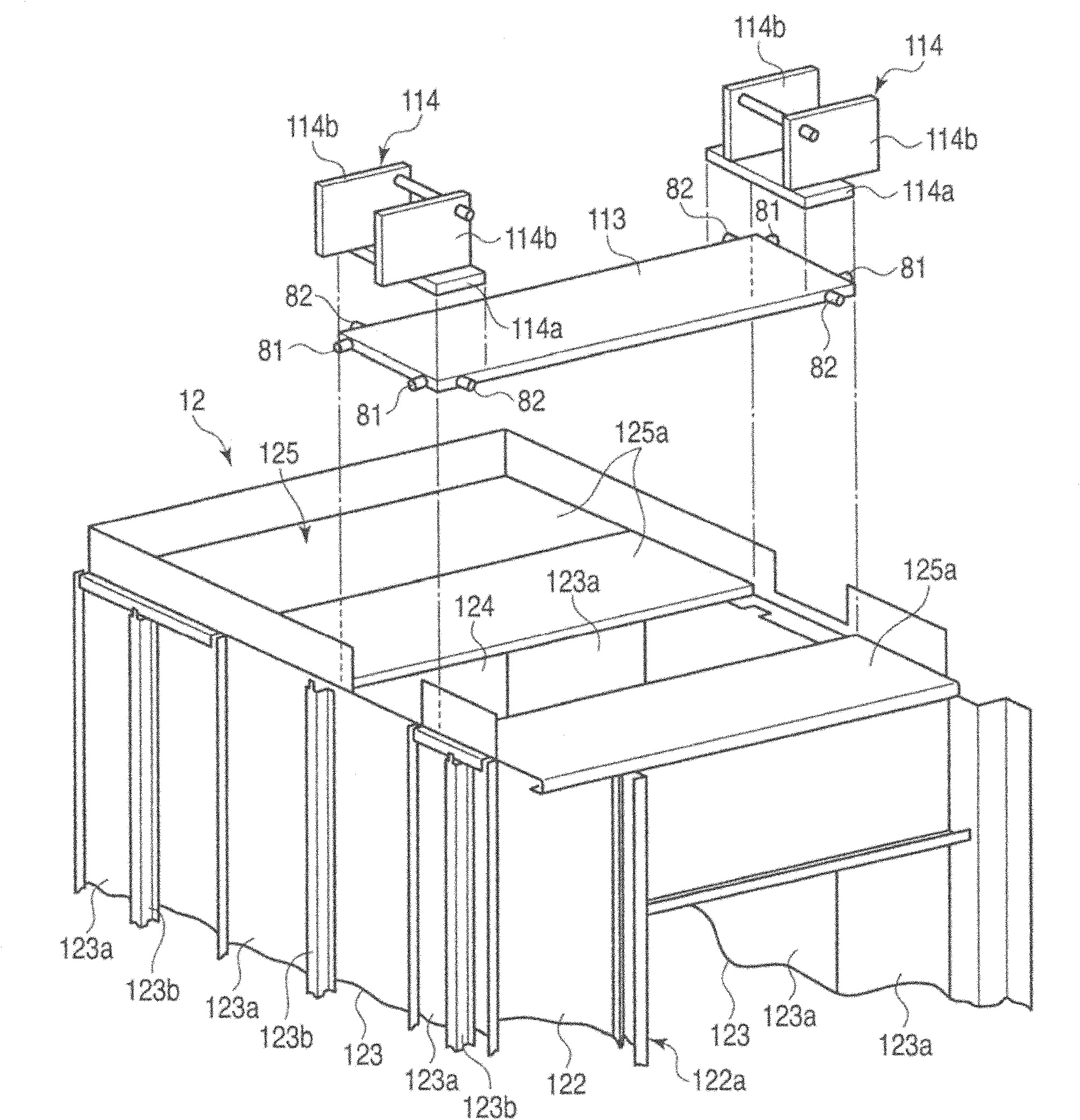

Elevator car

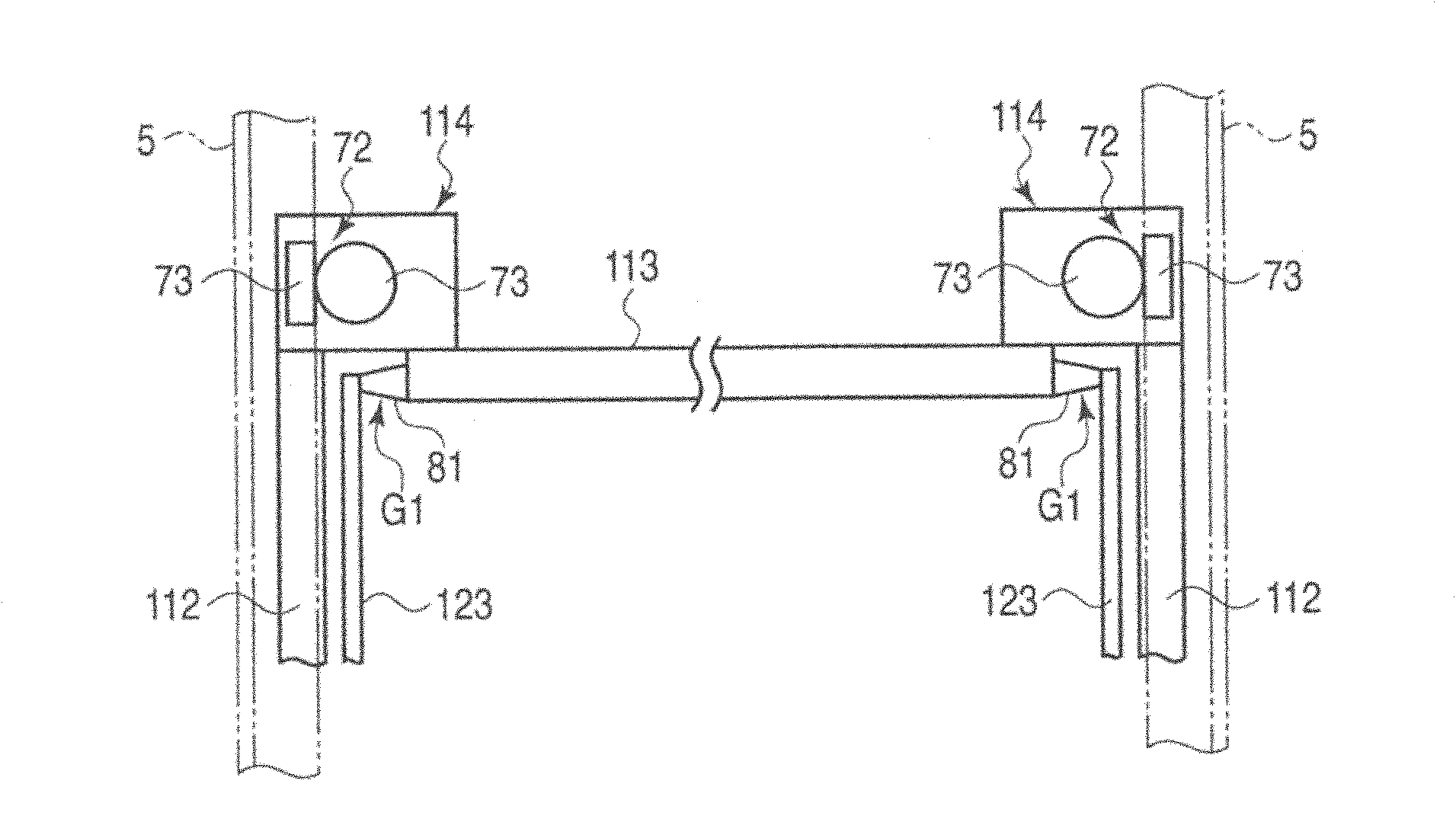

InactiveCN102190232BGuaranteed StrengthCurb tiltElevatorsBuilding liftsEngineeringAutomotive engineering

The invention provides an elevator car. The elevator car (1) comprises a vertical frame (112), an upper beam (113) and a bracket (114). A pair of vertical frames (112) is arranged along a guide rail; and the upper beam (113) is arranged between the pair of vertical frames (112) so as to be used as a part of a ceiling (125) of a car chamber (12). The upper beam (113) is connected with the upper end of the vertical frame (112) by the bracket (114).

Owner:TOSHIBA ELEVATOR KK

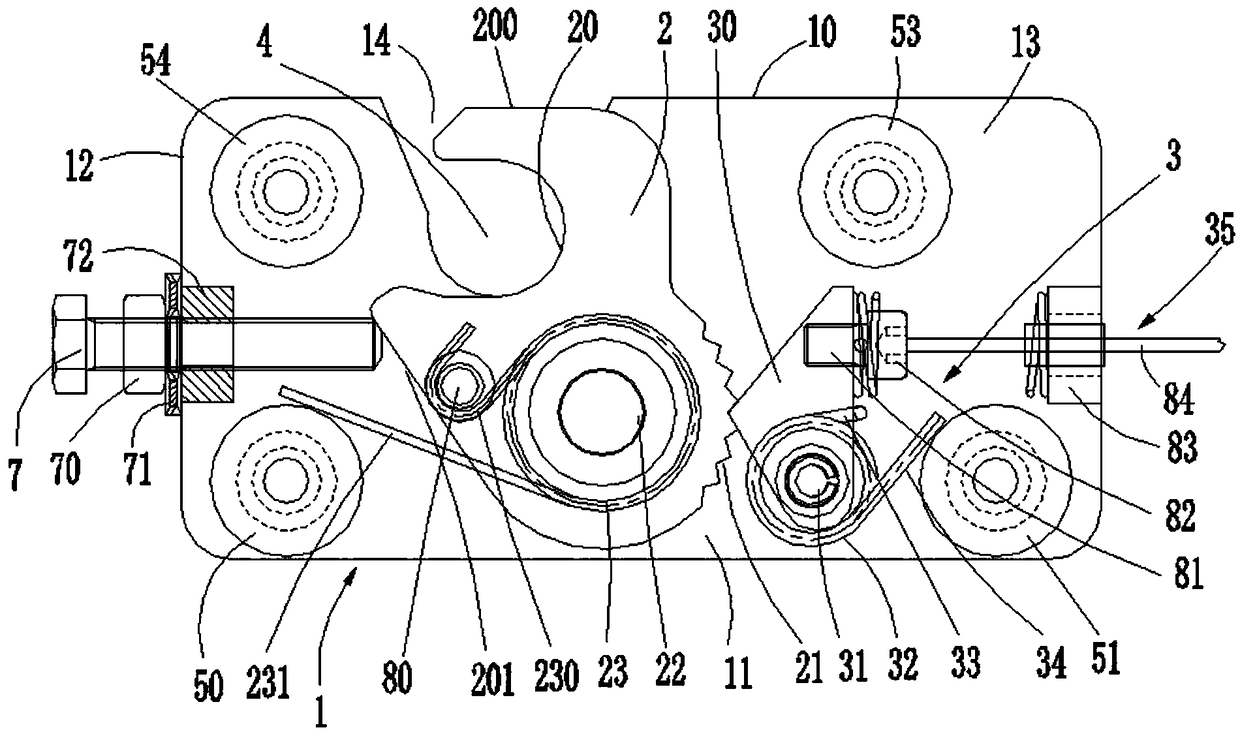

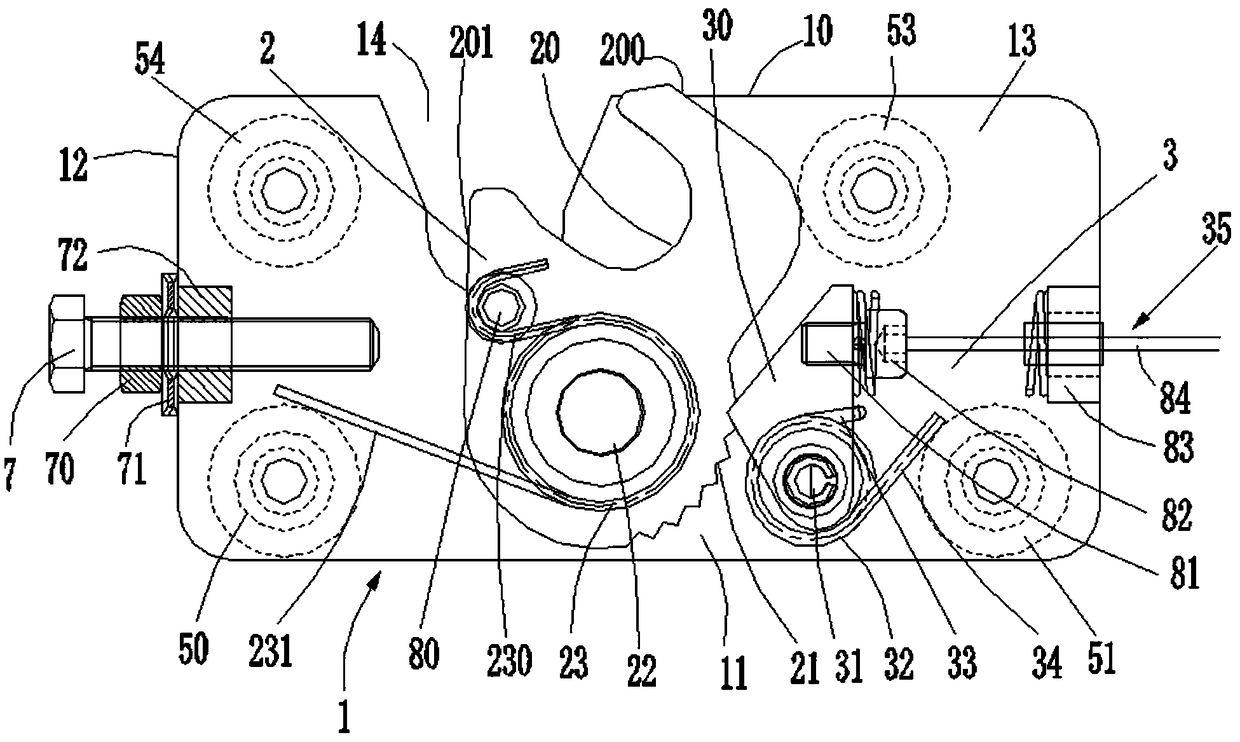

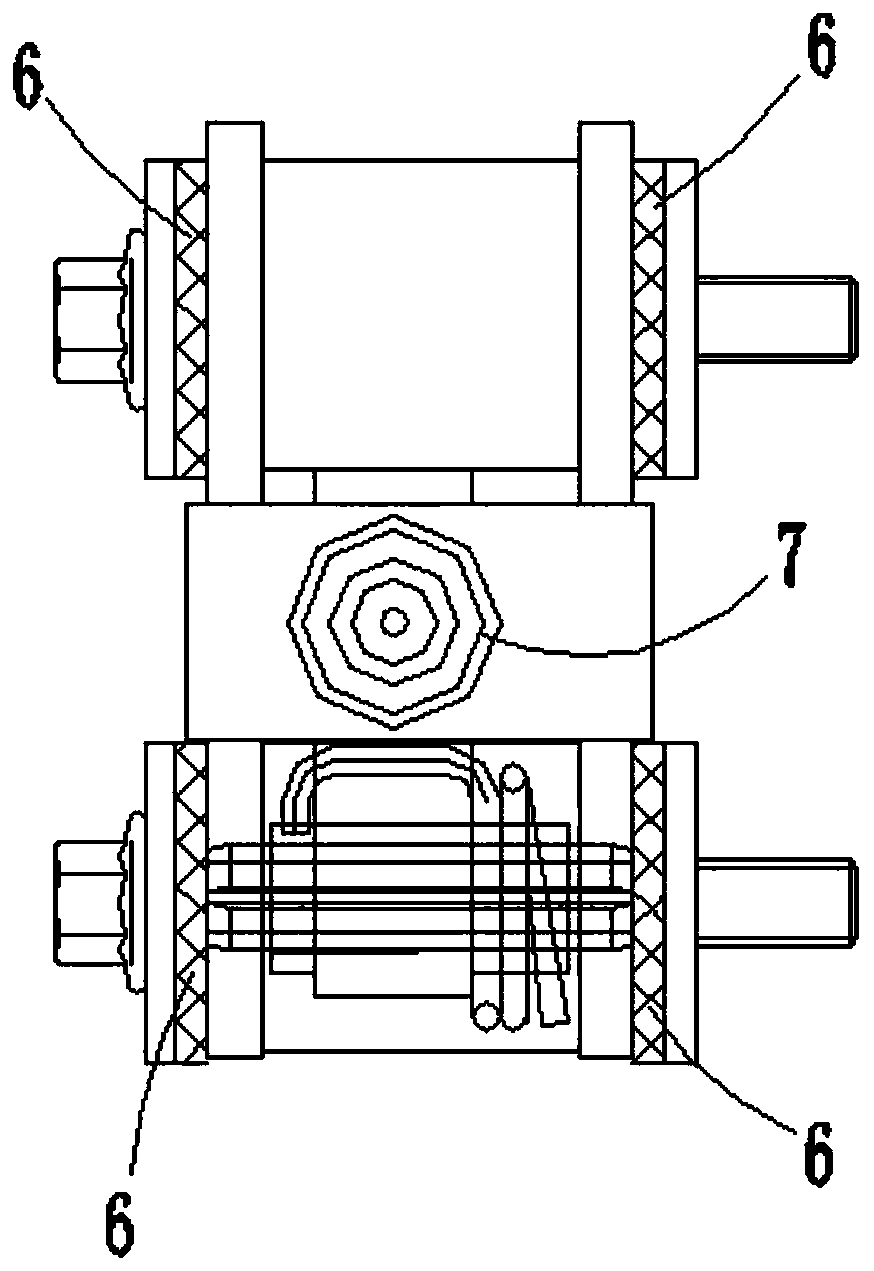

Locking device

The invention relates to the technical field of locks and provides a locking device comprising a lock body; the lock body is a chamber formed by a pair of first side plates, a pair of second side plates and a pair of third side plates by surrounding; a lock head and a lock assembly are disposed in the chamber; one of the first side plates of the lock body has a first groove that is recessed into the chamber; a portion of the lock head has a second groove that is recessed toward the interior thereof; an inner side wall of the second groove and one section of the inner side walls of the first groove may be enclosed to form a locking interval for locking the foreign object; a part away from the second groove of the locking head is provided with a locking member that can engage the locking assembly and secure the locking head. By arranging the second groove forming the locking interval and the locking member for fixing the lock head with the locking assembly on the lock head, and the lockassembly is also disposed on the lock body, the falling possibility of the lock assembly is eliminated; the locking interval can be opened or closed at any time; the manufacturing cost of the whole device is low and the device is suitable for promotion.

Owner:XIAOGAN DINGZUO ELECTROMECHANICAL EQUIP

Guided sieve plate valve tower

The invention relates to a guiding sieve plate float valve tower, belonging to a gas-liquid mass-transfer separation plant in chemical process. The guiding sieve plate float valve tower disclosed herein mainly comprises a tower body (1), a tower plate (2), a down-flow plate (7), a seal pan (9), etc., wherein the liquid inlet of the tower plate (2) is provided with a bubbling promoter (6), the plate surface of the tower plate is provided with a floating tongue (3), a guiding pore (4), a sieve pore (5) and a float valve. According to the invention, when the gas velocity is low, the float valve on the tower plate is not open, gas only passes through the guiding pore (4), the sieve pore (5) and the floating tongue (3); when the gas velocity increases to a certain level, the float valve is open, and the opening height of the float valve increases gradually with the increase of the gas velocity. The guiding sieve plate float valve tower disclosed herein has the advantages of simple structure, low cost, and greatly raised operation flexibility and separation efficiency.

Owner:河北化大科技有限公司

Three-position transfer switch control system and control method

ActiveCN108313074BReduce configurationEliminate dropElectric switchesLocomotivesElectricityDriver/operator

The invention provides a three-position switch control system and control method. The control system comprises a control knob arranged in a cab and a three-position switch device arranged on the car roof, the three-position switch device is electrically connected with the control knob, and the three-position switch device and the control knob are both connected with a vehicle-mounted power supply.The three-position switch device is internally provided with limiting switches corresponding to different control positions separately, and turning-on or turning-off of the limiting switches of the different control positions is driven by the rotation of the control knob. The three-position switch control system allows a driver to realize control over the three-position switch device on the car roof in the cab, the operation is simple and fast, operation by climbing to the roof is not needed, the allocation of manpower and material resources and related resources is reduced, and potential safety hazards such as falling or electric shocking during the operation of an operator climbing to the roof are eliminated.

Owner:CRRC TANGSHAN CO LTD

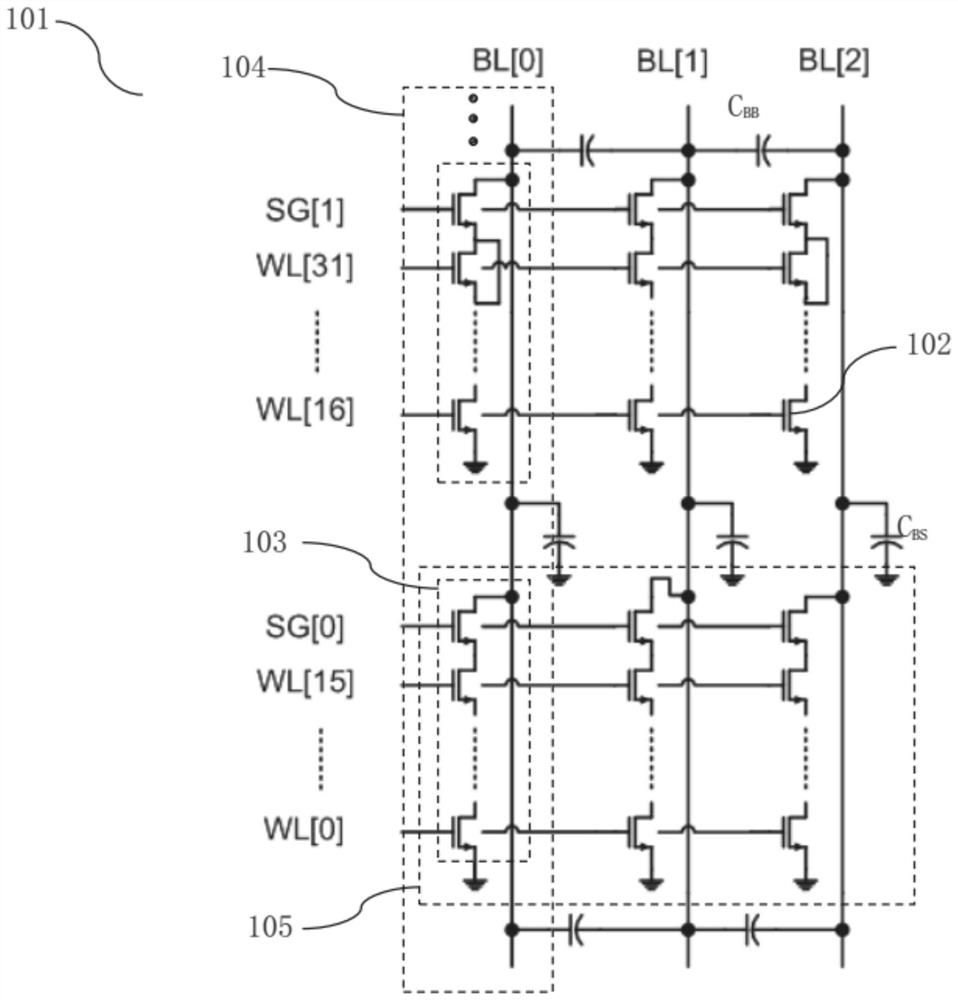

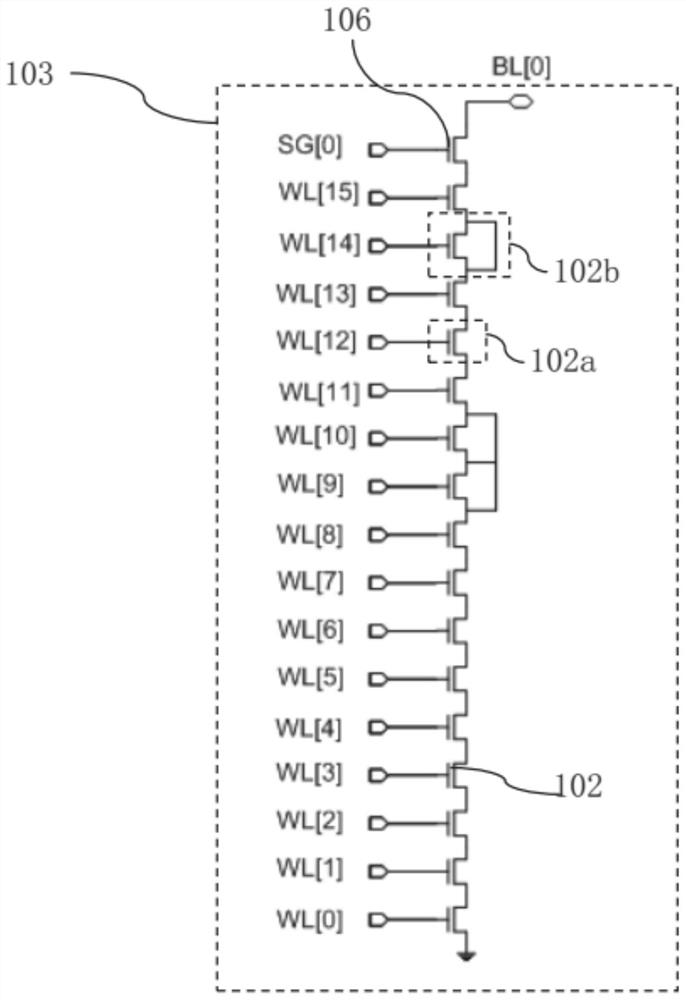

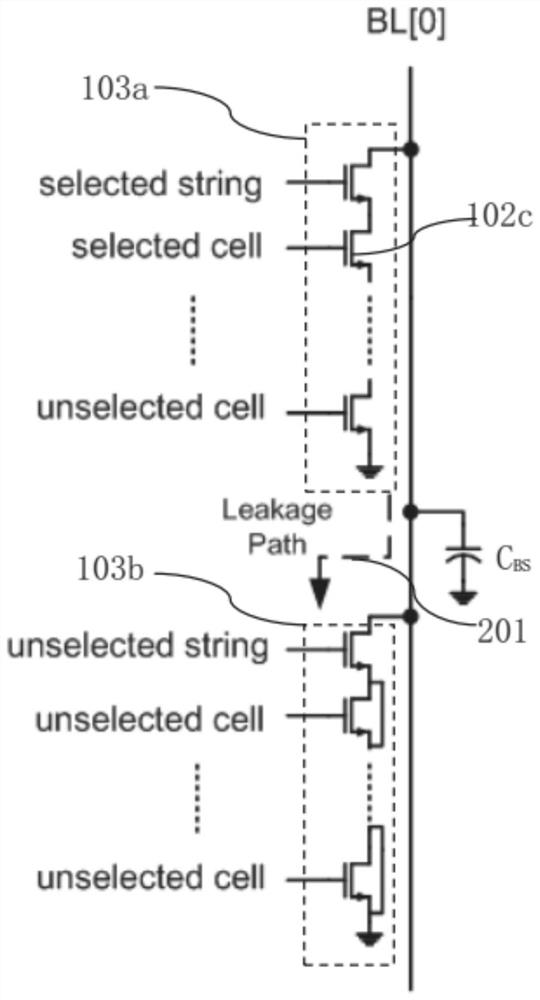

nand type rom

ActiveCN110021309BEliminate bit line voltage dropEliminates lower bit line voltageRead-only memoriesComputer hardwareBit line

The invention discloses an NAND type ROM. A column structure comprises a plurality of NAND type memory cell series structures and bit lines. Each storage unit series structure is connected between thecorresponding bit line and the corresponding source line; each memory cell series structure in the row structure forms a corresponding memory cell series structure row; the source lines form a dynamic split type source electrode bias voltage structure, and specifically, any two adjacent storage unit series structures in the storage unit series structure row are connected with different source lines; source lines connected with different memory cell series structures in the same column are different. The bias voltage in the reading process is set as follows: the source line corresponding to the read memory cell is connected with a low level, the source line corresponding to the memory cell series structure adjacent to the read memory cell in the same row is connected with a high level, andthe source line corresponding to the memory cell series structure adjacent to the read memory cell in the same column structure is connected with a high level. The reading voltage drop caused by bitline electric leakage, bit line capacitance sharing and bit line crosstalk can be eliminated.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com