Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

57 results about "Register window" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

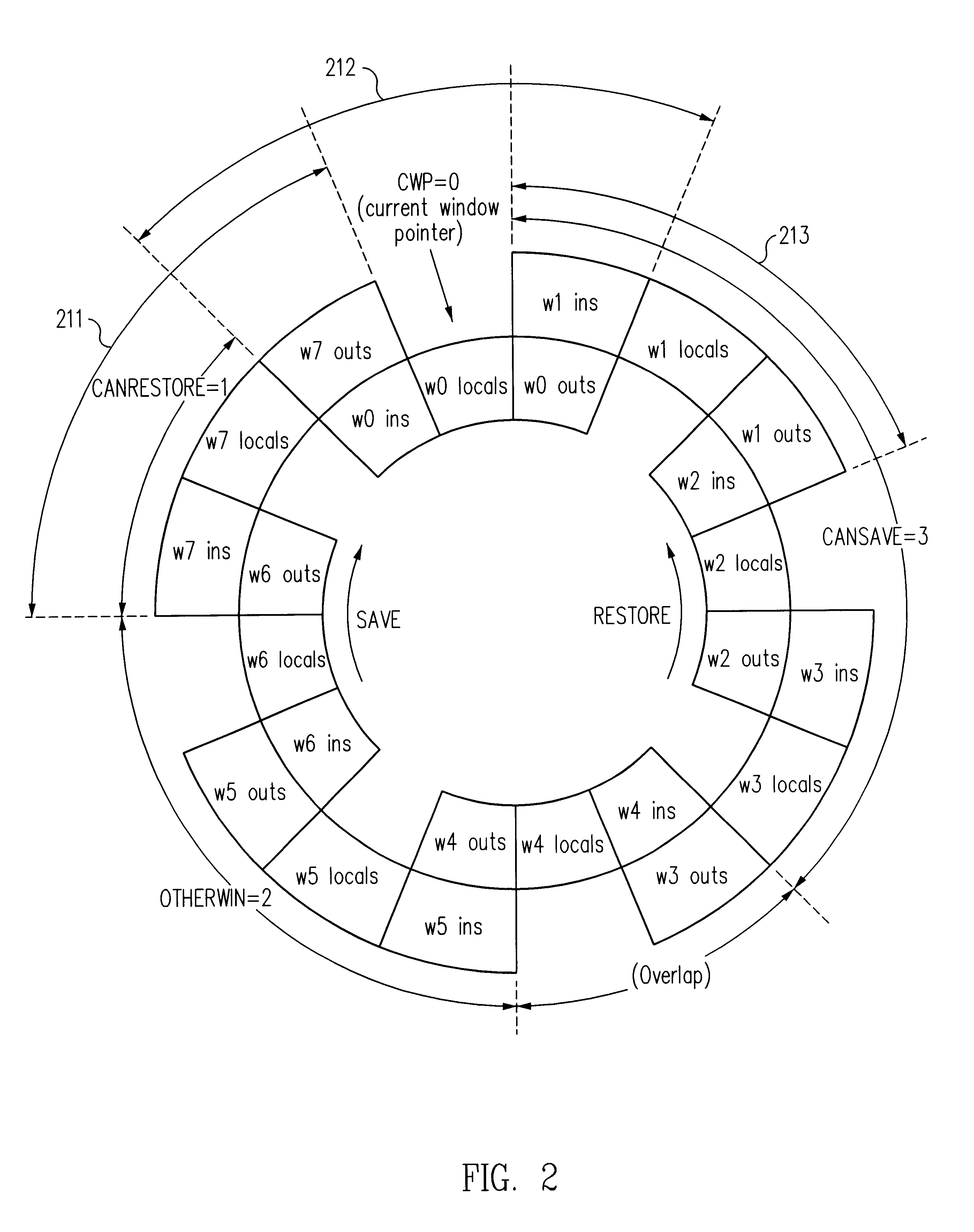

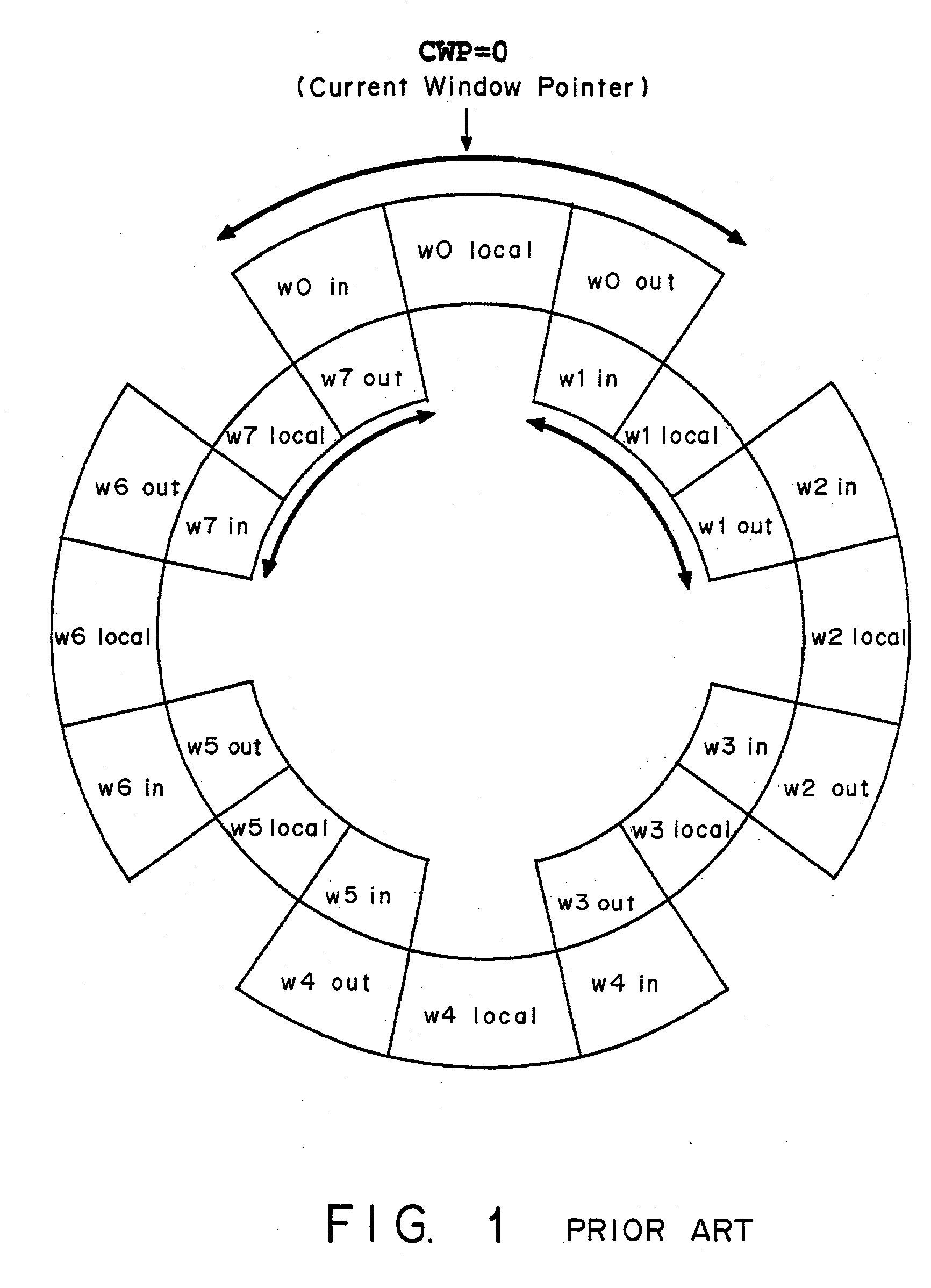

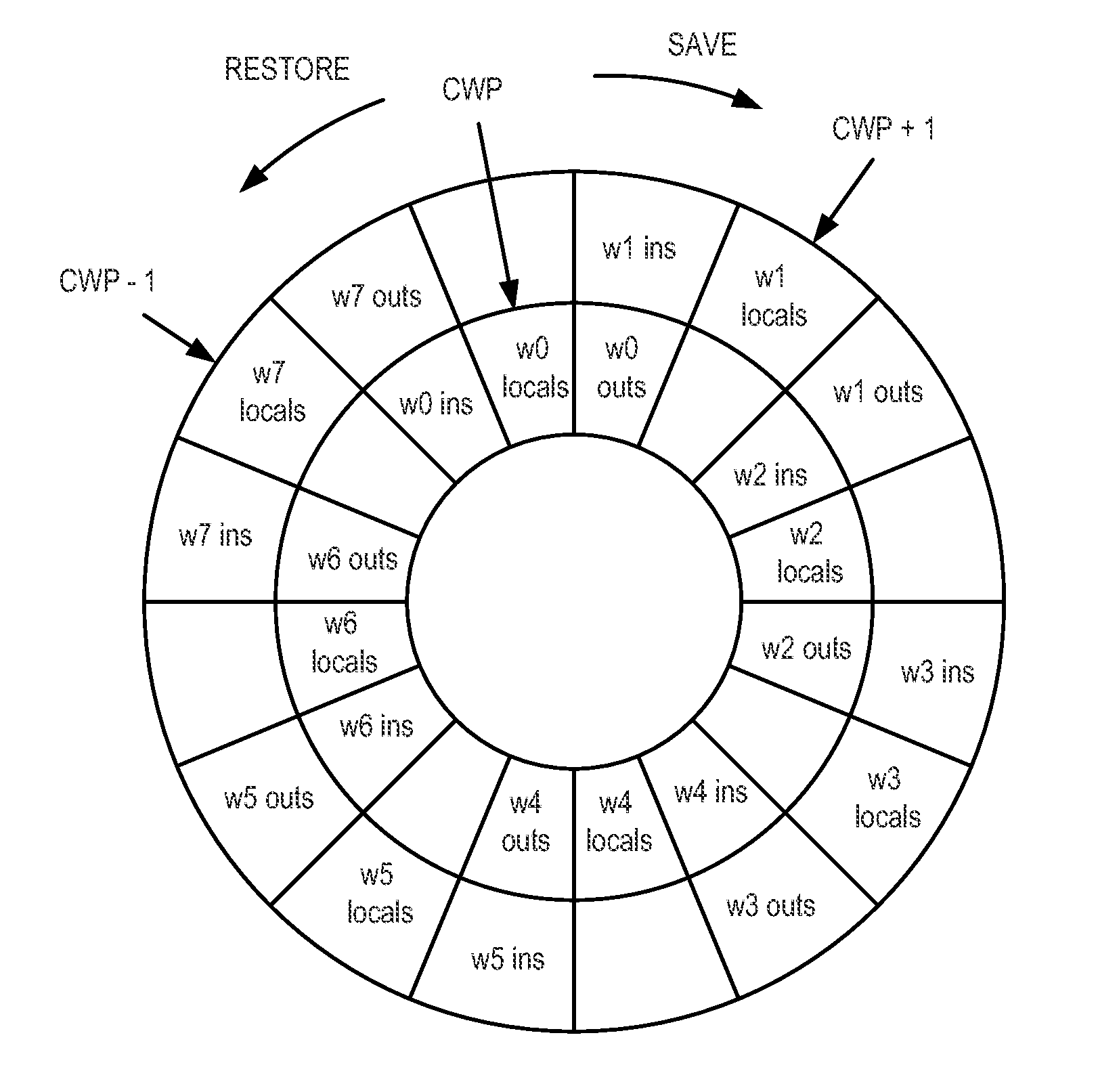

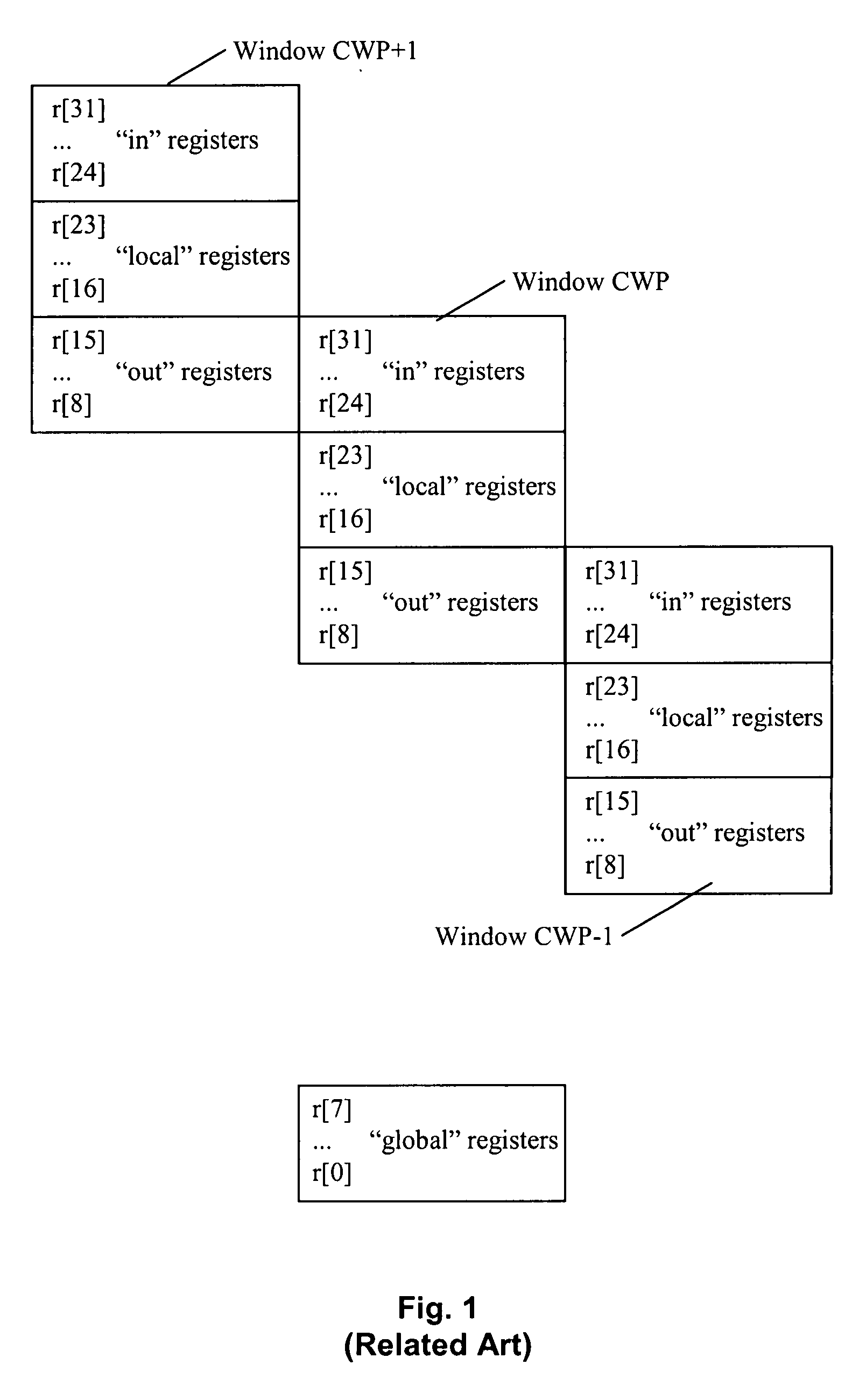

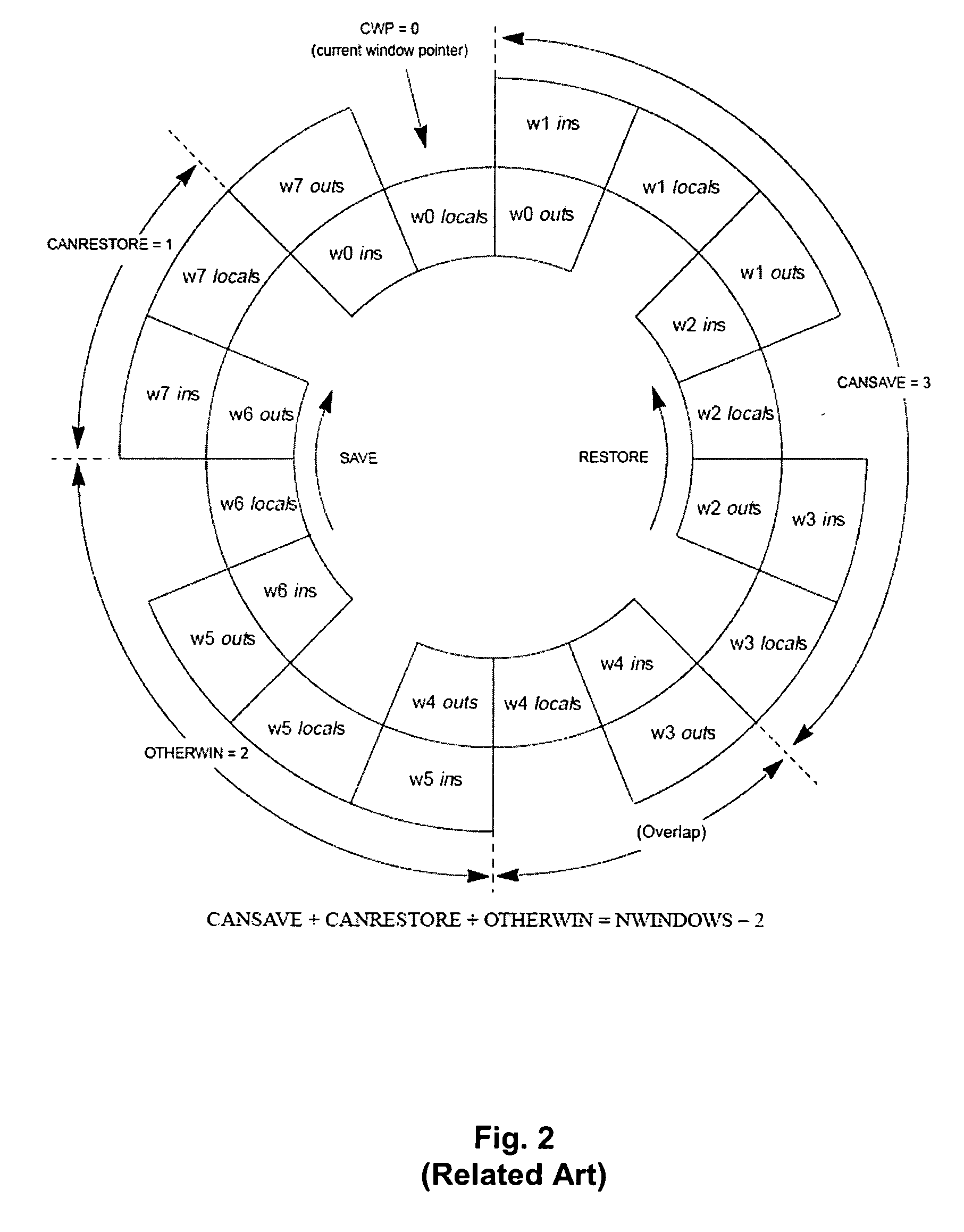

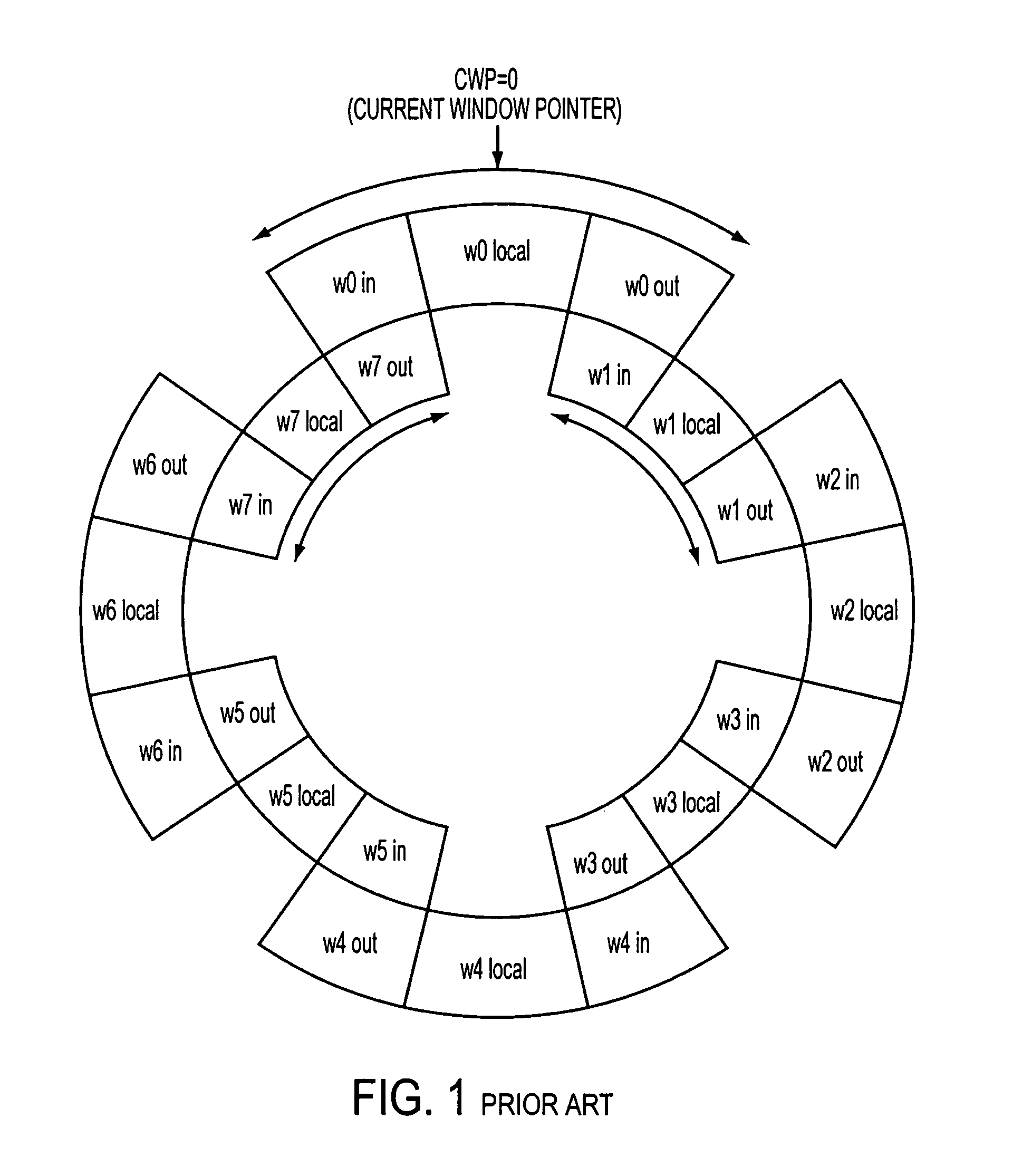

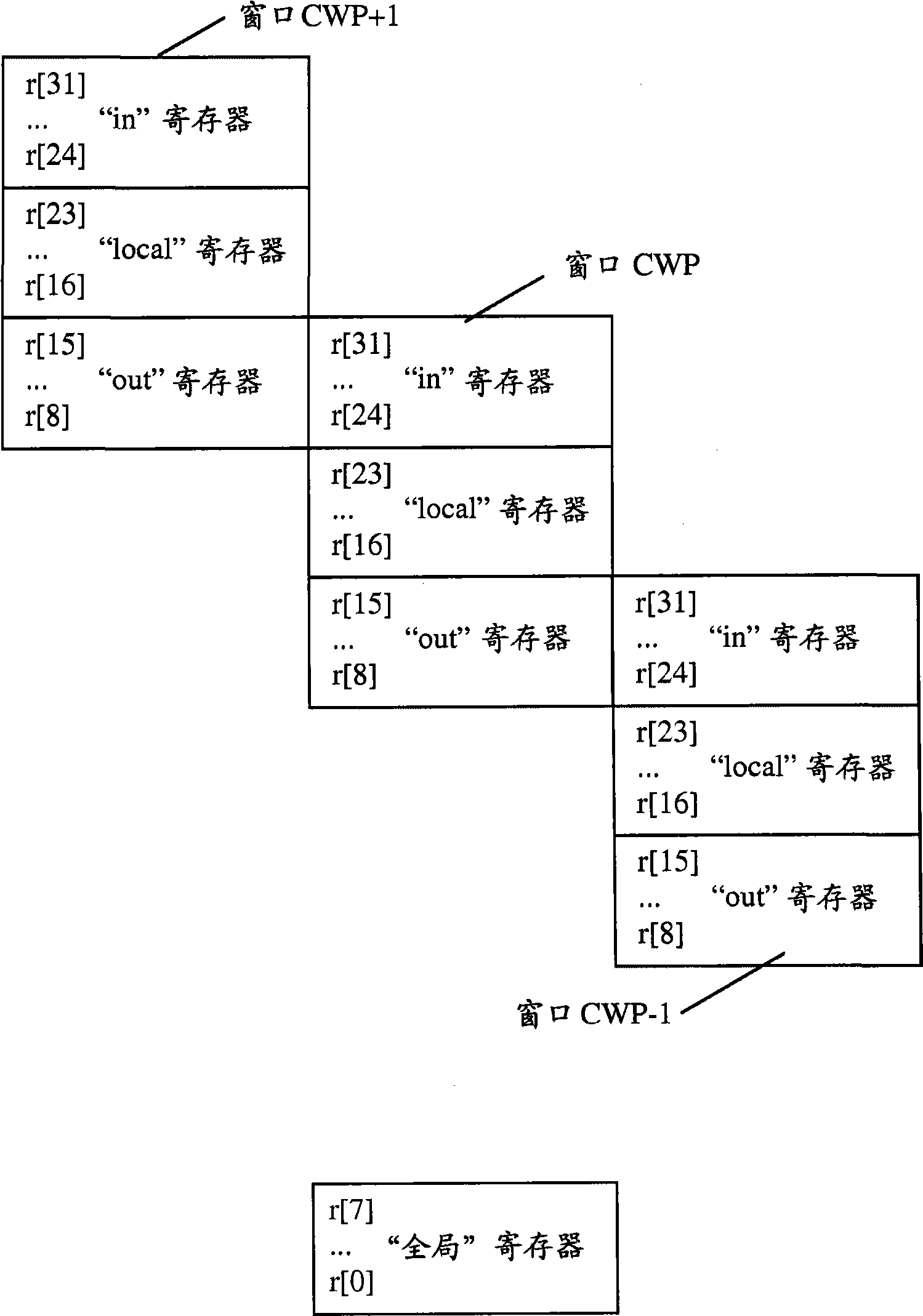

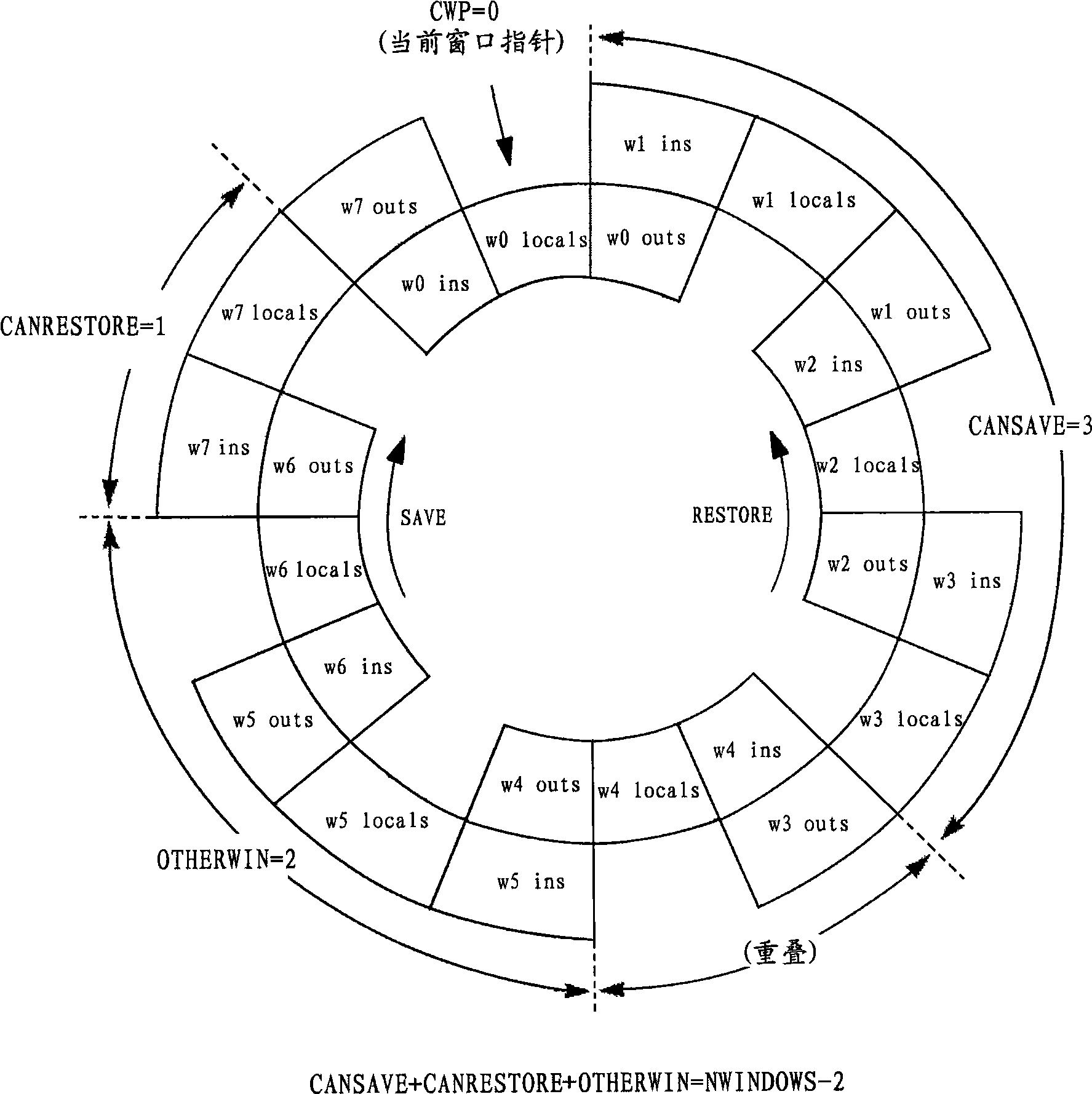

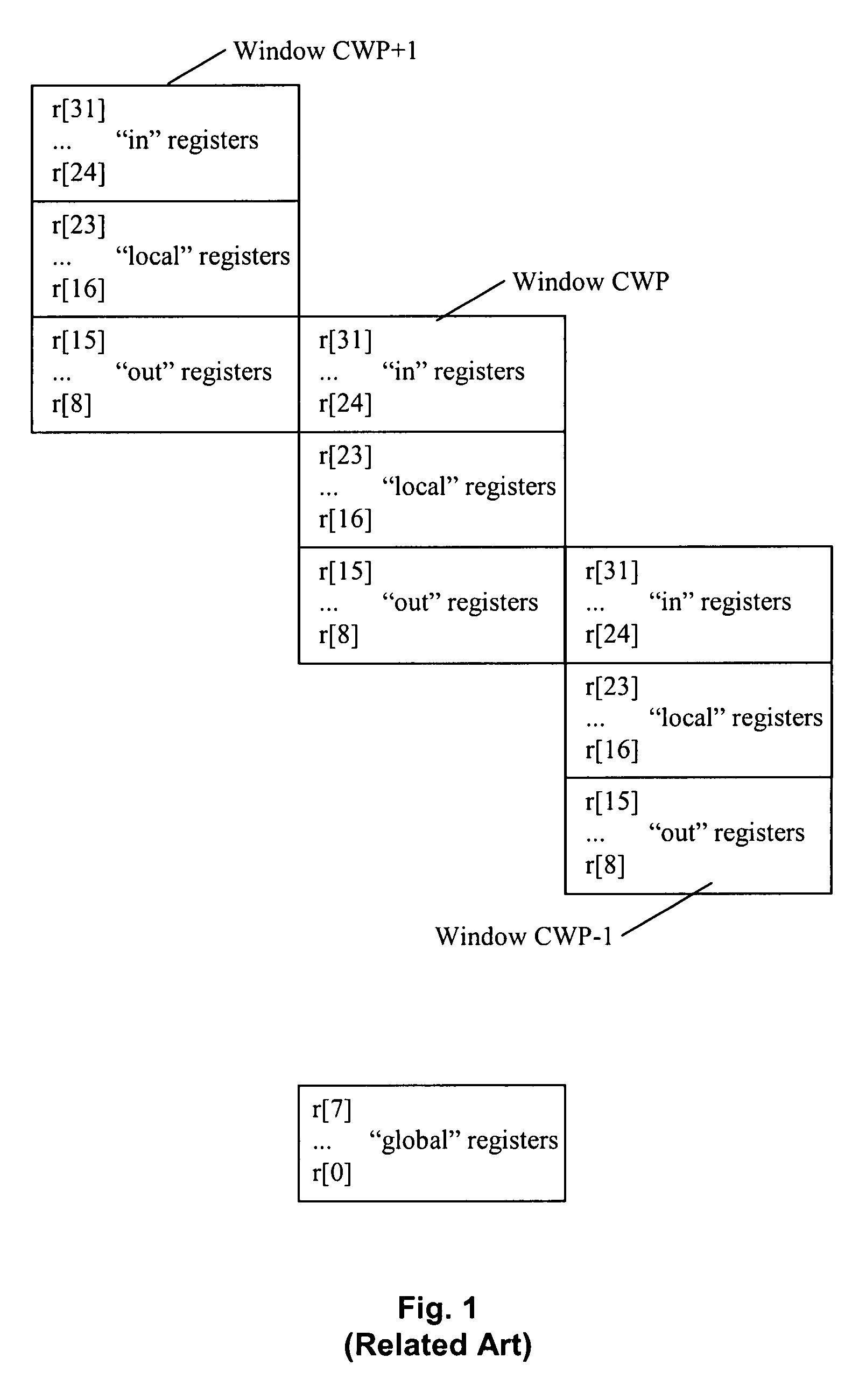

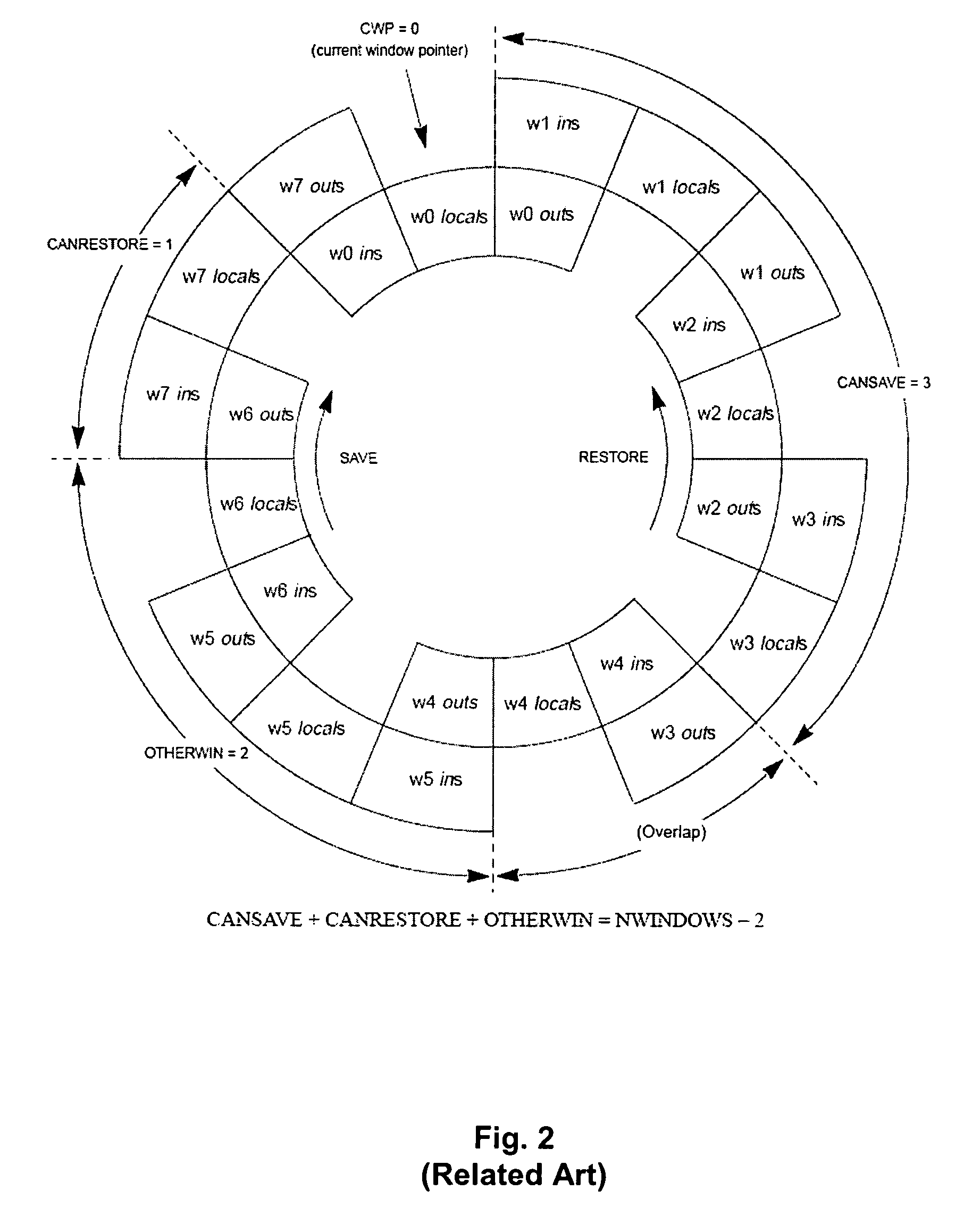

In computer engineering, register windows are a feature in some instruction set architectures to improve the performance of procedure calls, a very common operation. Register windows were one of the main features of the Berkeley RISC design, which would later be commercialized as the AMD Am29000, Intel i960, Sun Microsystems SPARC, and Intel Itanium.

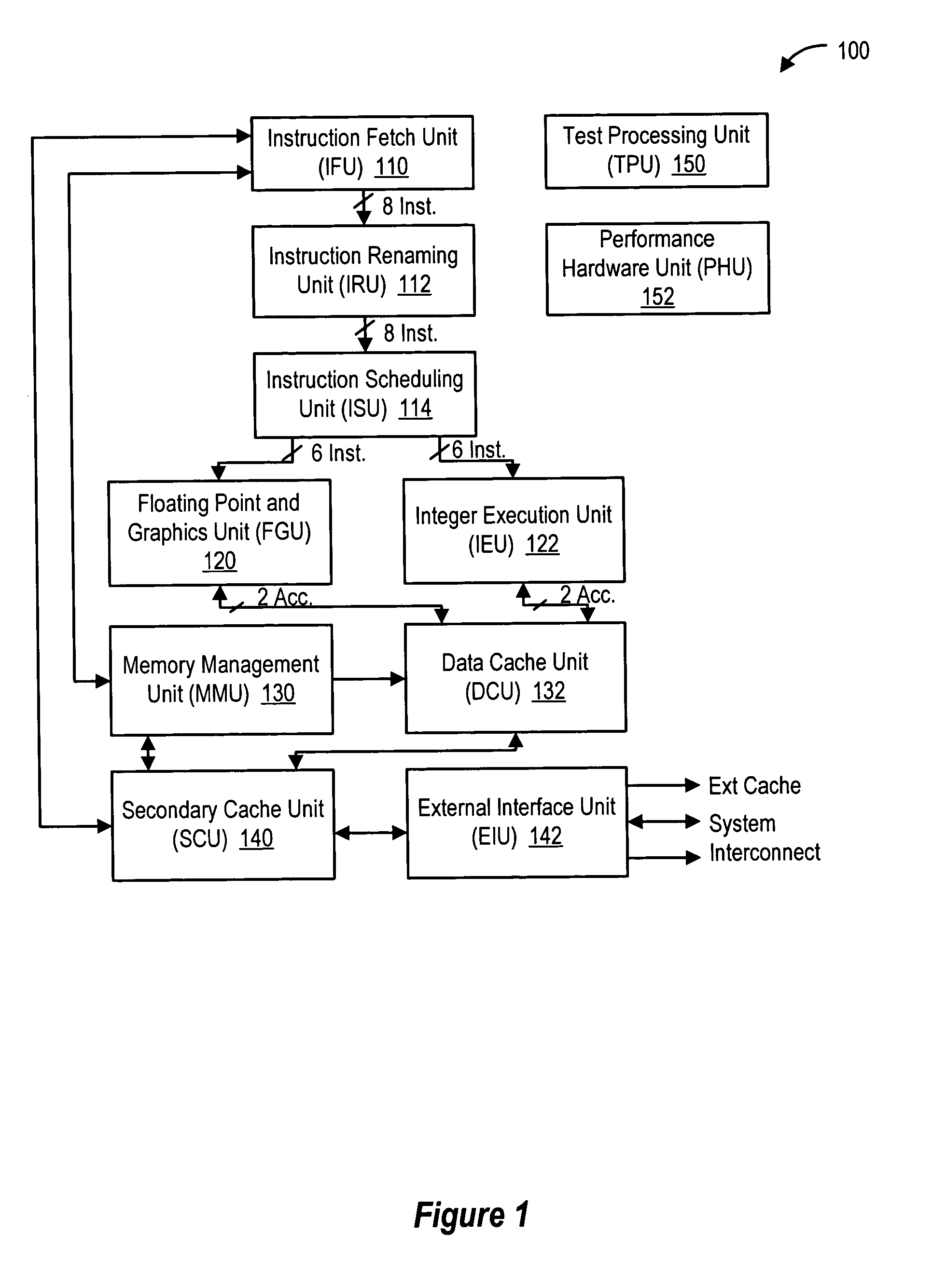

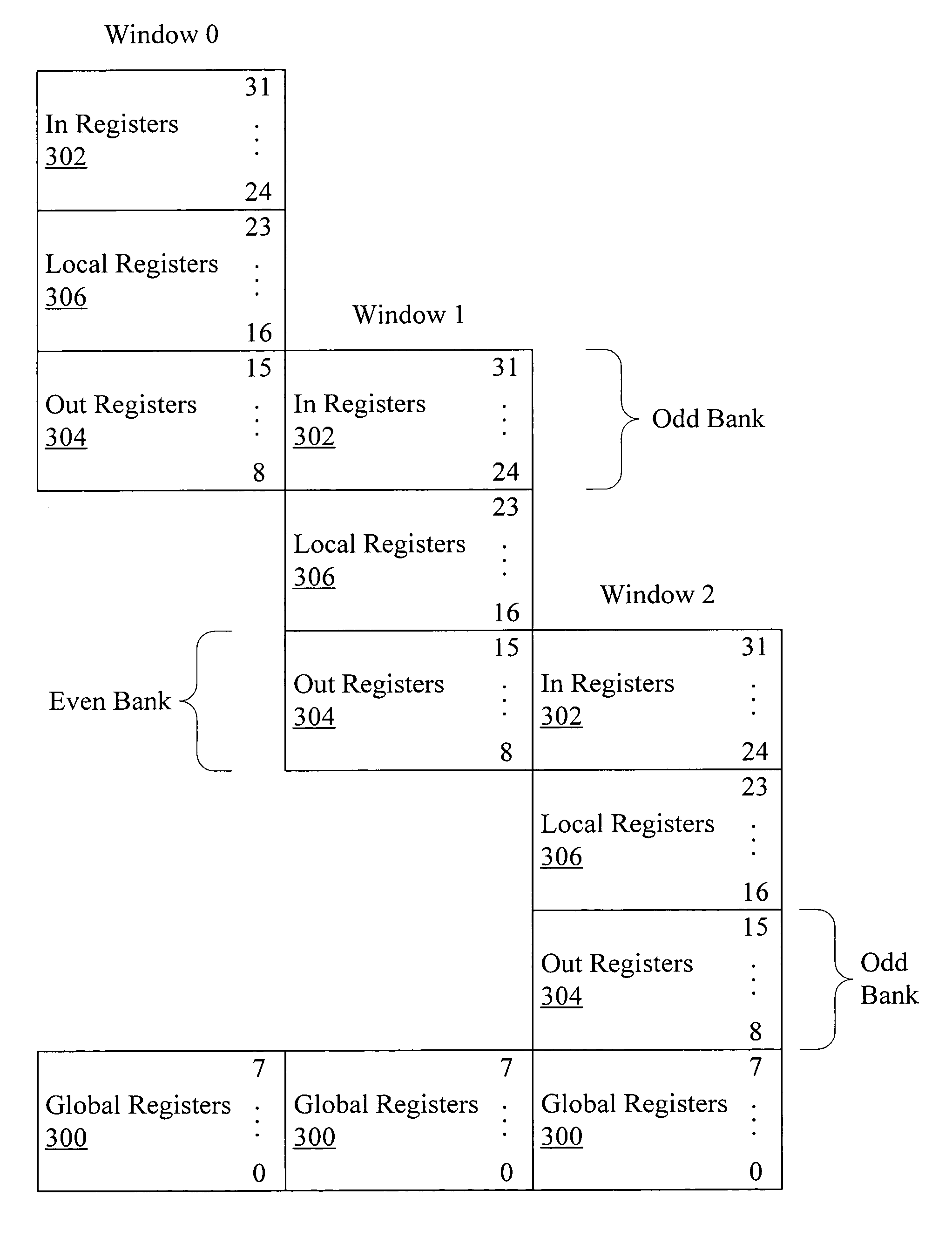

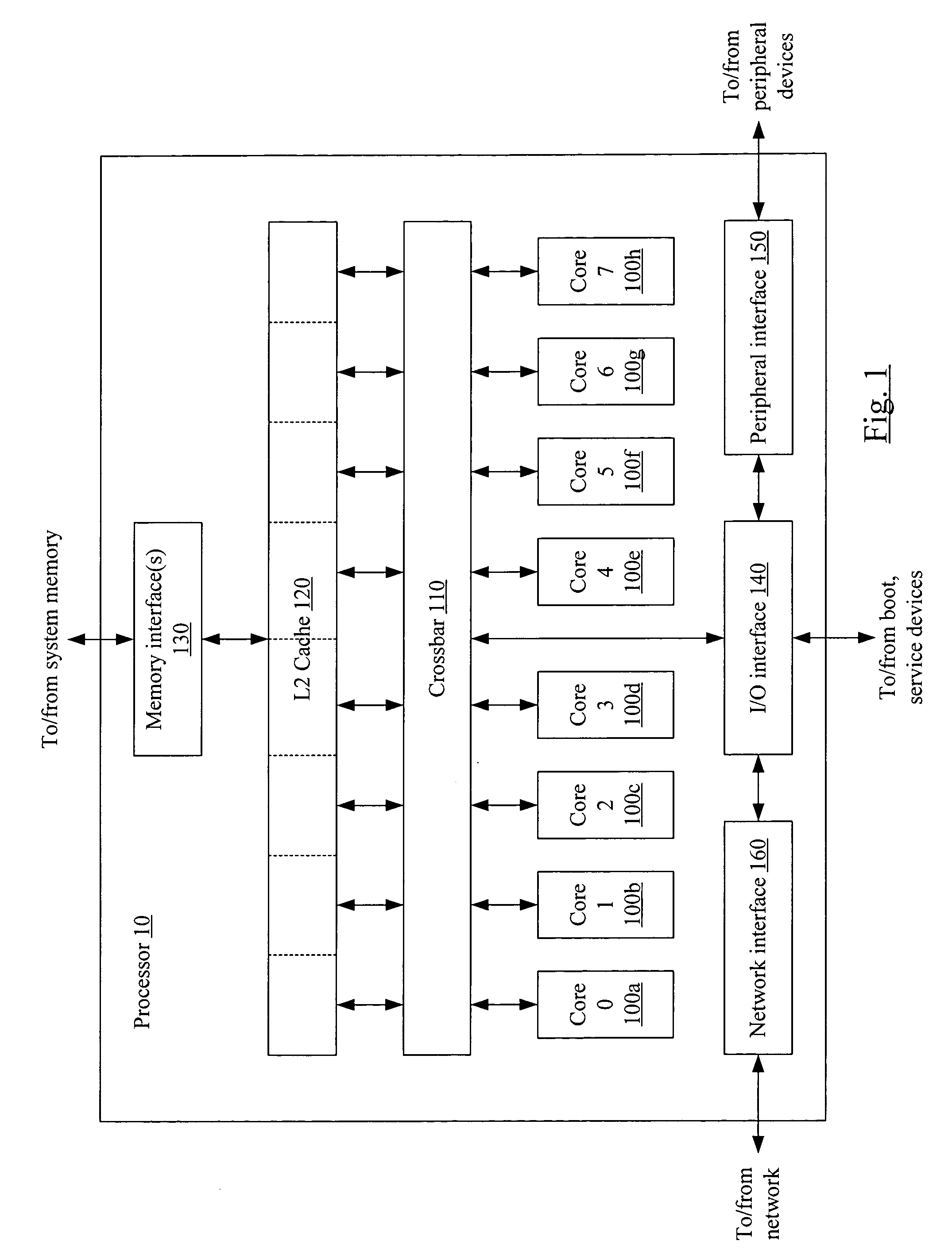

Versatile register file design for a multi-threaded processor utilizing different modes and register windows

ActiveUS7418582B1Improve performanceRegister arrangementsDigital computer detailsFile designRegister window

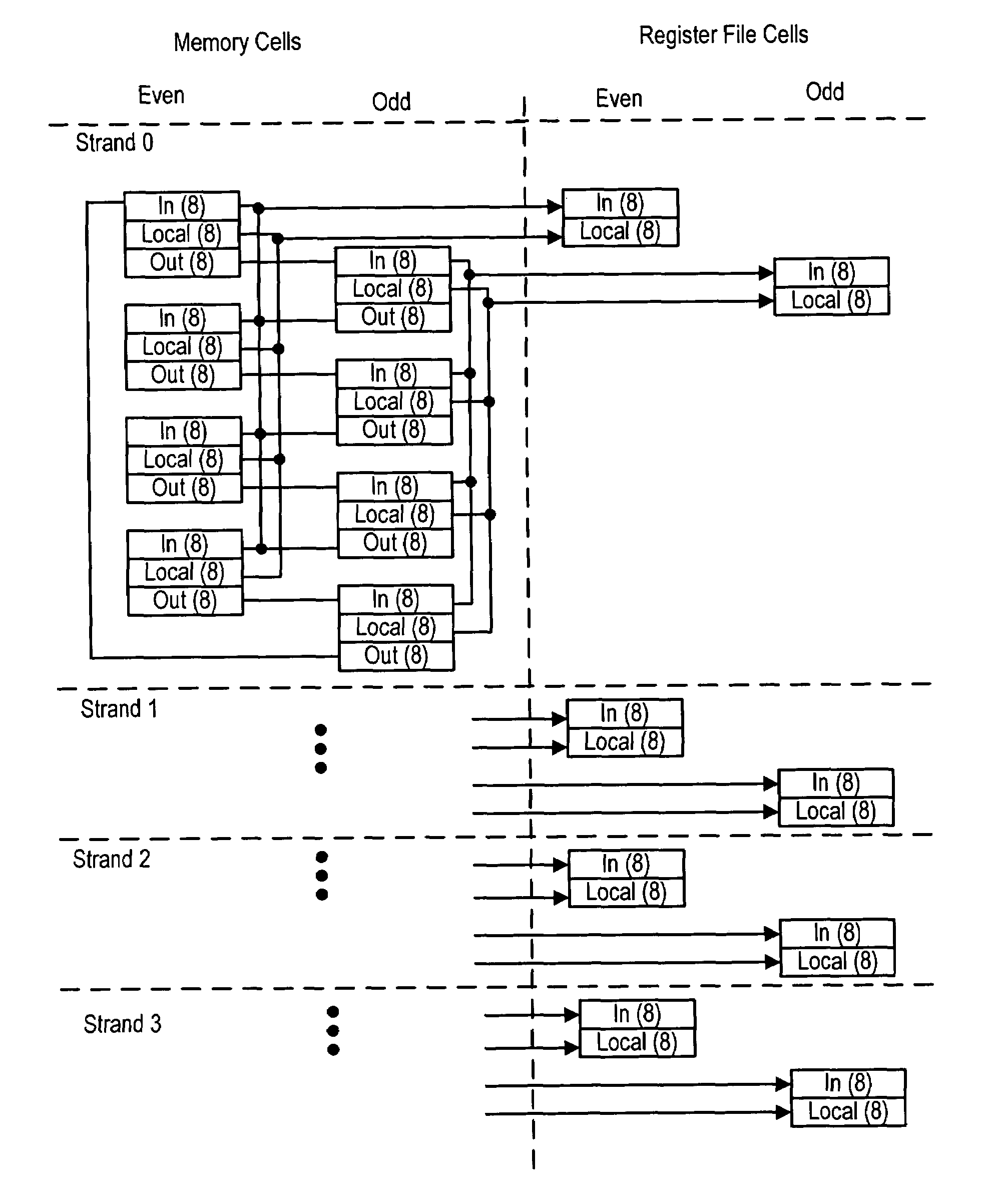

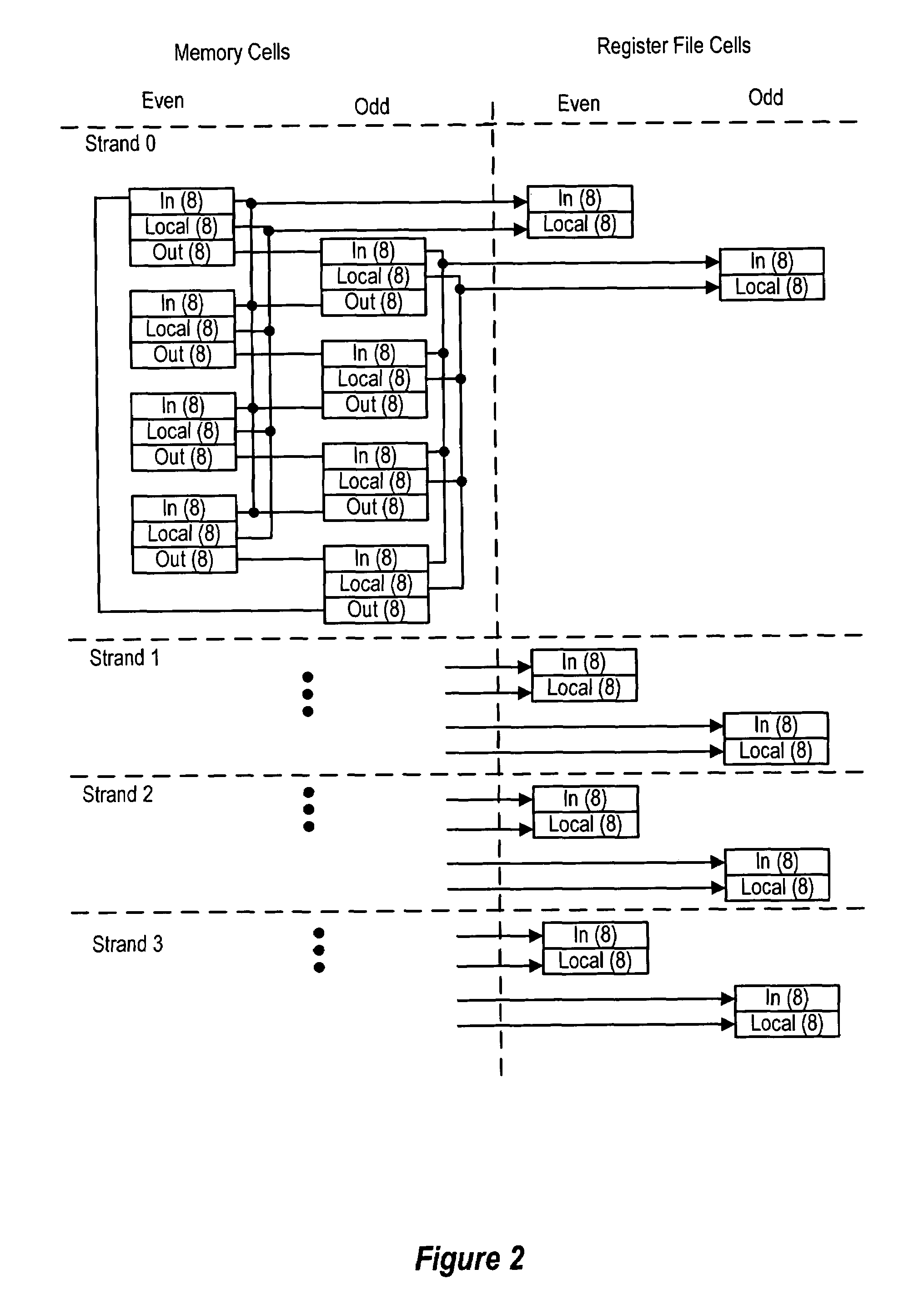

A method for optimizing a register file hierarchy in a multithreaded processor. The method includes providing a register file hierarchy with a plurality of register file cells, associating the plurality of register file cells with respective threads when the processor is operating in a multithreaded mode and flattening the plurality of register file cells with a single thread when the processor is operating in a single threaded mode. The register file cells correspond to threads of the multithreaded processor.

Owner:ORACLE INT CORP

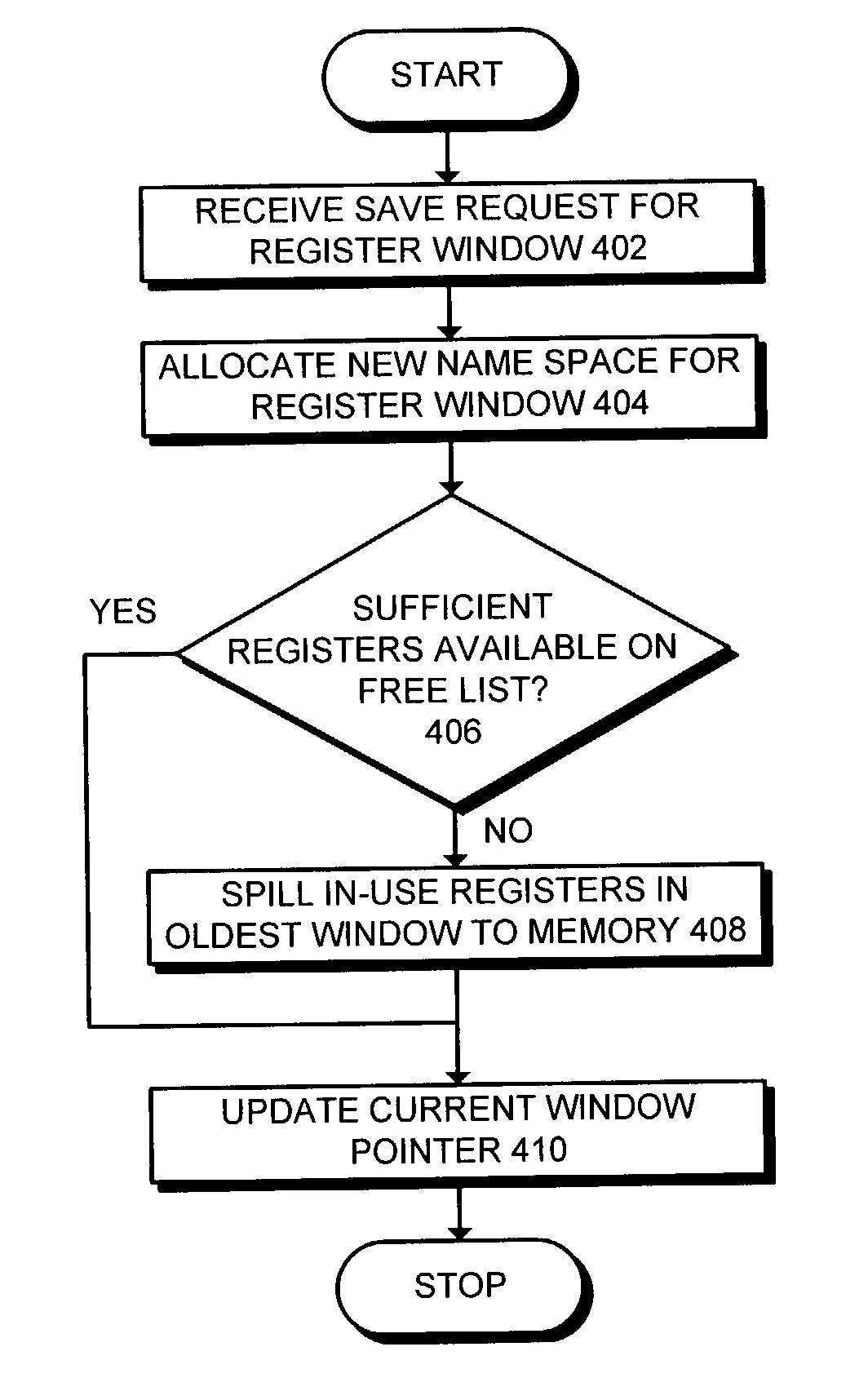

Method and apparatus for dynamically allocating registers in a windowed architecture

ActiveUS7127592B2Digital computer detailsConcurrent instruction executionRegister windowRegister file

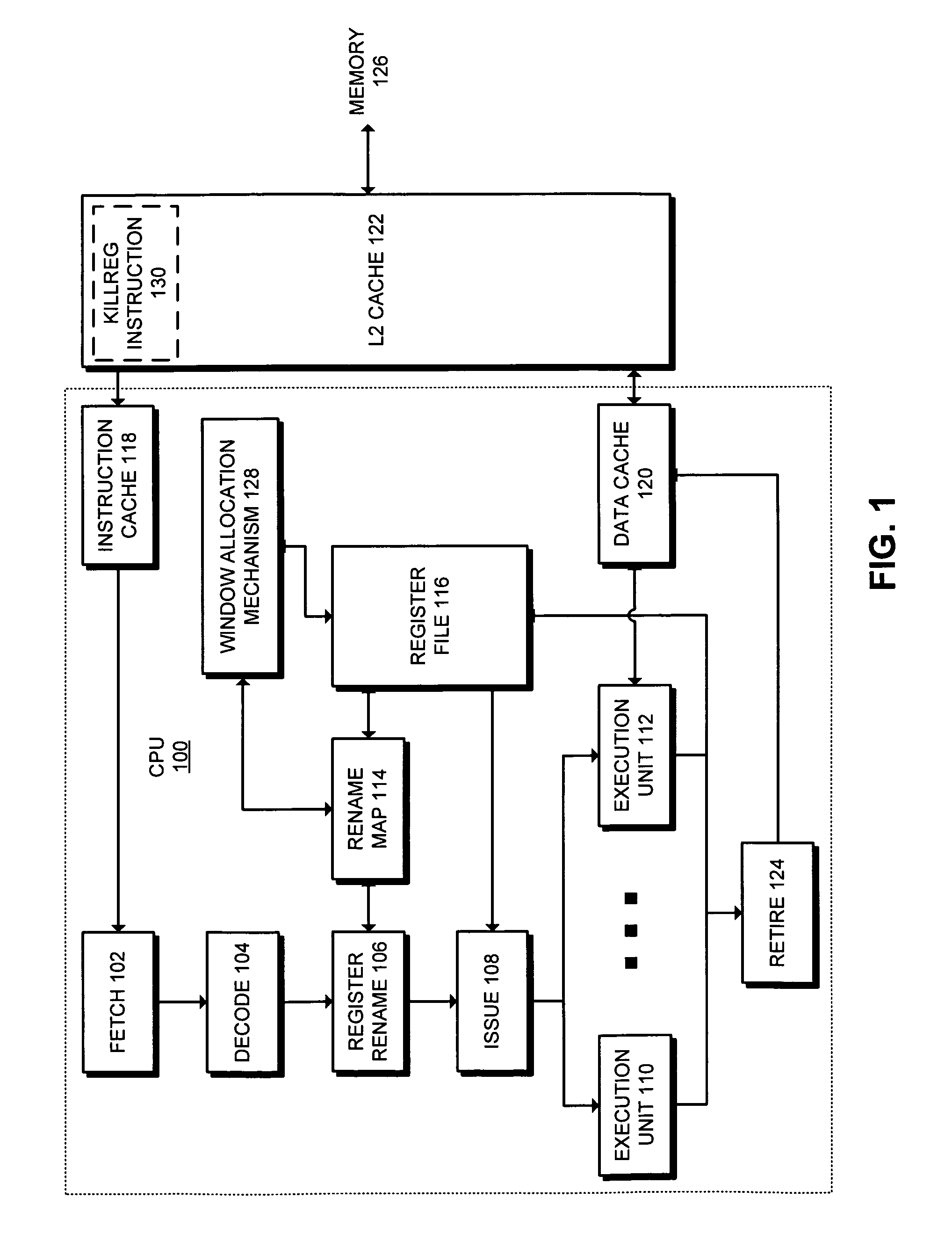

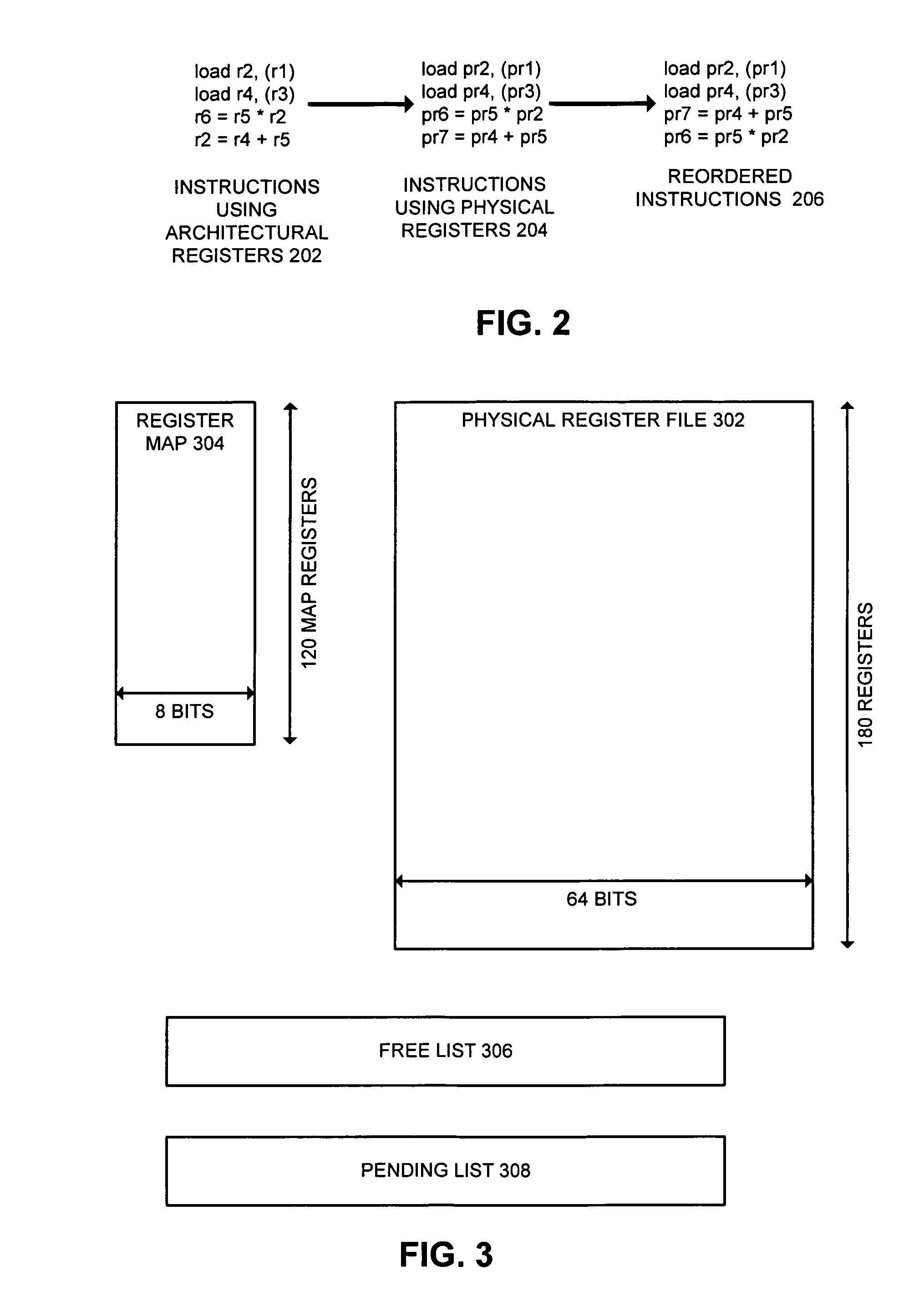

One embodiment of the present invention provides a system that dynamically allocates physical registers in a windowed processor architecture. The system includes a physical register file and a register map that maps architectural registers defined within an executing program to physical registers within the physical register file. The system also includes a window allocation mechanism that allocates a new name space for a register window without allocating physical registers for the register window, thereby allowing the physical registers to be dynamically allocated as needed instead of being allocated at window initialization time.

Owner:ORACLE INT CORP

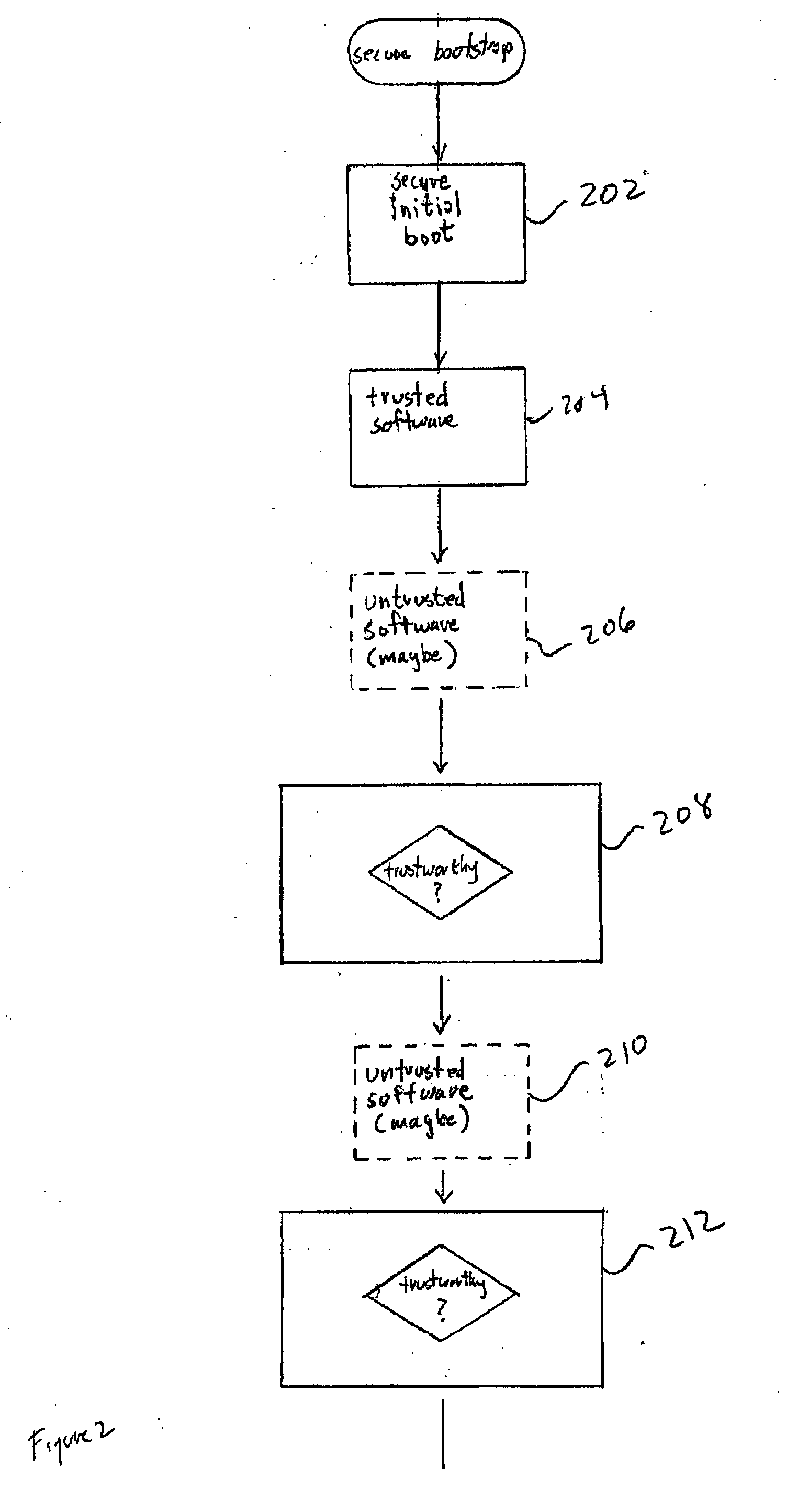

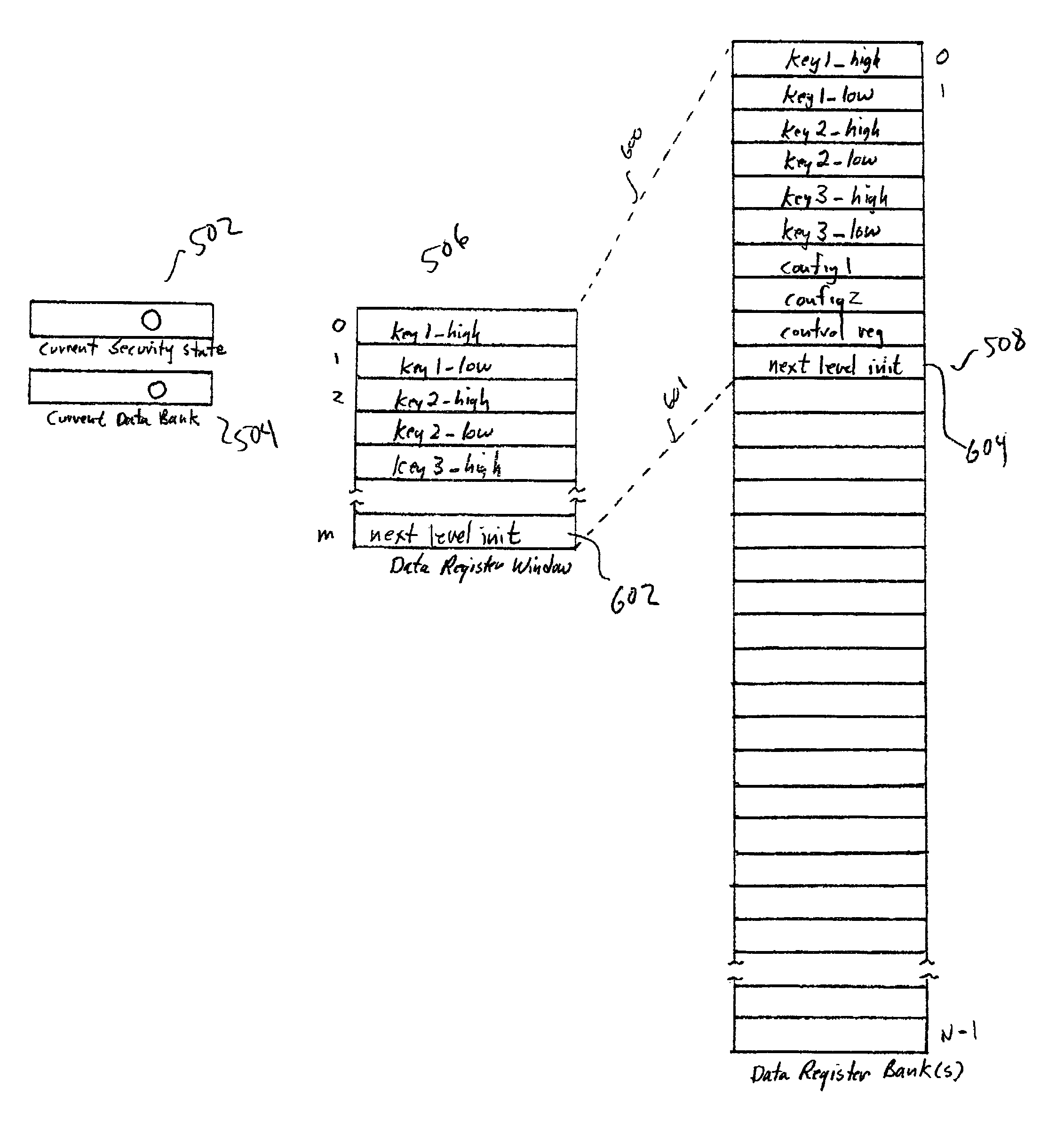

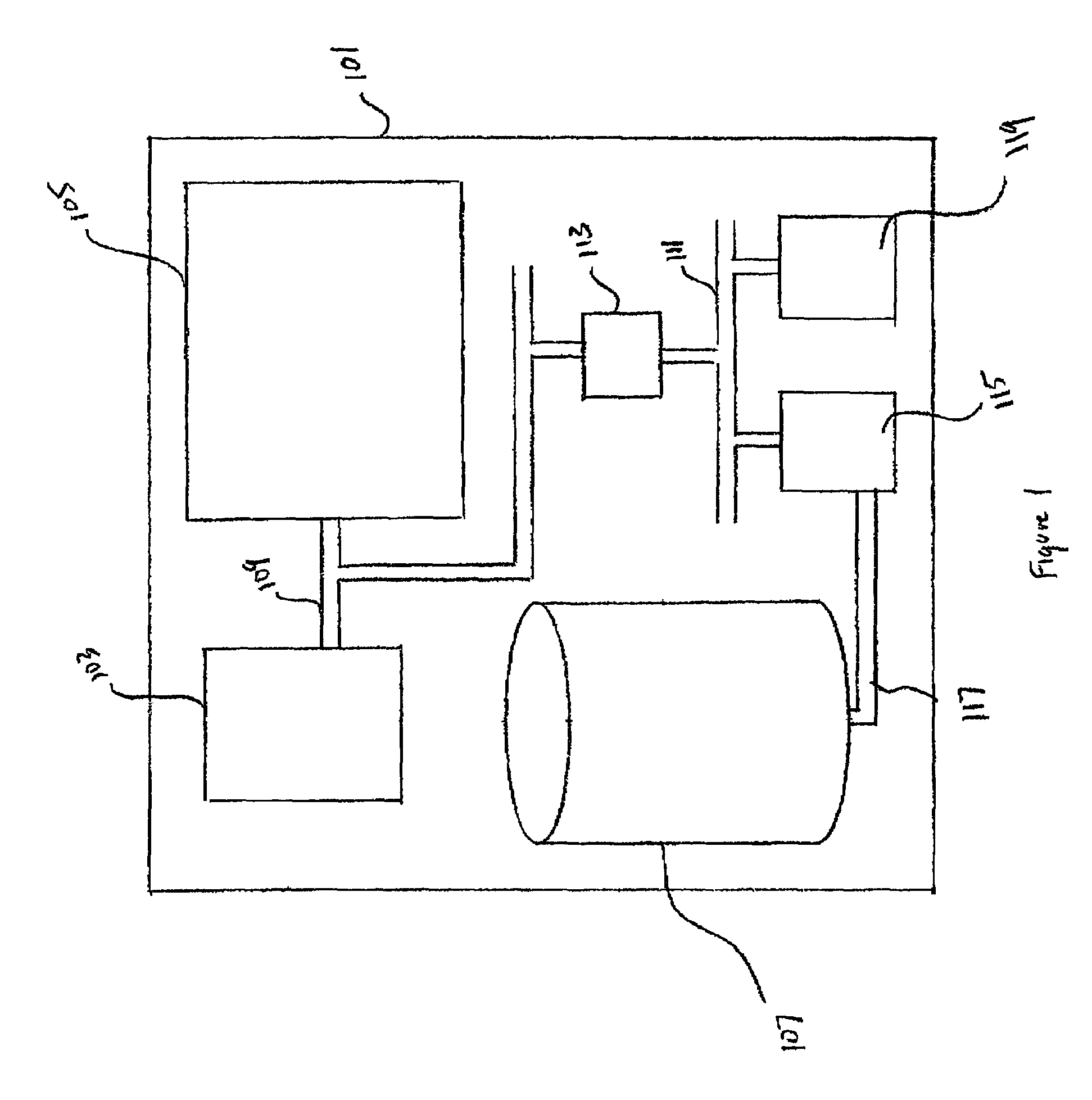

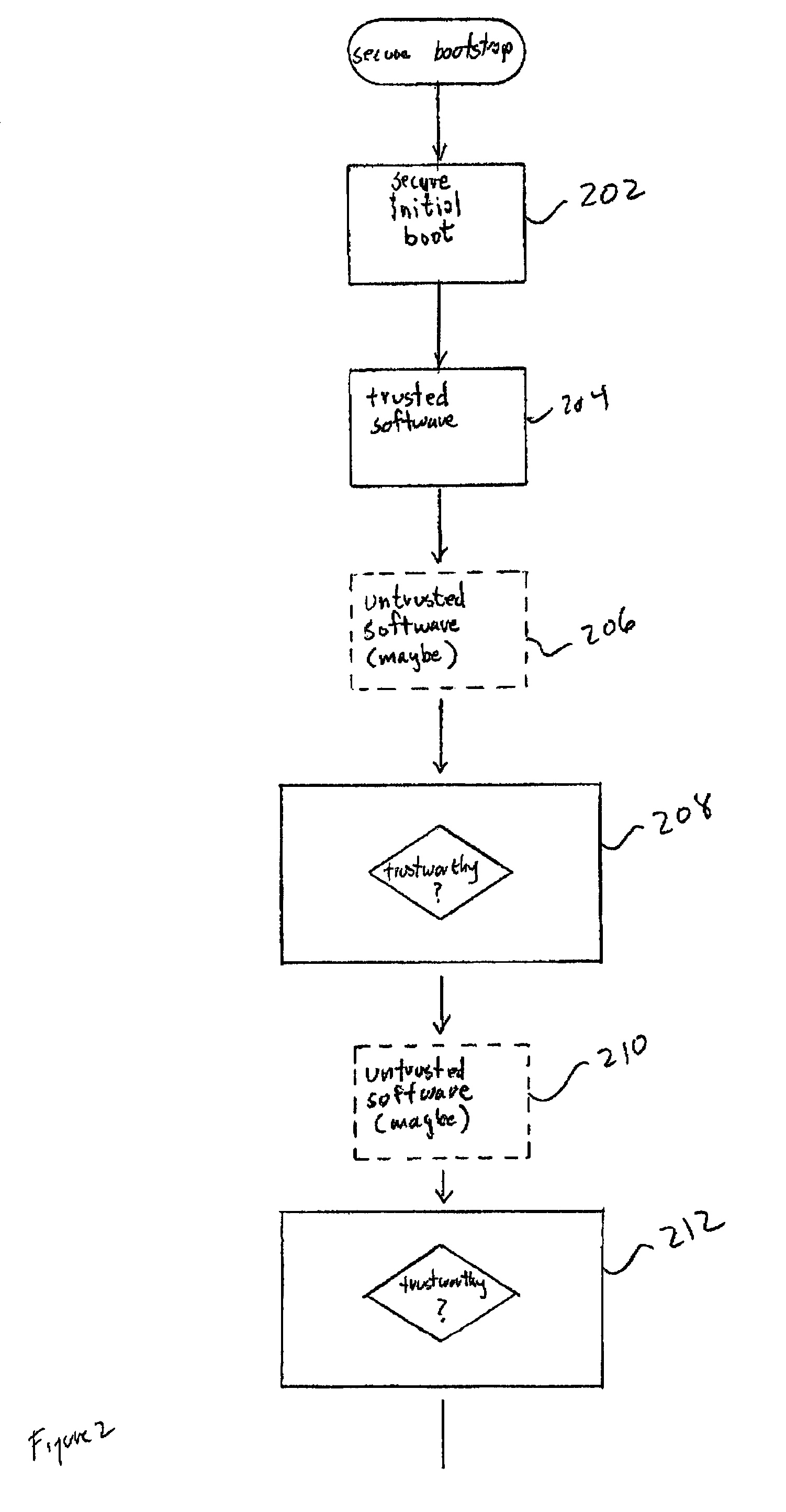

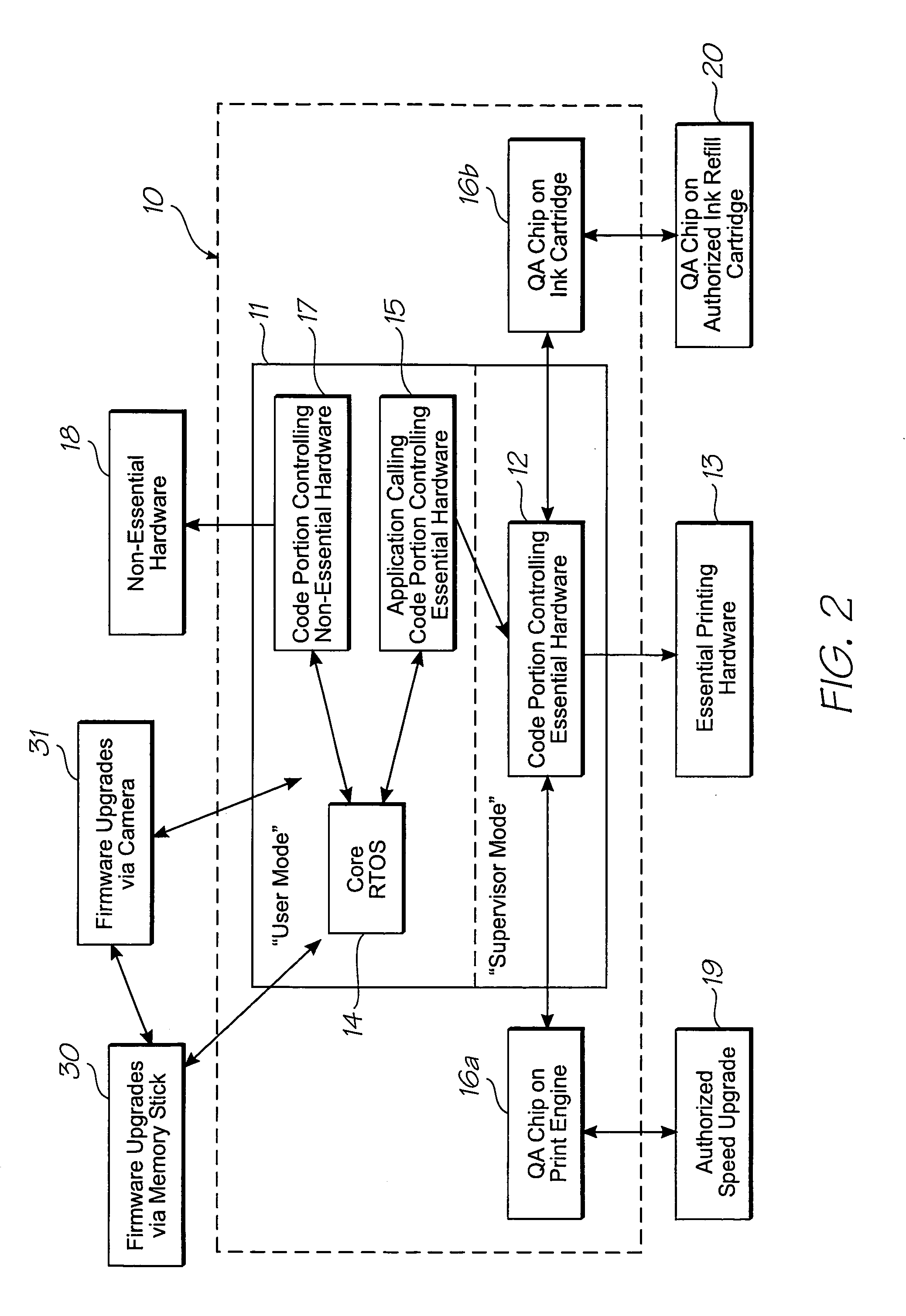

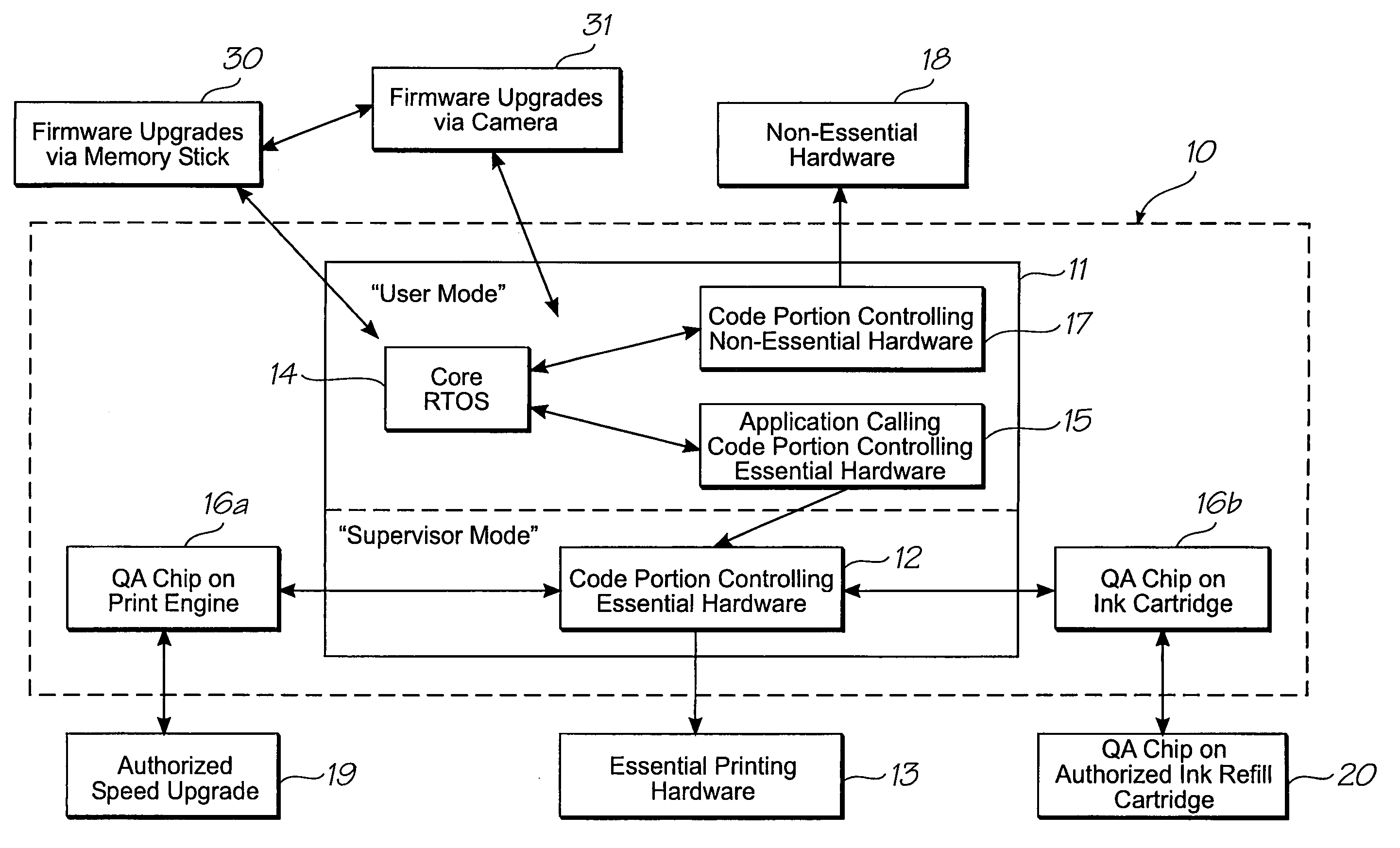

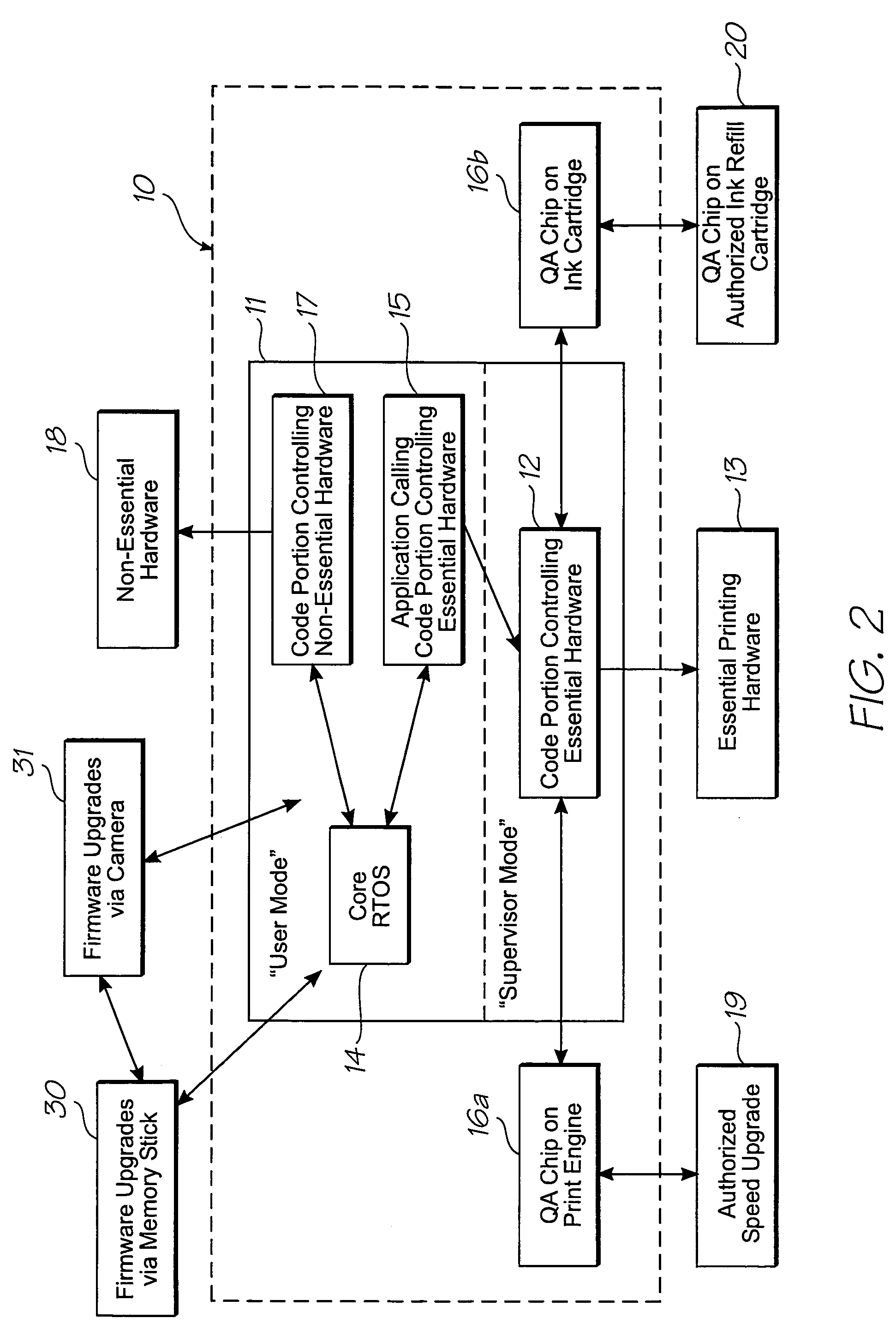

Method and system for securing a computer system

InactiveUS20050033978A1Digital data processing detailsAnalogue secracy/subscription systemsRegister windowControl register

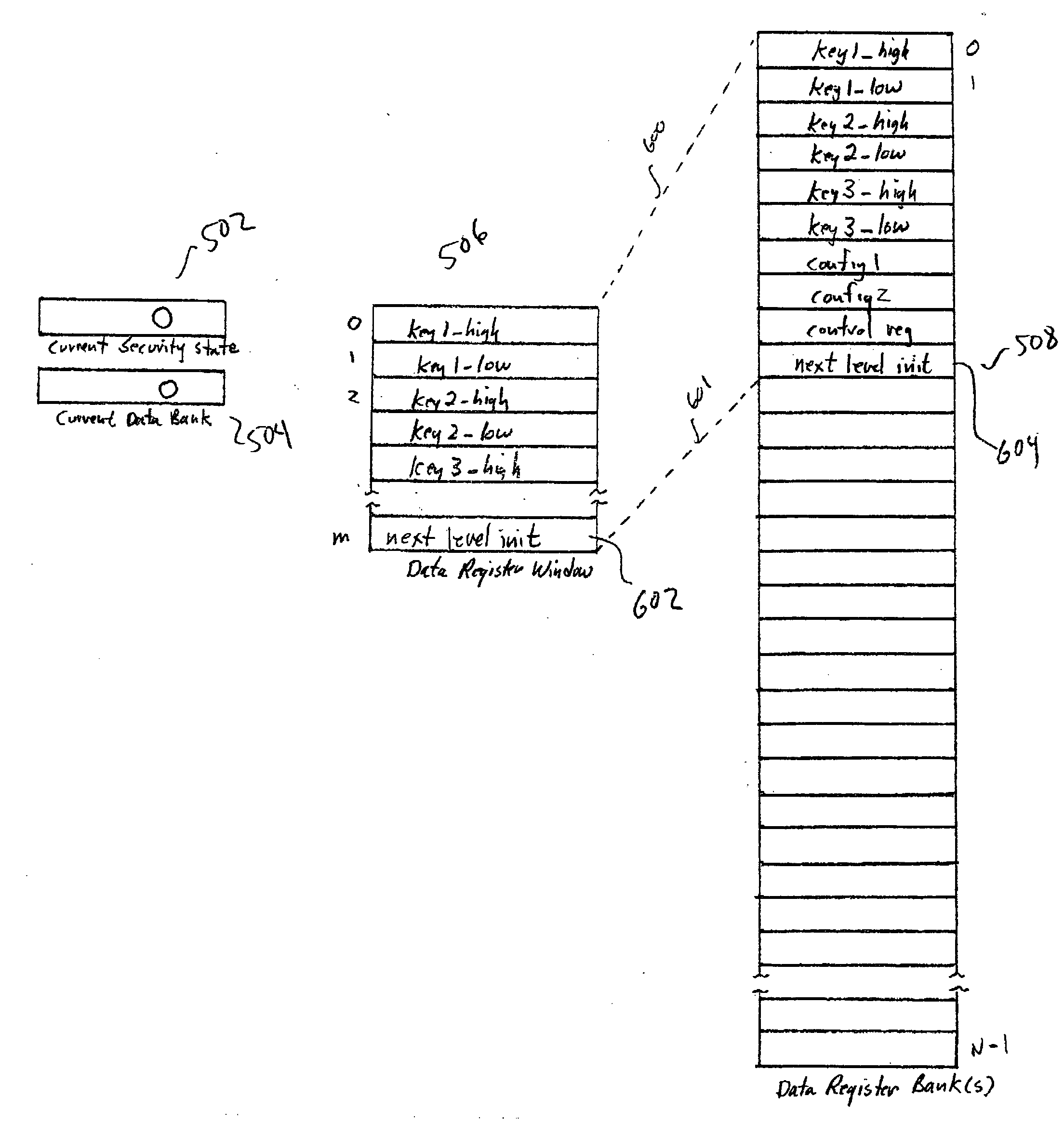

Security-state-reporting and data-control functionality introduced into a computer system to monitor and report the security state of the computer system and to store and make selectively available, for processes executing within a computer system, security-state-associated data. The hardware element includes two control registers, a current-security-state control register (“CSS”) and a current-data-bank control register (“CDB”). When the CSS is read, the CSS reports the current security state of the computer system, with security states represented as unsigned integers starting from a highest security level of 0 and decreasing with unsigned integers of increasing magnitudes. The CDB controls access to one or more data-register banks, positioning a data-register window to allow access only to those data-register-bank registers associated with the currently reported security state.

Owner:GOOGLE LLC

Method and system for securing a computer system

InactiveUS7398390B2Digital data processing detailsAnalogue secracy/subscription systemsRegister windowControl register

Security-state-reporting and data-control functionality introduced into a computer system to monitor and report the security state of the computer system and to store and make selectively available, for processes executing within a computer system, security-state-associated data. The hardware element includes two control registers, a current-security-state control register (“CSS”) and a current-data-bank control register (“CDB”). When the CSS is read, the CSS reports the current security state of the computer system, with security states represented as unsigned integers starting from a highest security level of 0 and decreasing with unsigned integers of increasing magnitudes. The CDB controls access to one or more data-register banks, positioning a data-register window to allow access only to those data-register-bank registers associated with the currently reported security state.

Owner:GOOGLE LLC

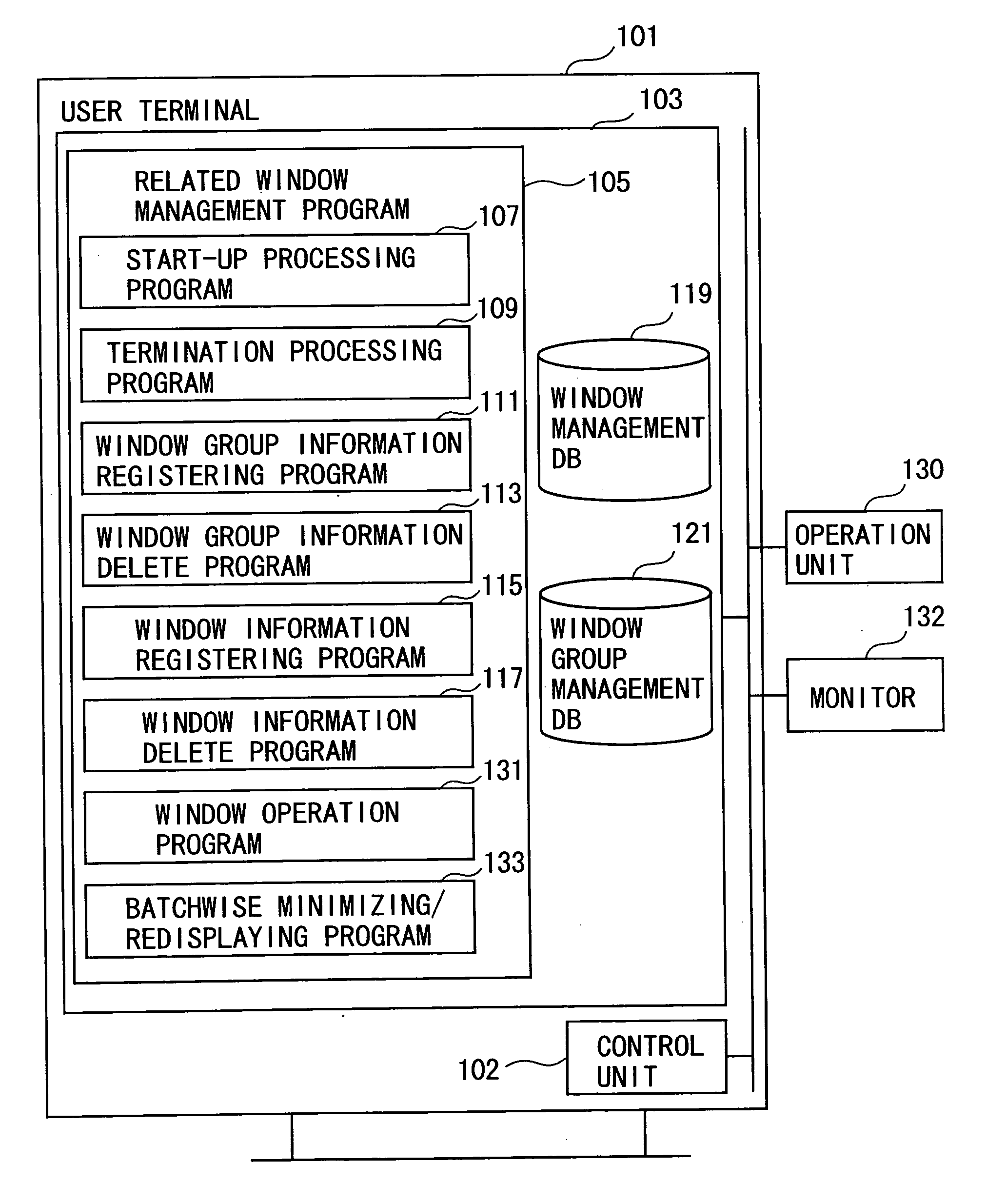

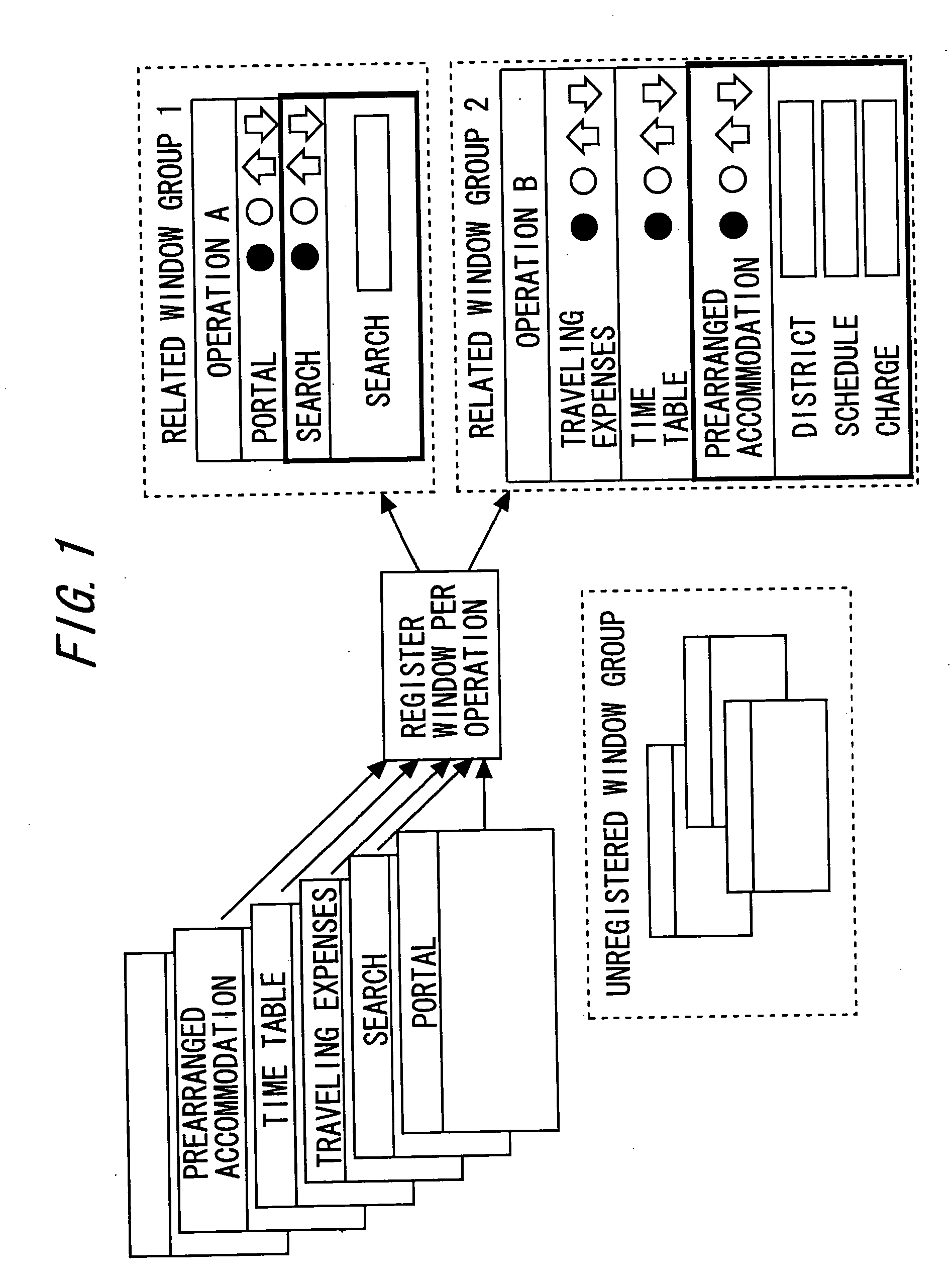

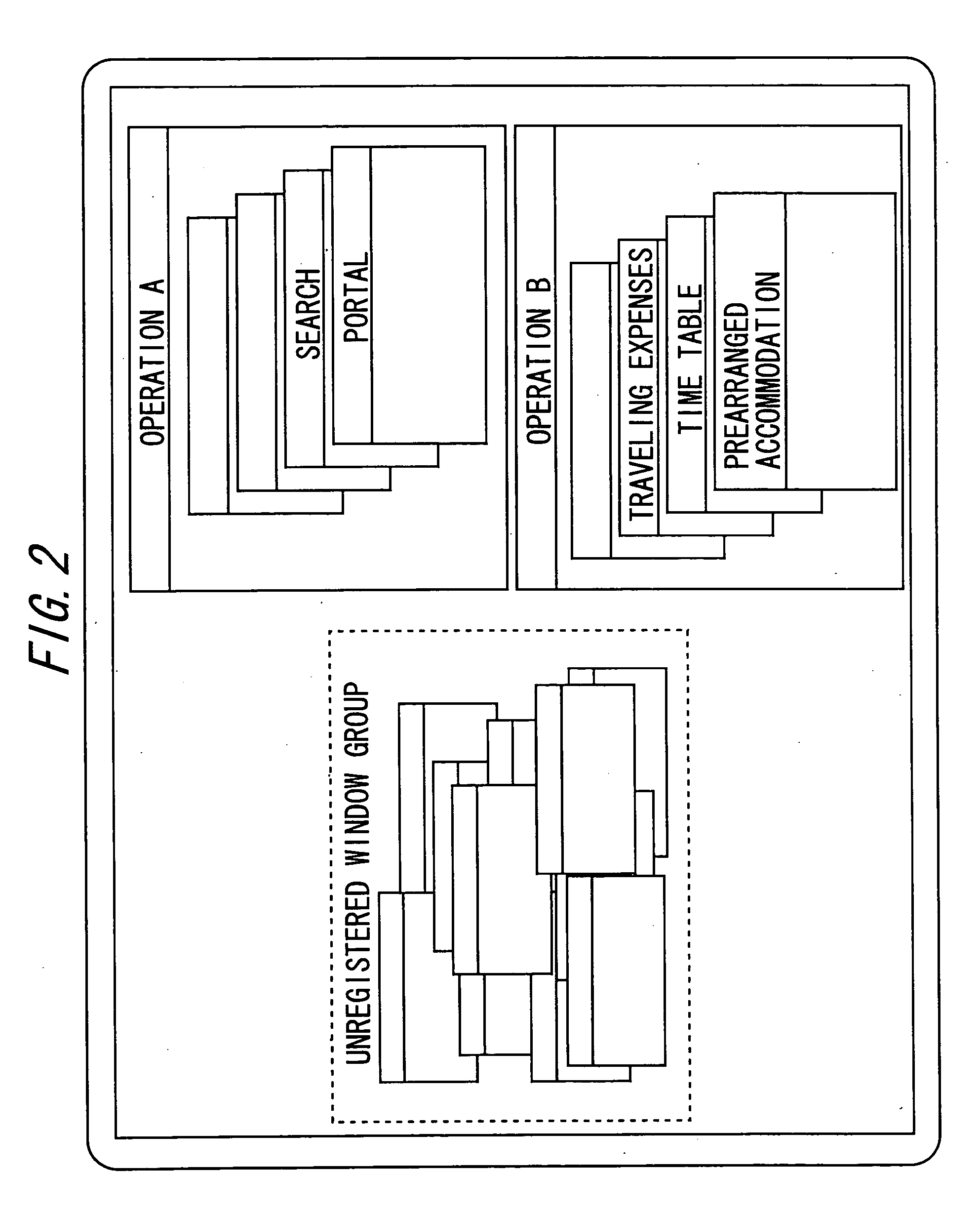

Window management system

InactiveUS20050216918A1Quick identificationMinimizing displayCathode-ray tube indicatorsExecution for user interfacesRegister windowData mining

A control unit 102 registers window group information associated with each window group on a window group management DB 121, and registers window information associated with each window on a window management DB 119. Then, the control unit 102 executes a process related to the display of the window by a window-group basis on the window group information registered on the window group management DB 121 and the window information registered on the window management DB 119.

Owner:FUJITSU LTD

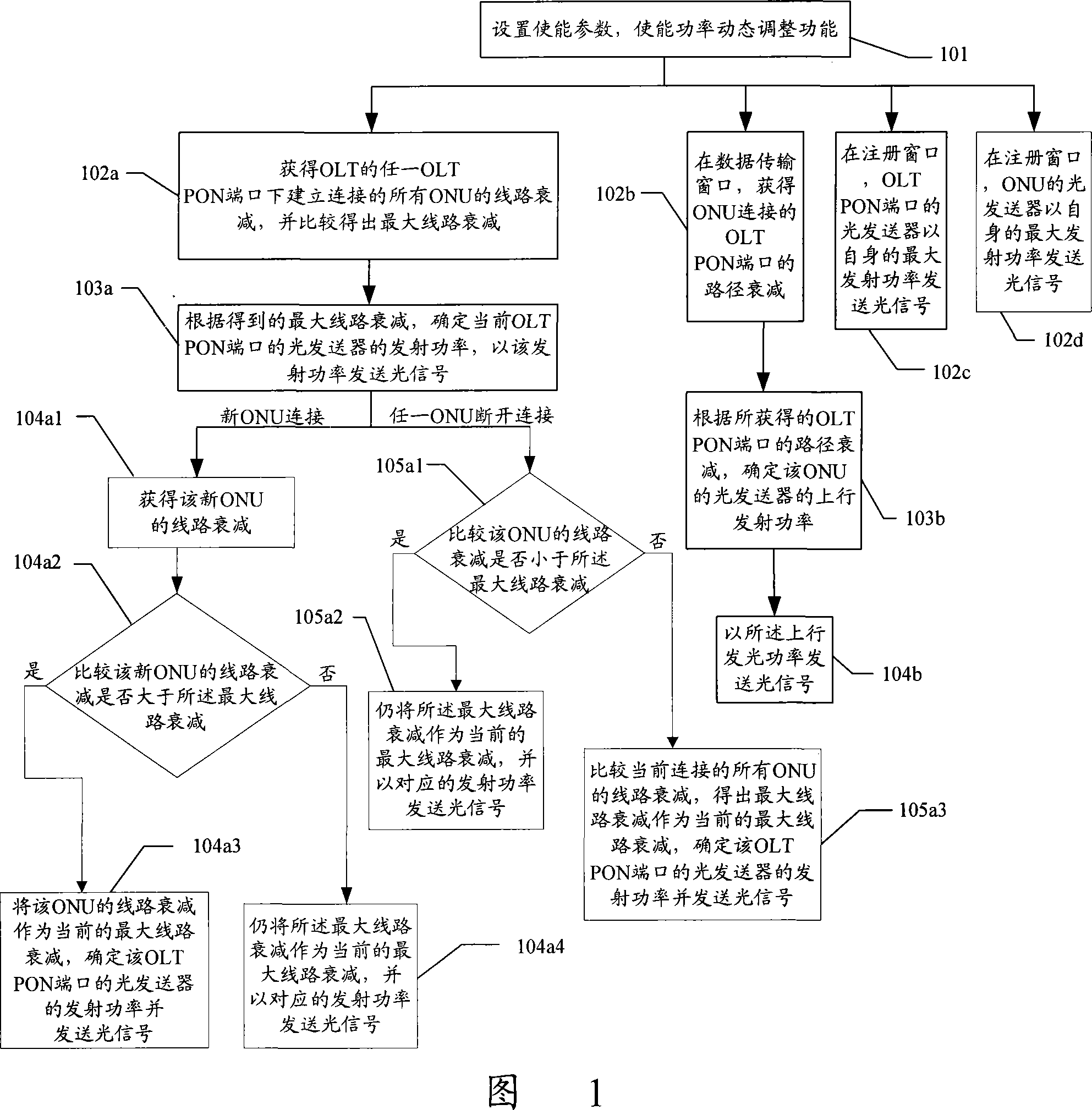

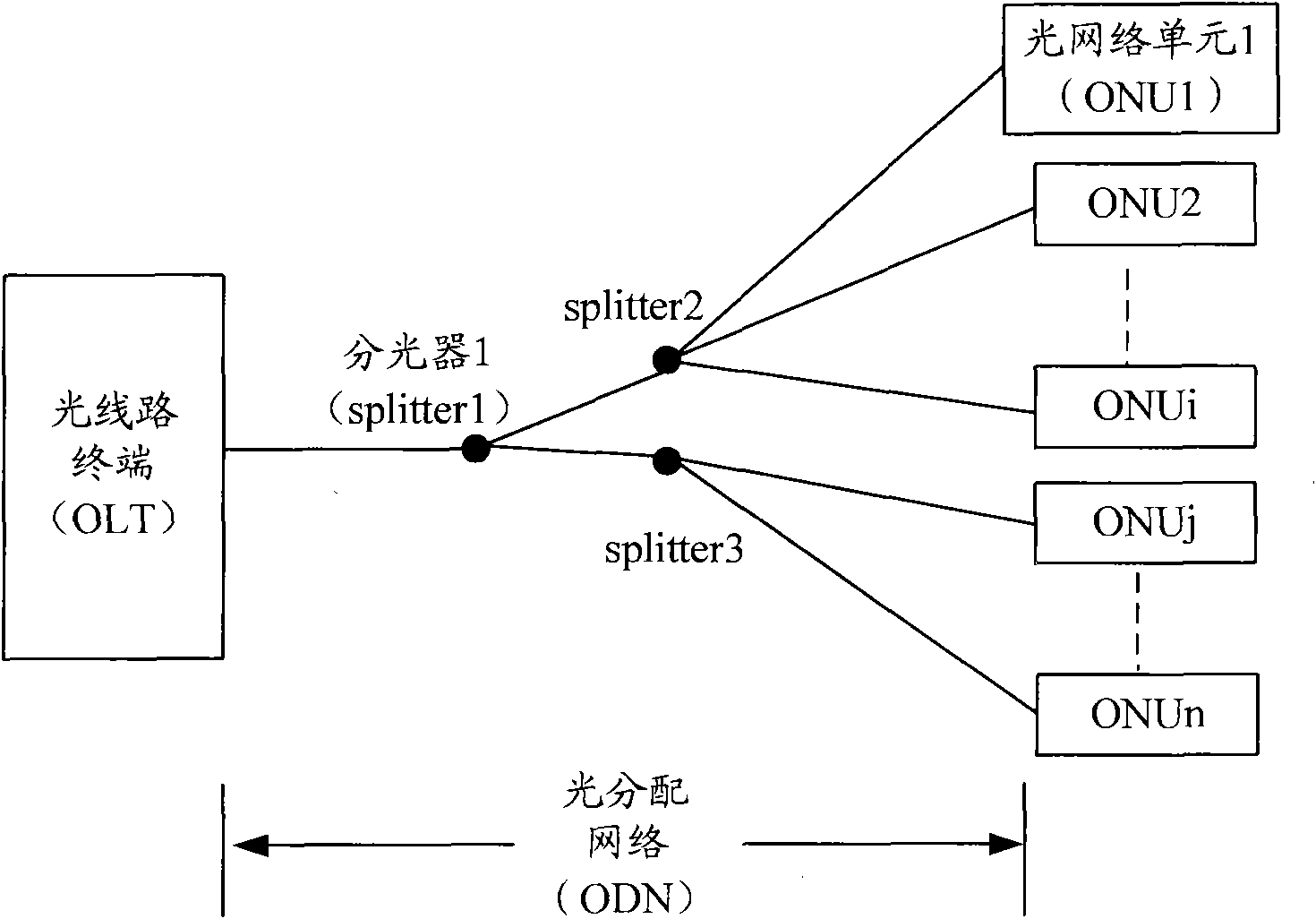

Power control method of passive optical network

ActiveCN101247182AReduce power lossRegistration successElectromagnetic transmissionRegister windowEngineering

The present invention discloses Power control method in passive optical network, light sender of OLTPON terminal port transmits light signal with self maximum emission power at register windows to assure all ONU register success successfully; all ONU with establishing connection below the OLTPON terminal port can steadily receives light signal transmitted from the OLTPON terminal port by dynamic adjusting emission power of light sender of OLTPON terminal port in data-transmission windows. Adopting method of the present invention can dynamic regulate light signal emission power of OLT and ONU in PON system, thereby power loss of PON system is decreased.

Owner:ZTE CORP

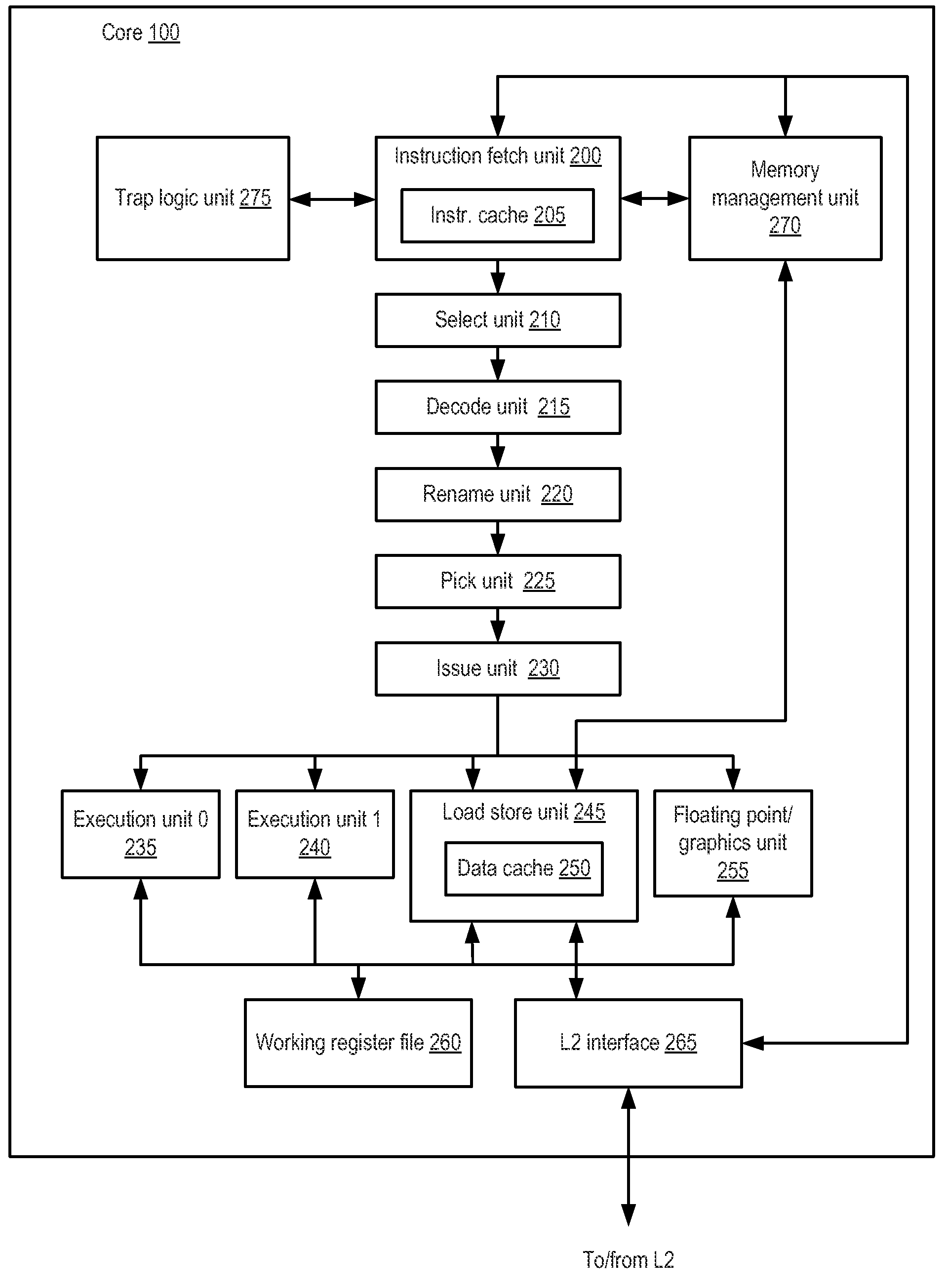

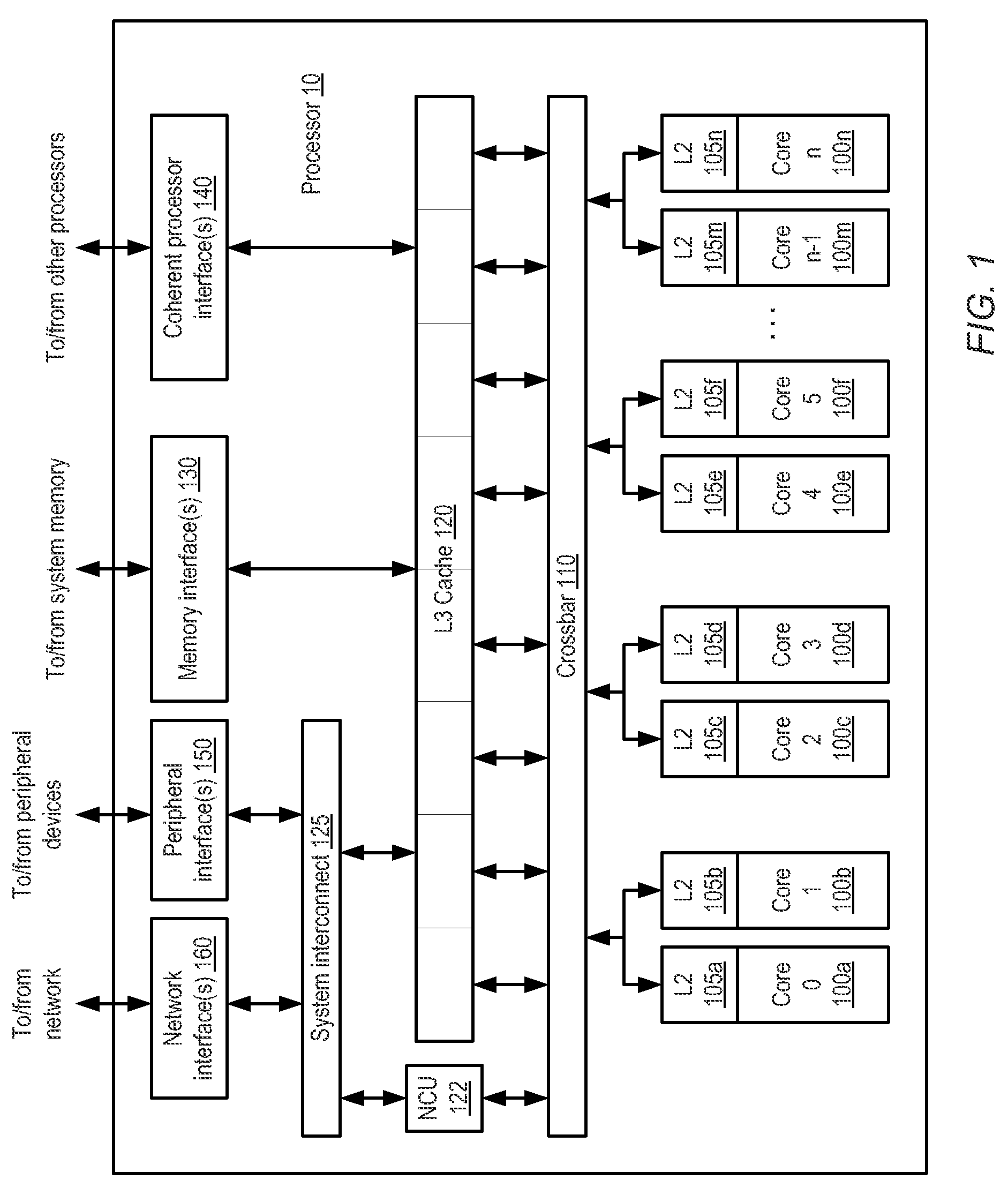

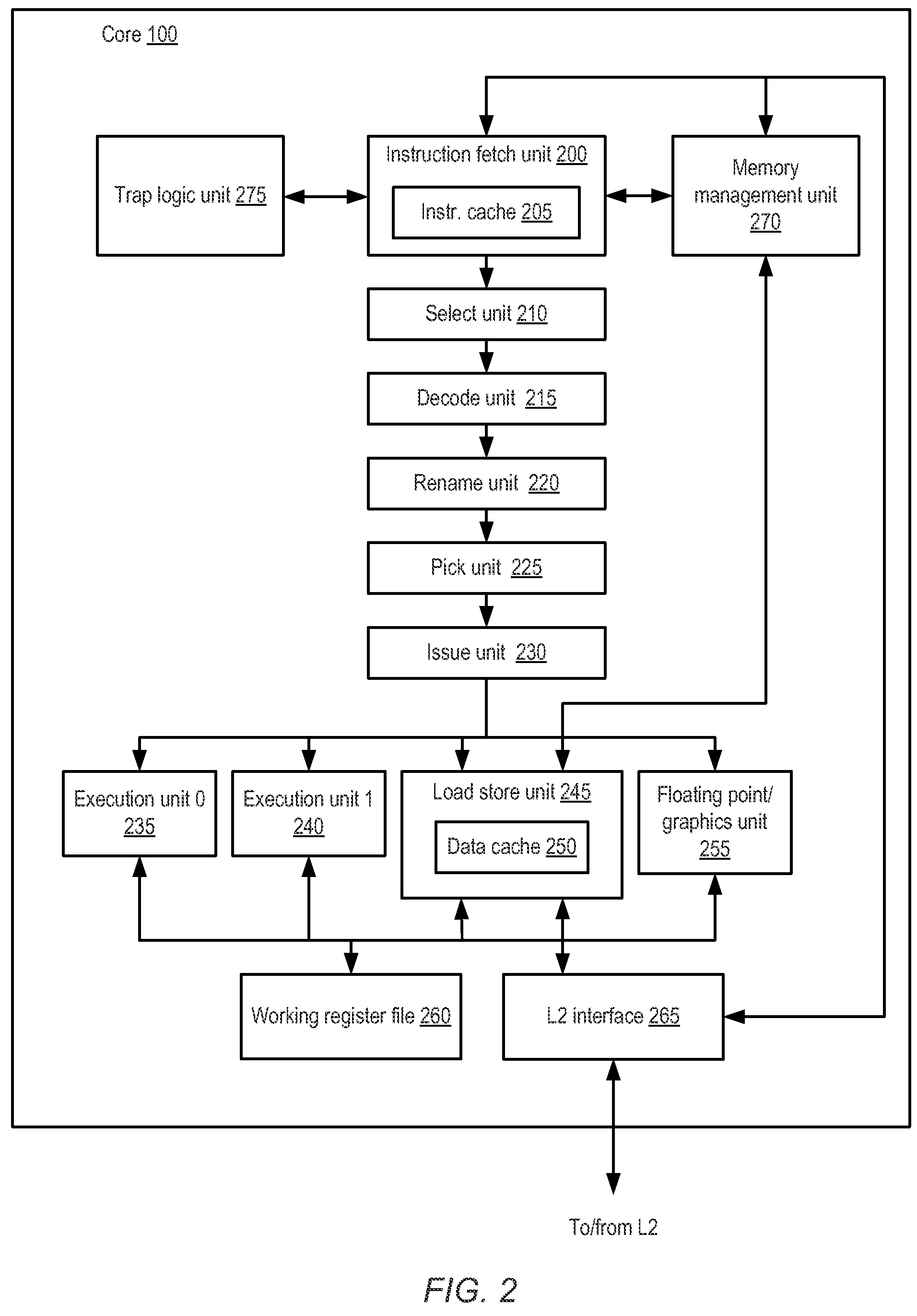

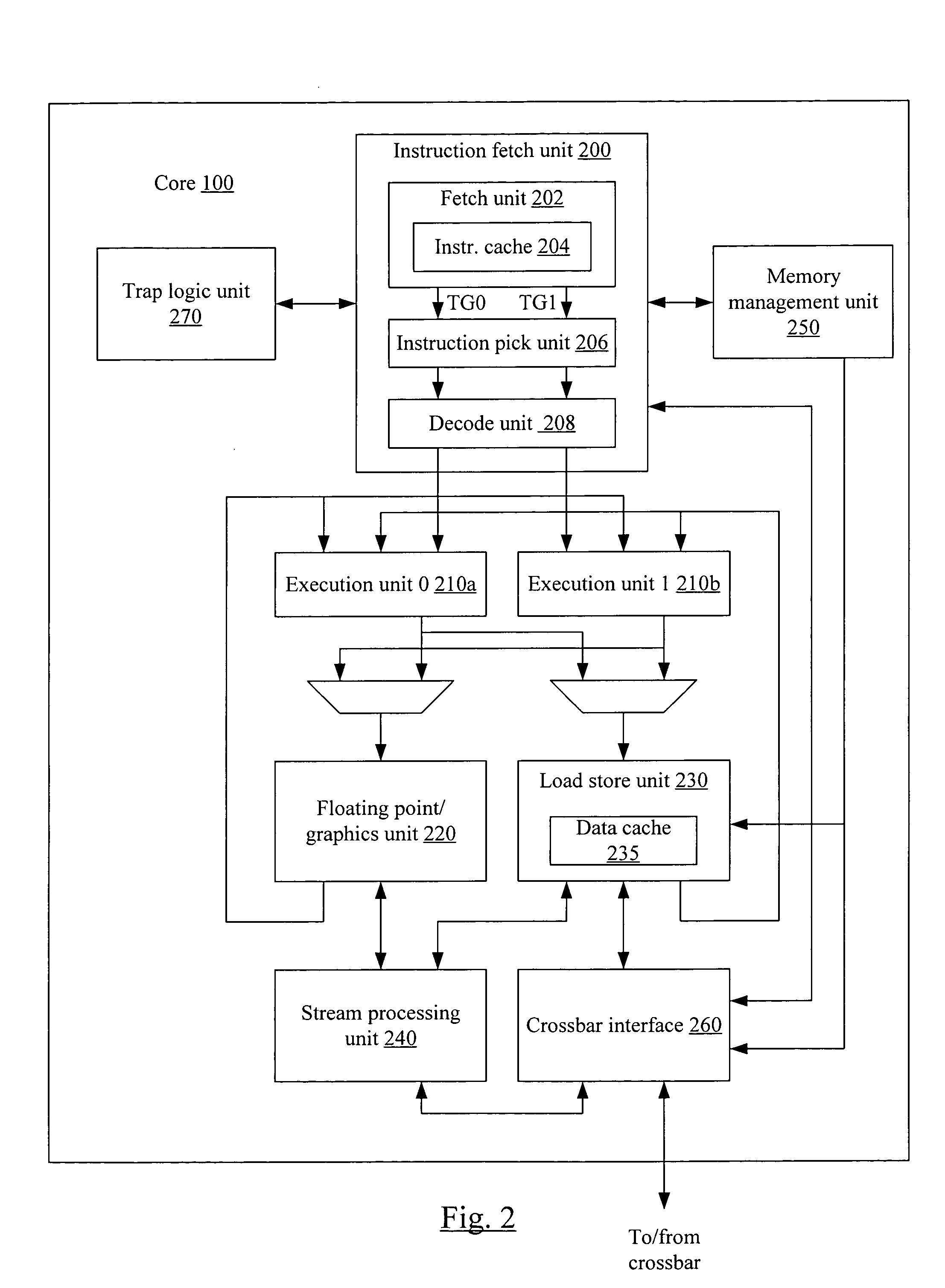

Multiported register file for multithreaded processors and processors employing register windows

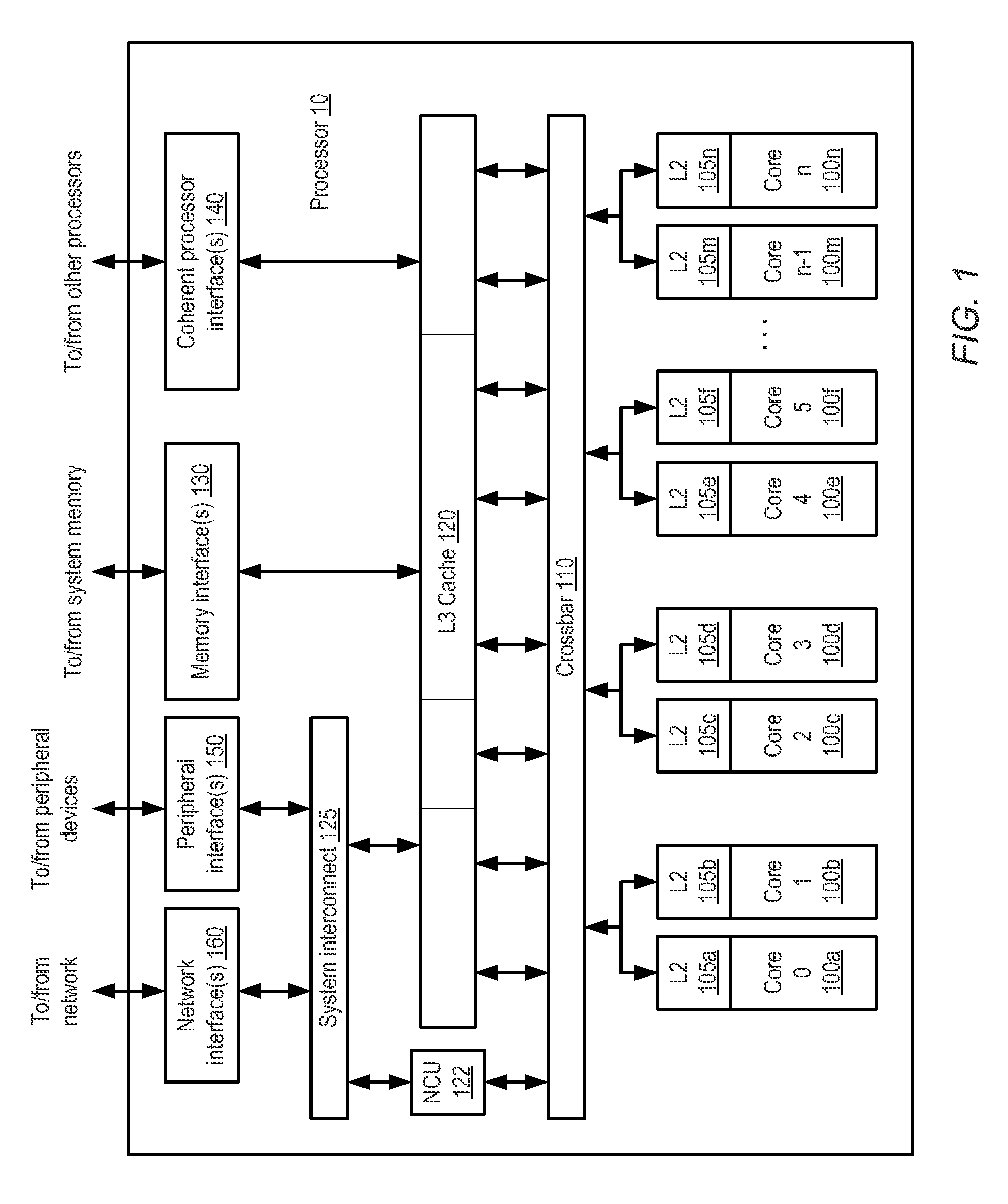

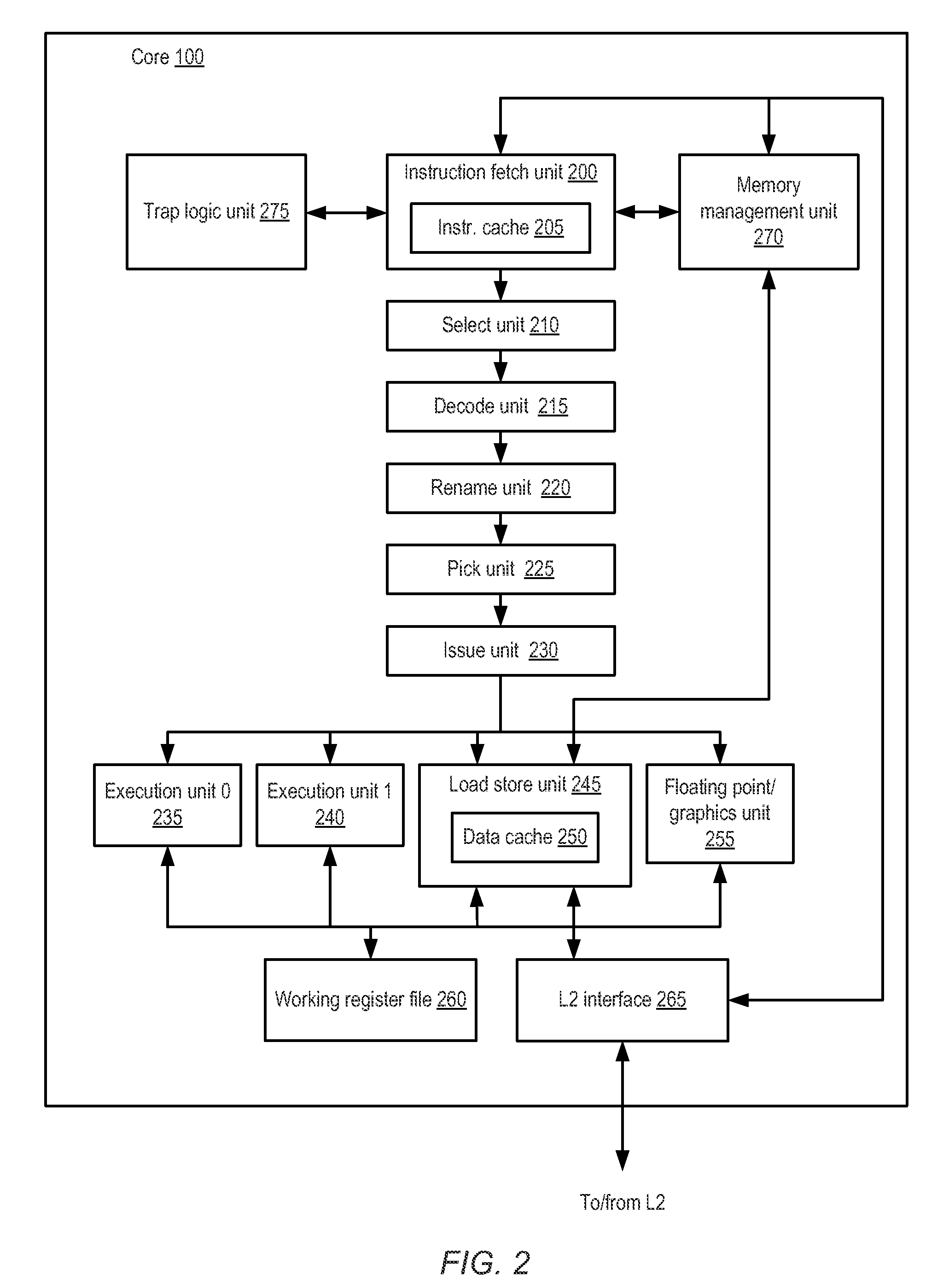

A processor includes an instruction fetch unit configured to issue instructions for execution, where the instructions are selected from a number of threads, where each given instruction has a corresponding thread identifier, and where at least some of the instructions specify operand(s) via register identifiers. A register file stores operands usable by the instructions, and may include several banks, each corresponding to a register identifiers and including several entries corresponding to the several threads, wherein the entries are configured to store data values. In response to receiving a request to read a particular register identifier for a given thread identifier, the register file may be configured to decode the given thread identifier to retrieve entries from the banks that correspond to the given thread identifier. The register file may further select, from among the retrieved entries, a data value corresponding to the particular register identifier to be output.

Owner:ORACLE INT CORP

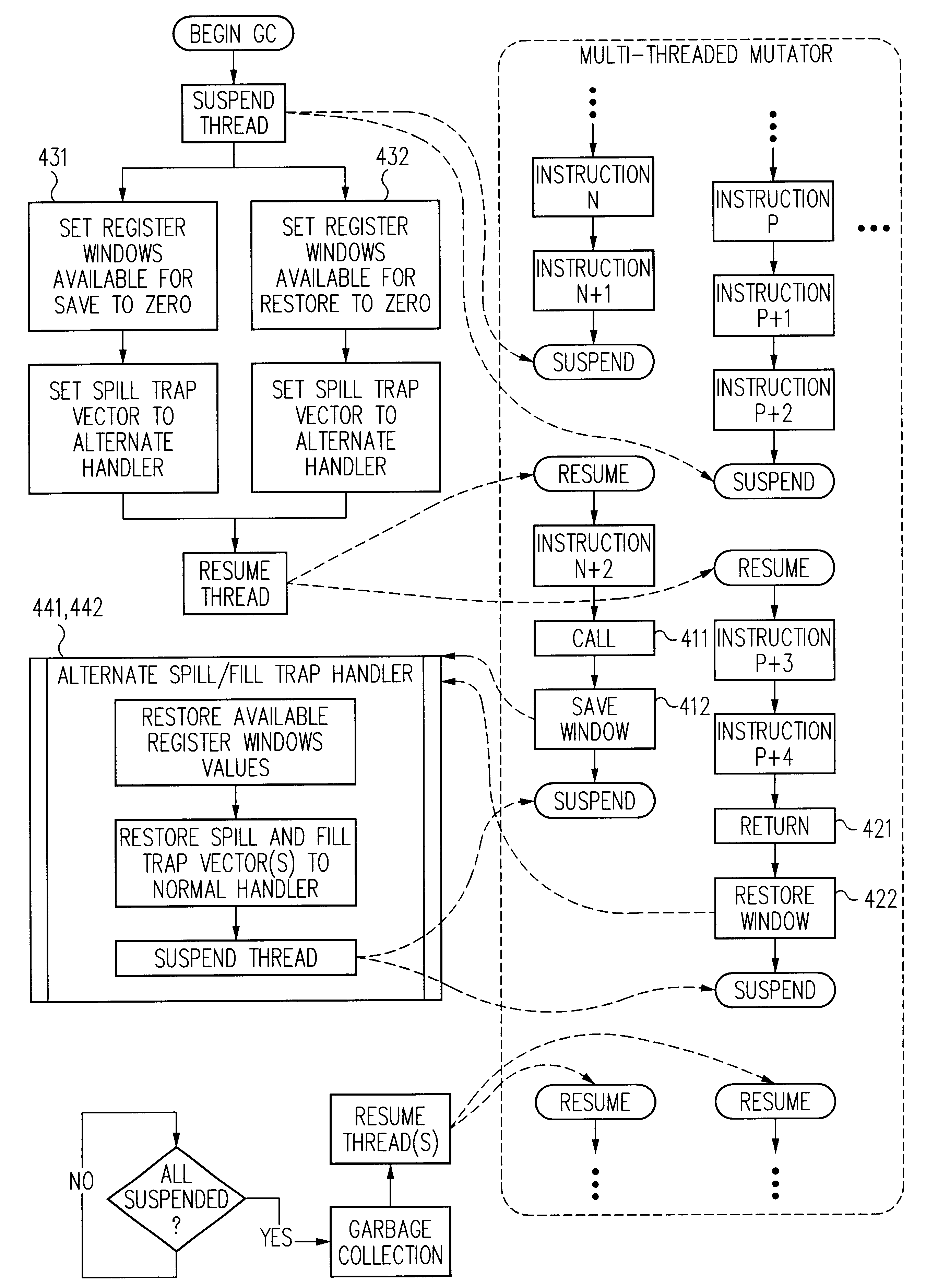

Thread suspension system and method

InactiveUS6842853B1Negligible overheadLower latencyMemory adressing/allocation/relocationDigital computer detailsRegister windowInstruction set

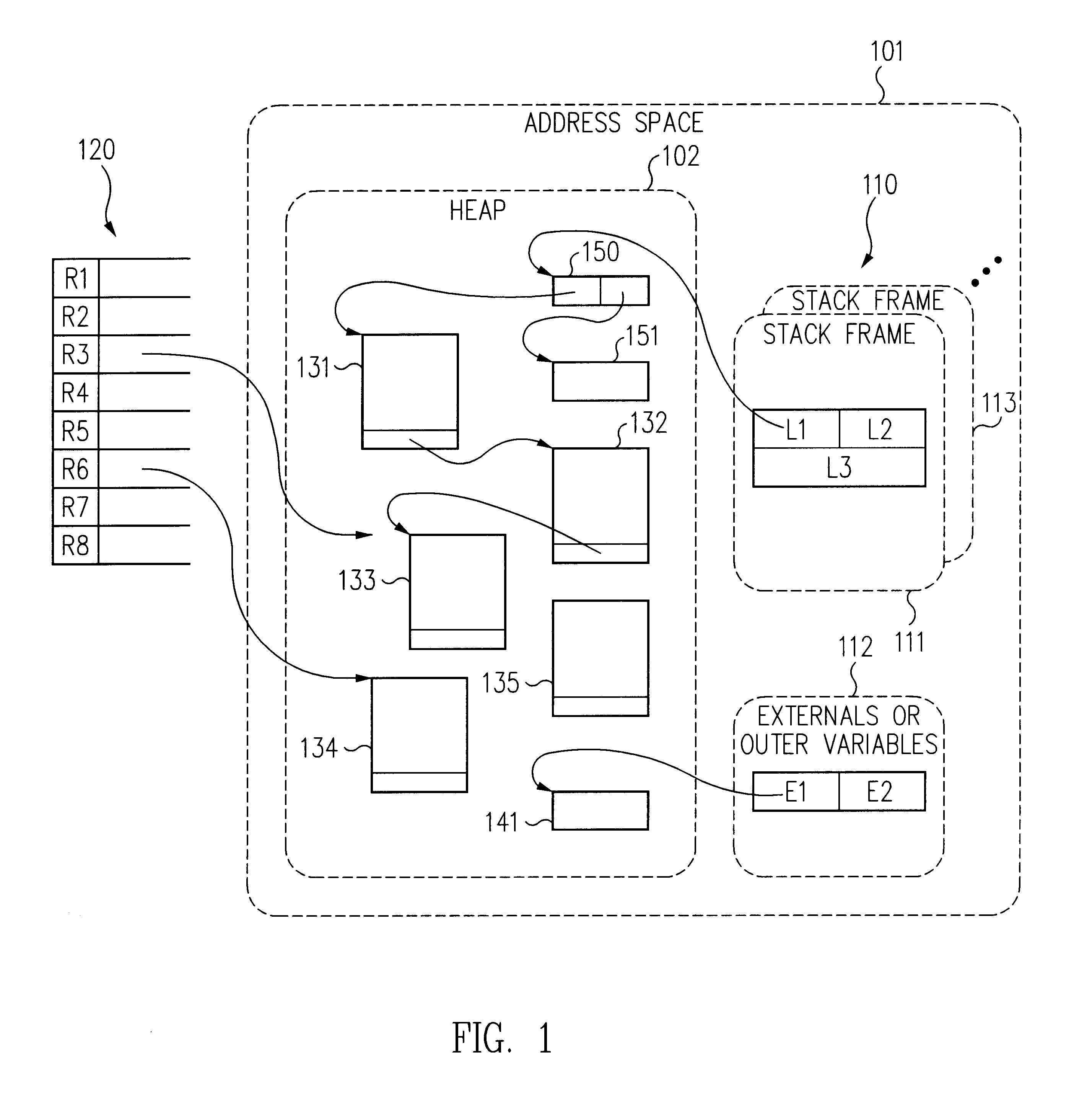

In processor architectures that support allocation of register windows to called procedures, functions or methods, register windowing mechanisms can be used to facilitate suspension of a mutator thread (or mutator threads) while imposing negligible overhead on the mutator computation during periods when thread suspension is not requested. Reduced Instruction Set Computer-(RISC)-oriented processor architectures often employ register windows (typically partially-overlapped register windows) and can therefore benefit from the technique. Variations can be employed even in processors (RISC or otherwise) that do not employ register windowing as long as the processor (by itself or in cooperation with software) provides facilities for allocating and reclaiming resources in correspondence with calls to, and returns from, procedures, functions or methods. Mechanisms are provided to spill values from the fixed set of resources to a secondary store and to fill values from the secondary store into the fixed set in correspondence with function call triggered overflows and function return triggered underflows. In some configurations, modified spill and / or fill mechanism(s) are used to suspend threads at safe points coinciding with call and / or return sites. Because the modified spill and / or fill mechanism(s) impose negligible overhead when not employed and can be engaged in response to an event (e.g., a start garbage collection event), safe points can be defined at call and / or return points throughout mutator code to reduce the latency between the event and suspension of threads.

Owner:ORACLE INT CORP

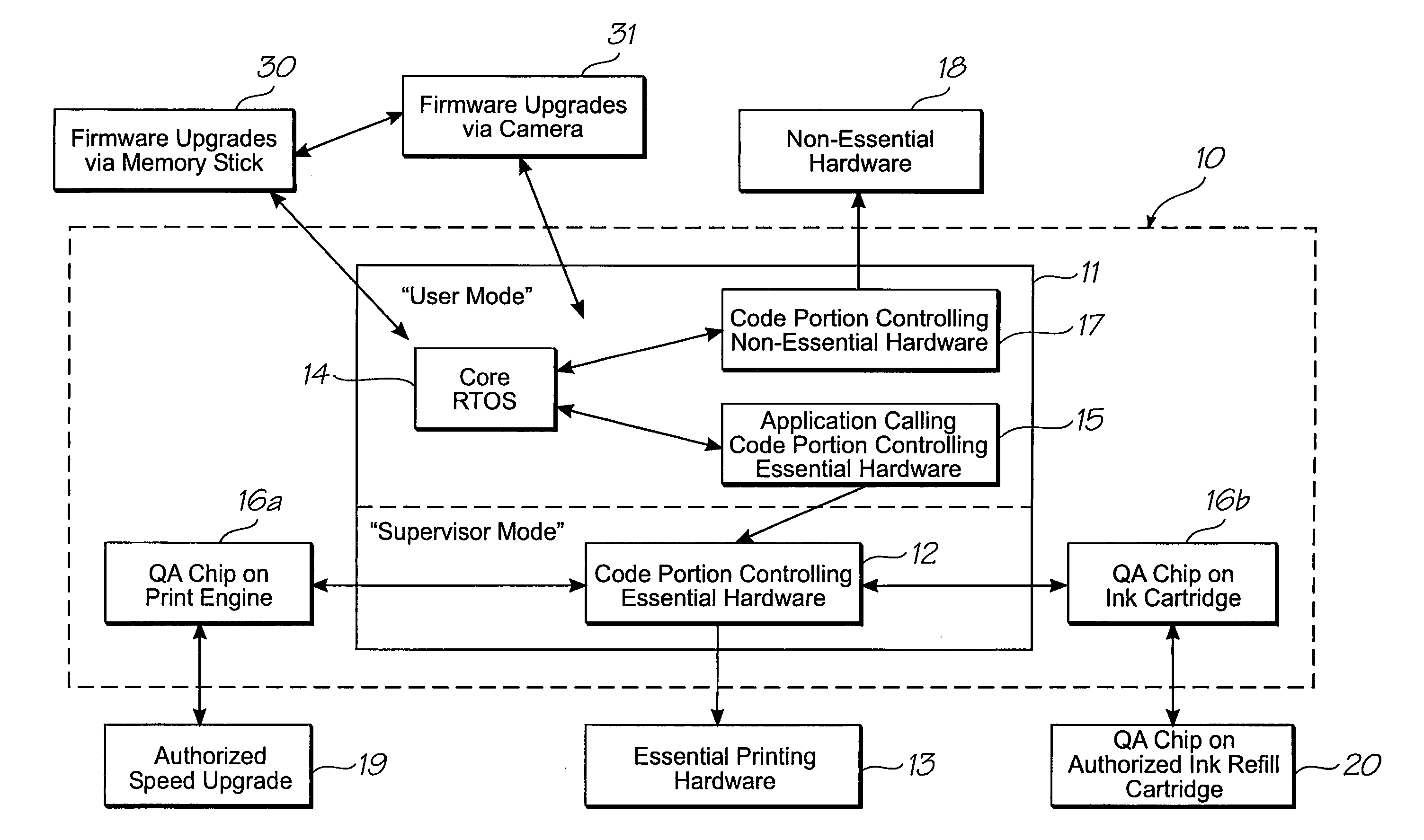

System for protecting sensitive data from user code in register window architecture

InactiveUS20080010425A1Simple processDigital data processing detailsUnauthorized memory use protectionComputer hardwareRegister window

A system for protecting supervisor mode data from user code in a register window architecture of a processor is provided. The system, when transitioning from supervisor mode to user mode, setting at least one invalid window bit in the invalid window mask of the architecture additional to the invalid window bit set for the reserved window of the invalid window mask. The additional bit is set for a transition window between supervisor and user data windows.

Owner:MEMJET TECH LTD

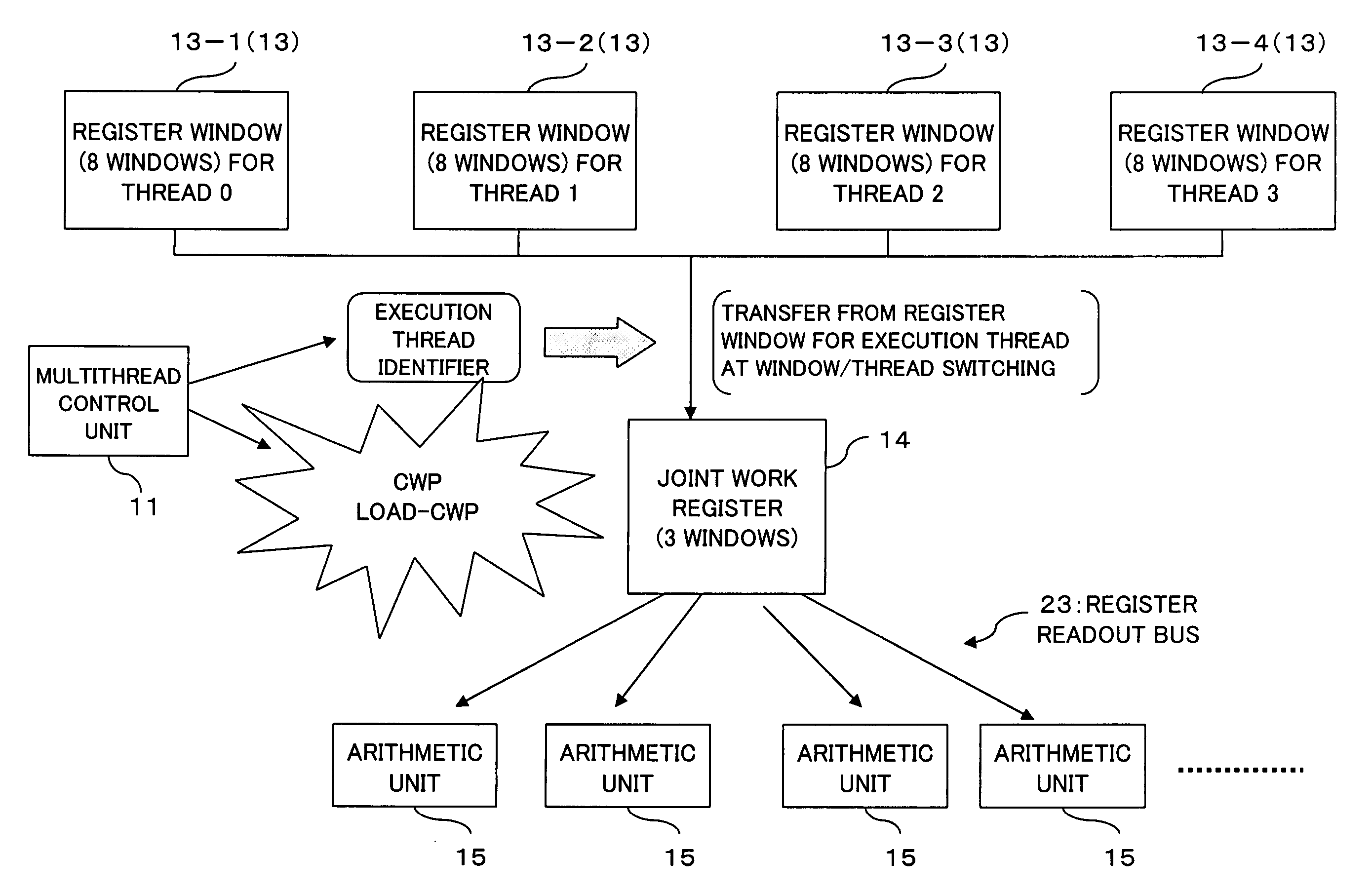

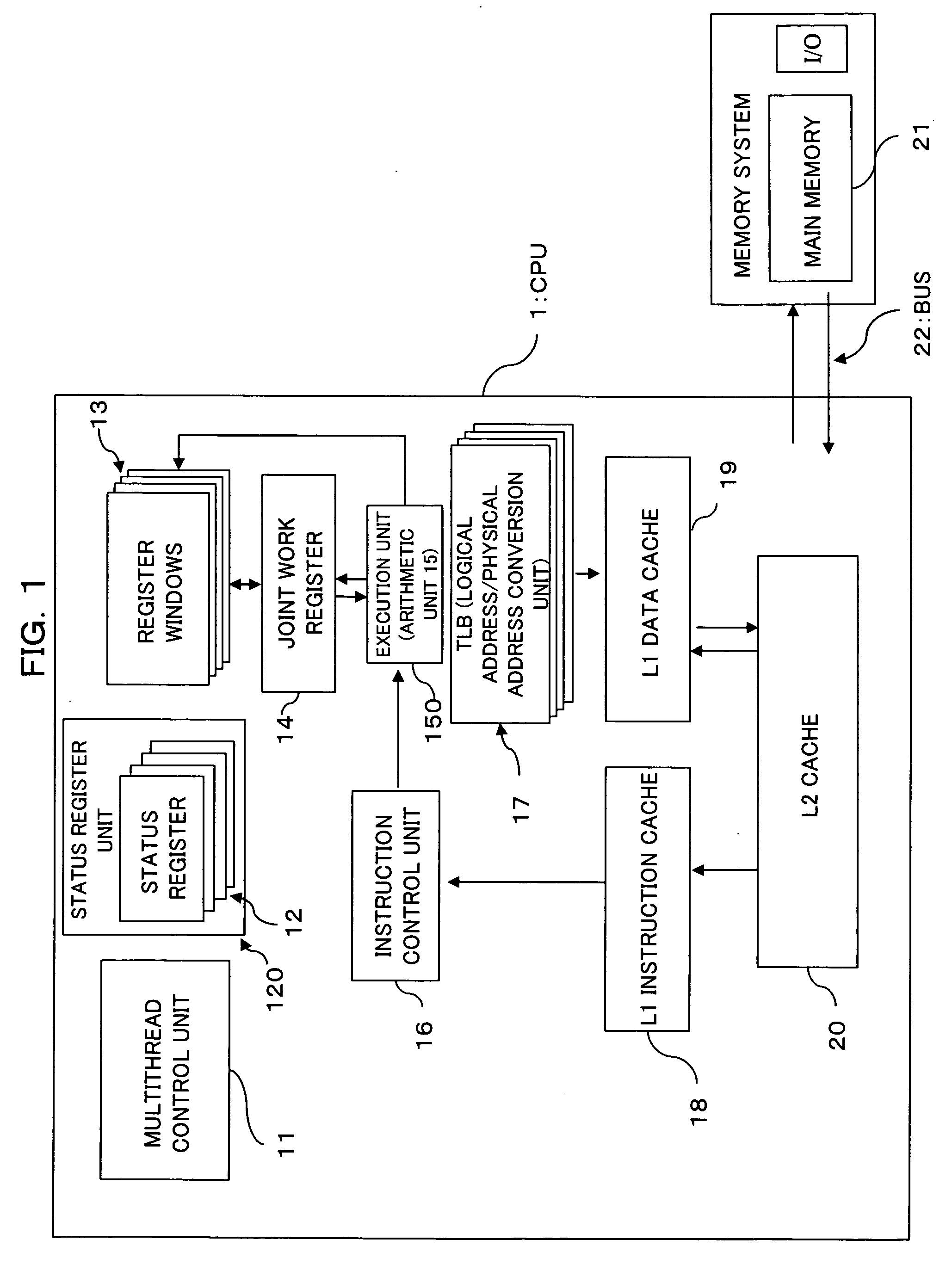

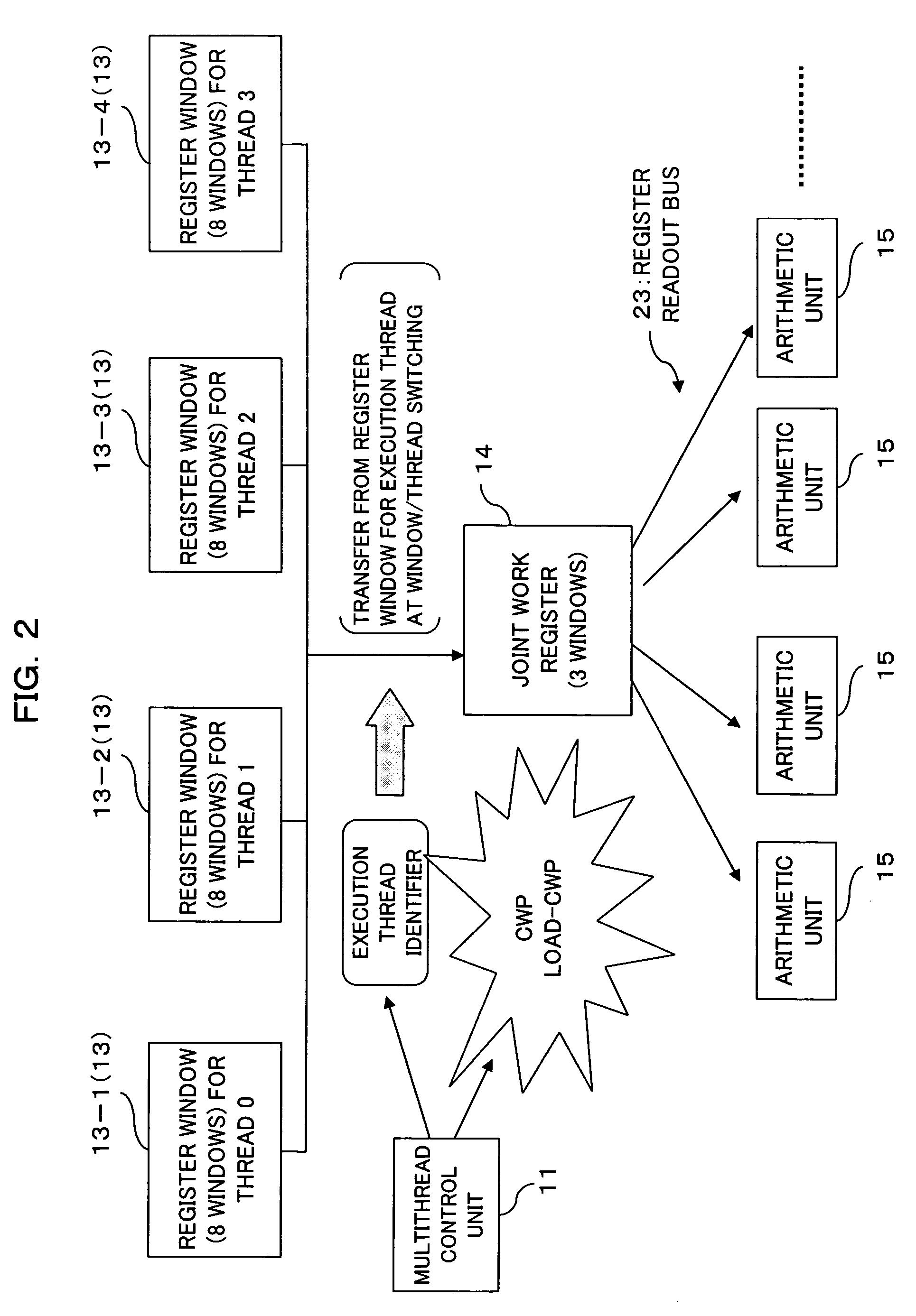

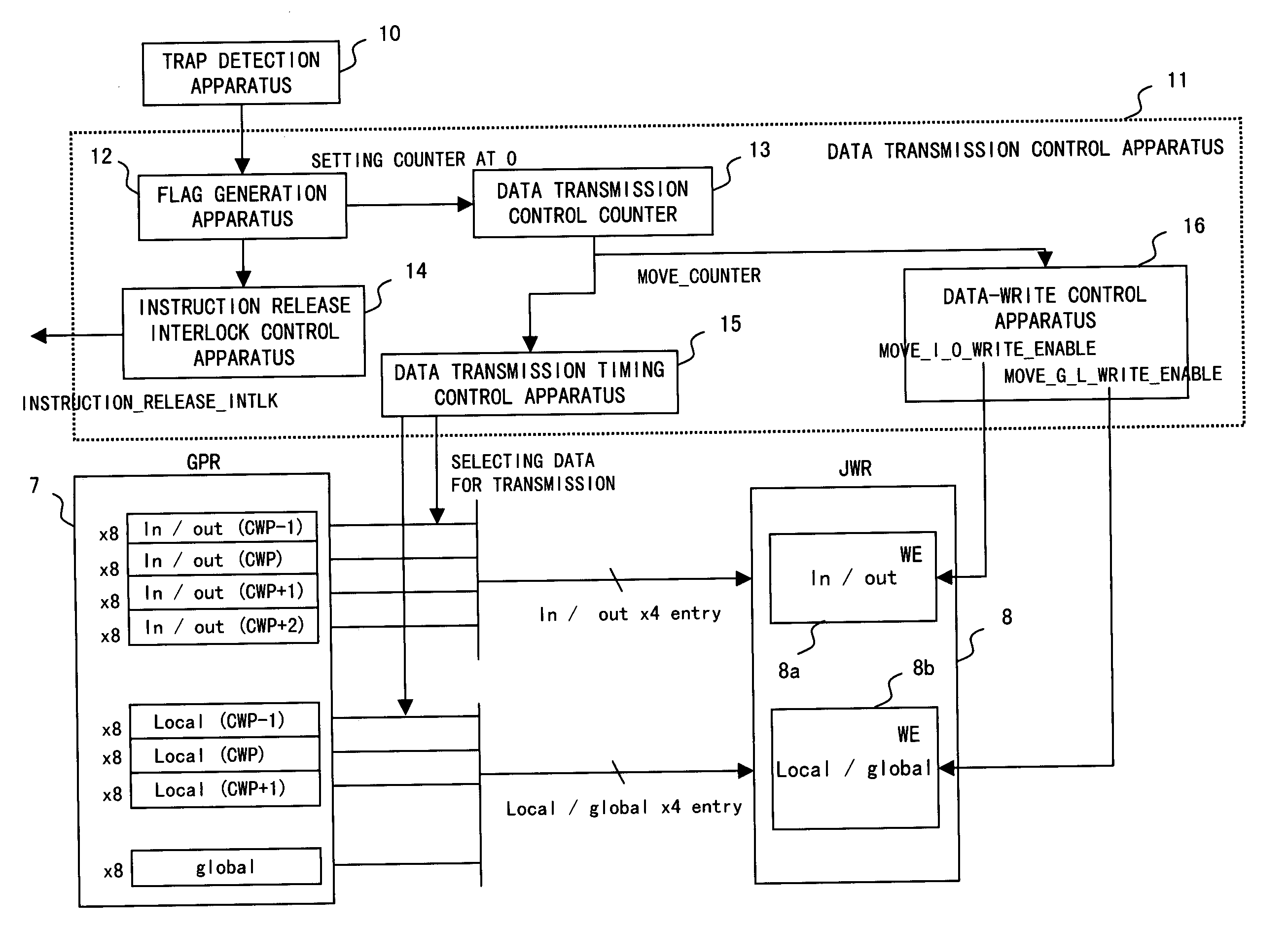

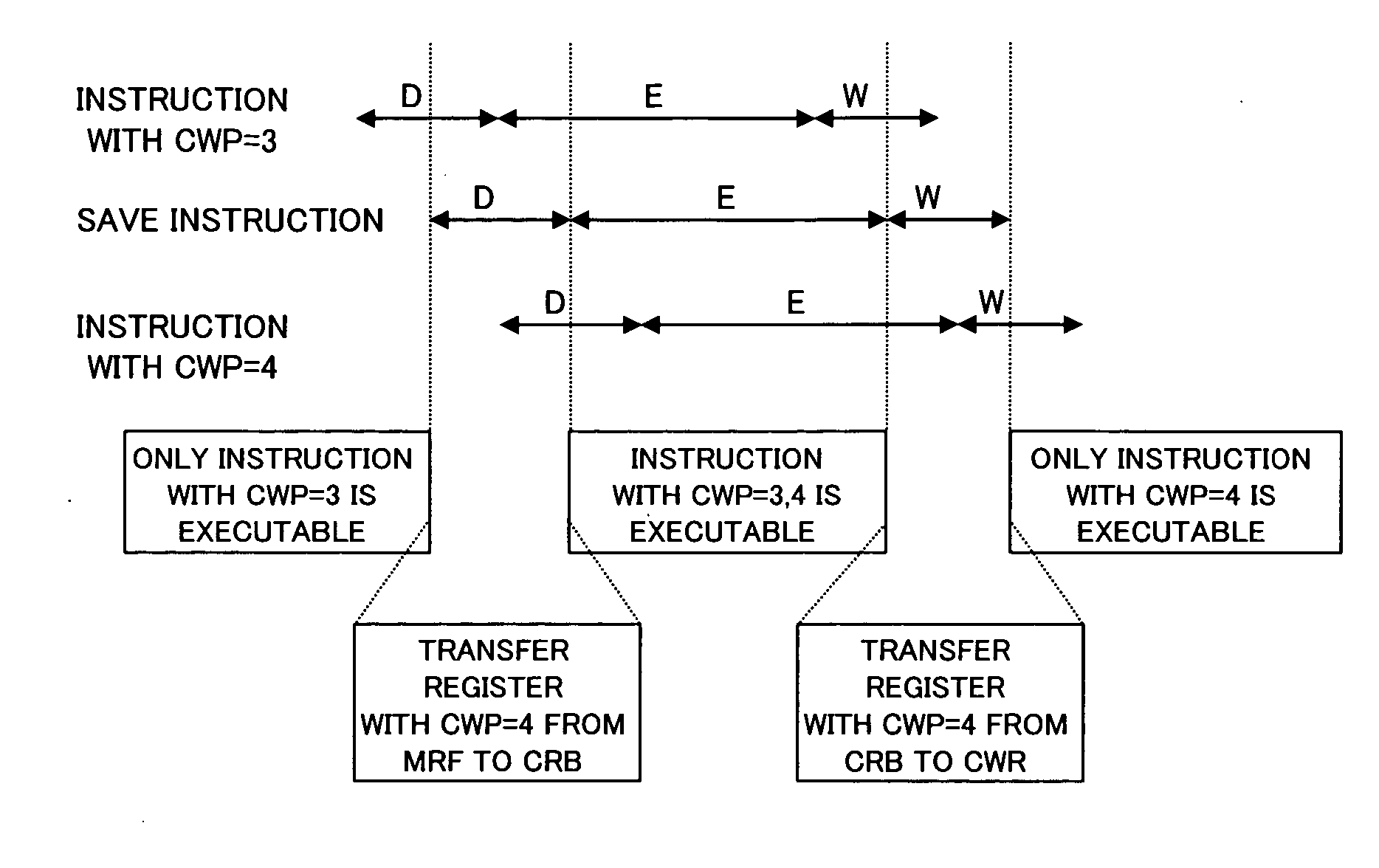

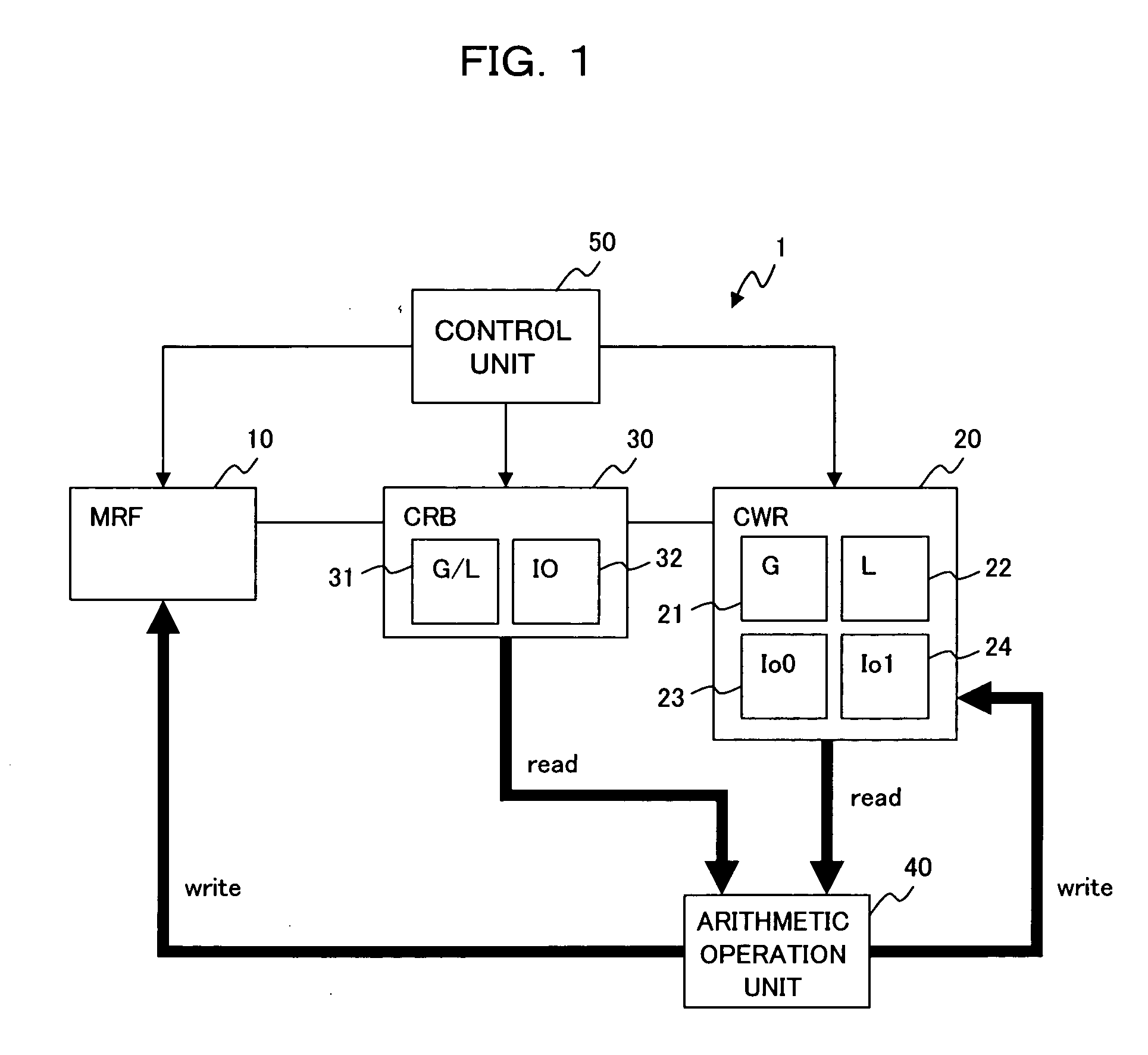

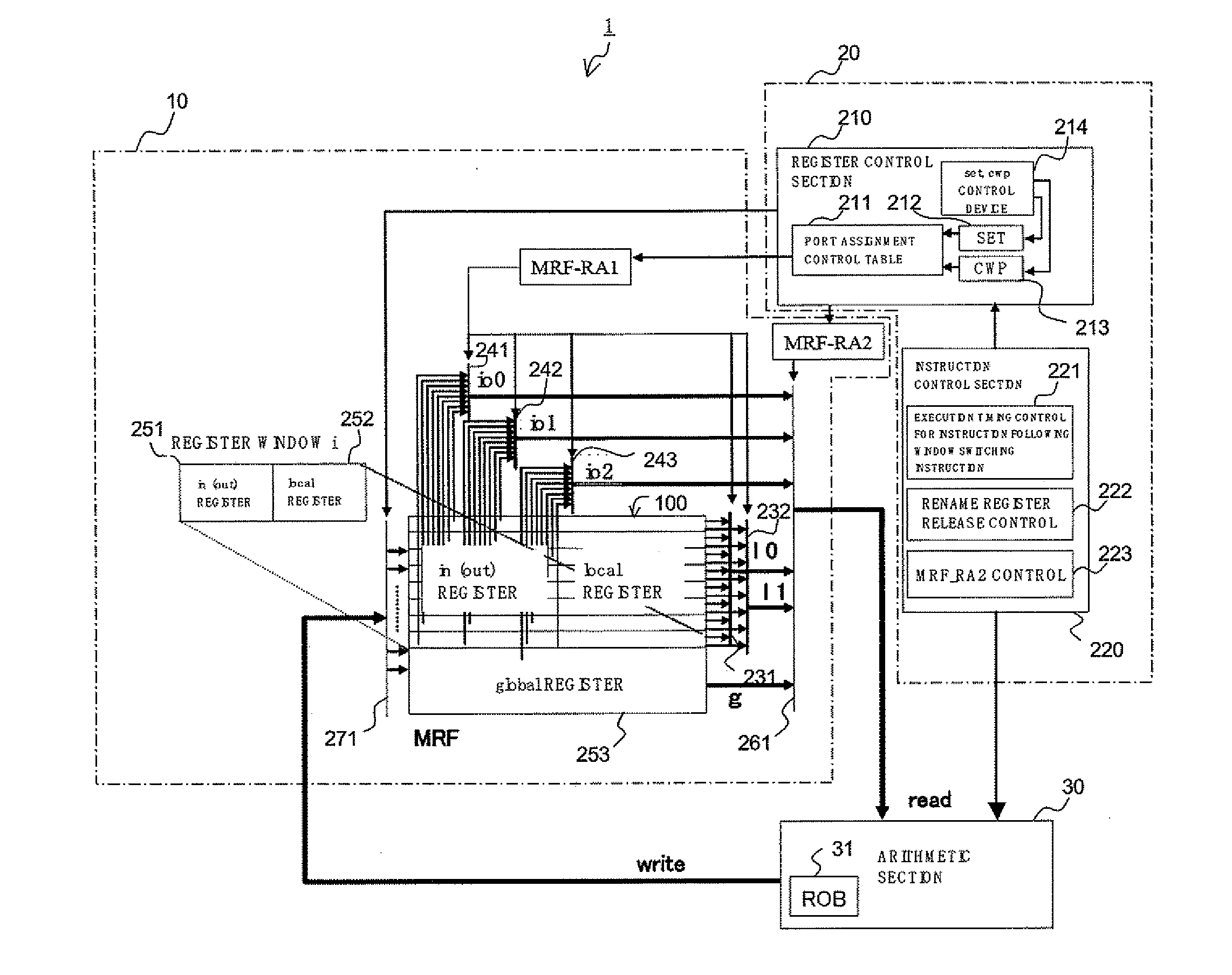

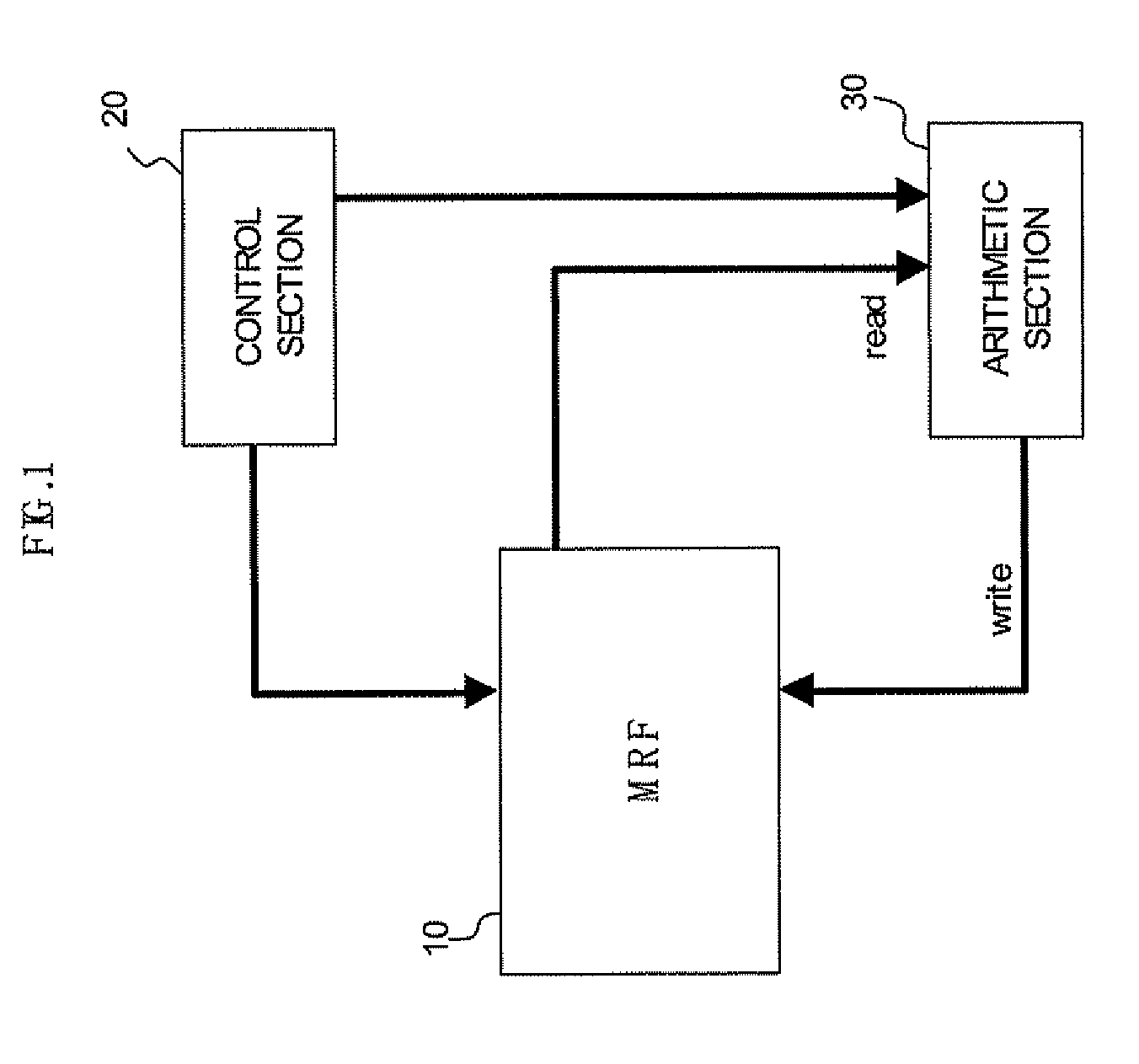

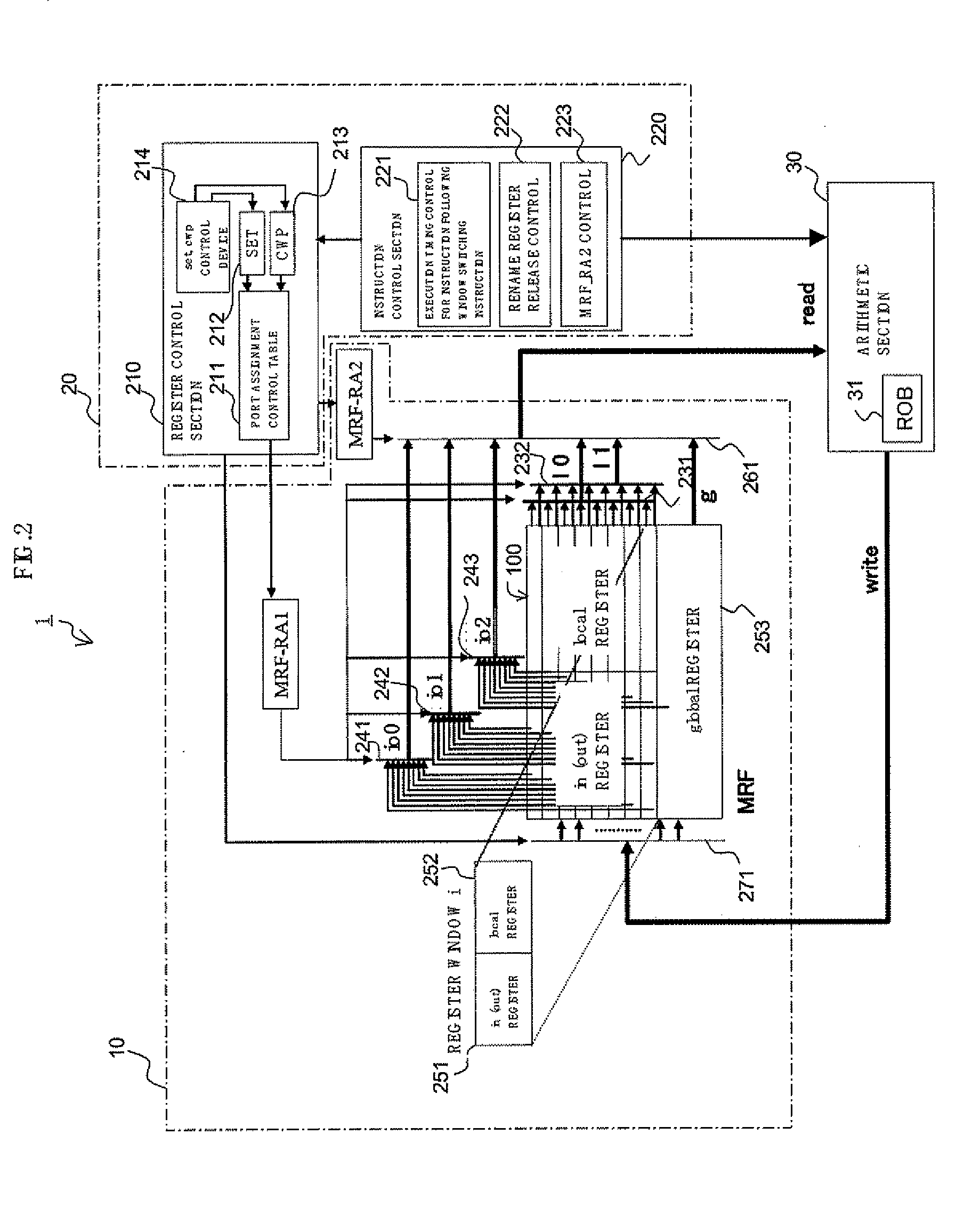

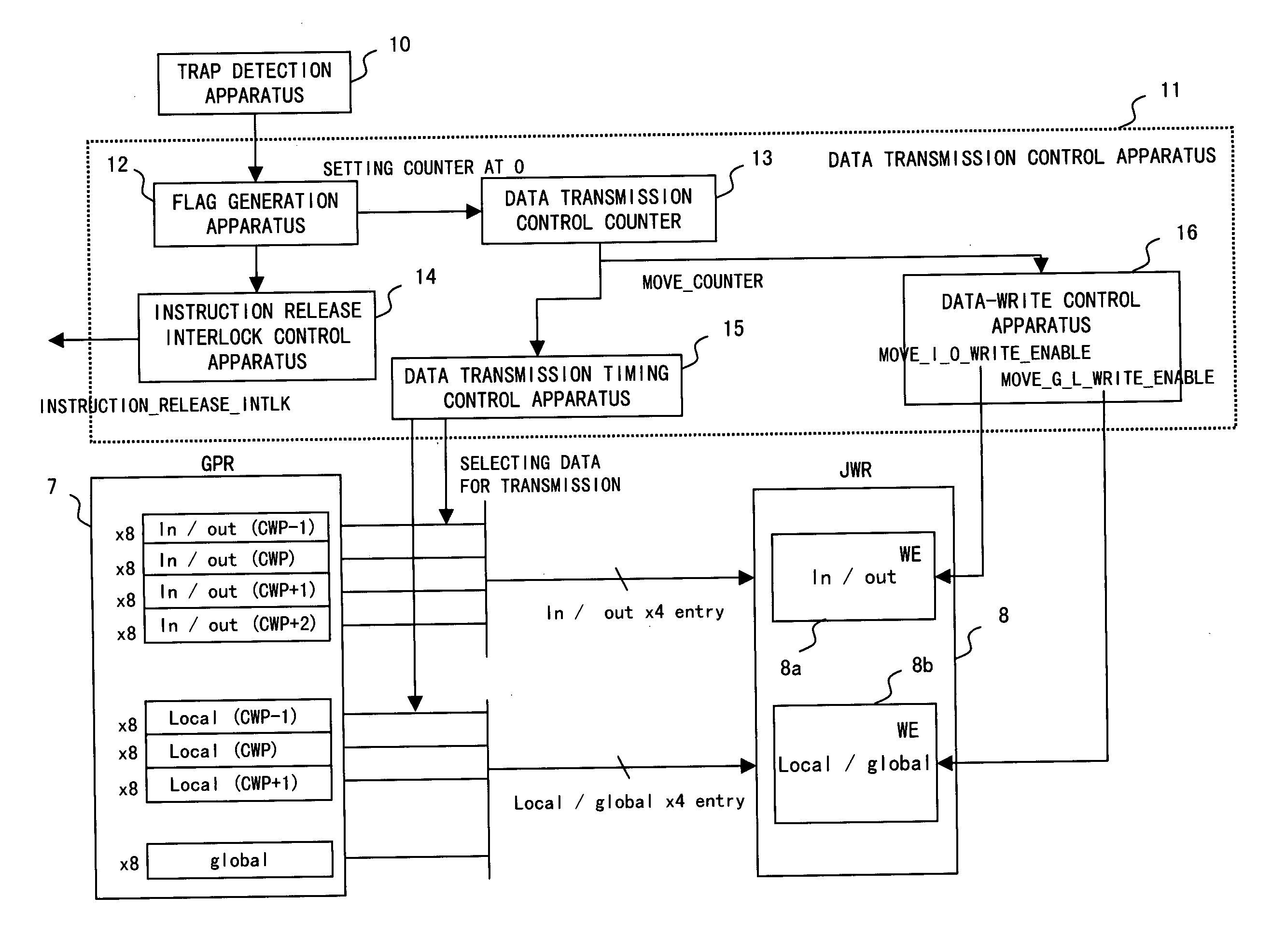

Multithread processor and register control method

InactiveUS20060020776A1Increase speedDigital computer detailsSpecific program execution arrangementsRegister windowData transmission

The present invention relates to a multithread processor, and this multithread processor comprises a plurality of register windows each provided for each of threads and capable of storing data to be used for instruction processing in an arithmetic unit, a work register capable of mutually transferring data with respect to the plurality of register windows and the arithmetic unit and a multithread control unit for controlling data transfer among the plurality of register windows, the work register and the arithmetic unit on the basis of an execution thread identifier for identifying the thread to be executed in the arithmetic unit. This enables conducting the multithread processing at a high speed.

Owner:FUJITSU LTD

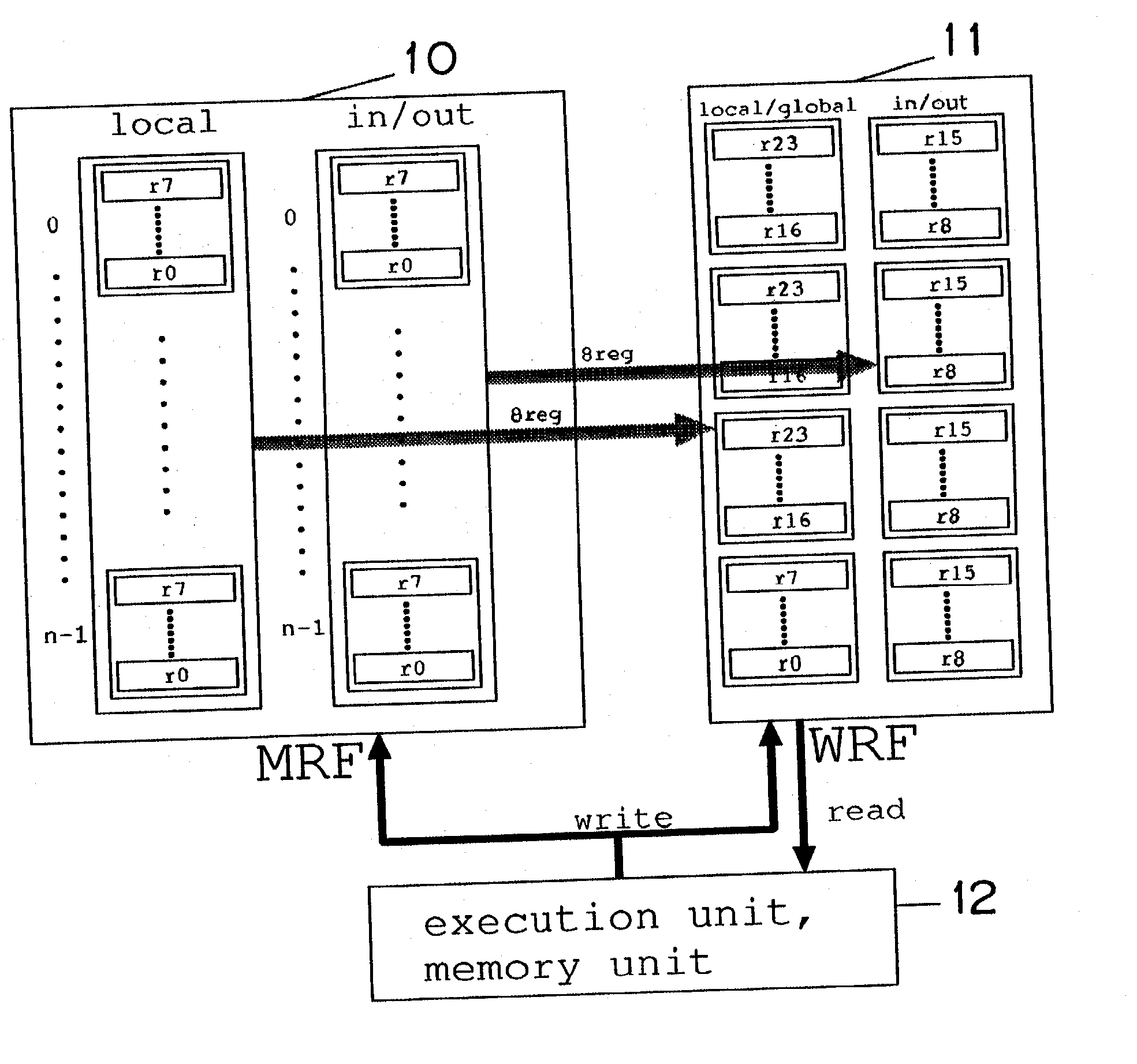

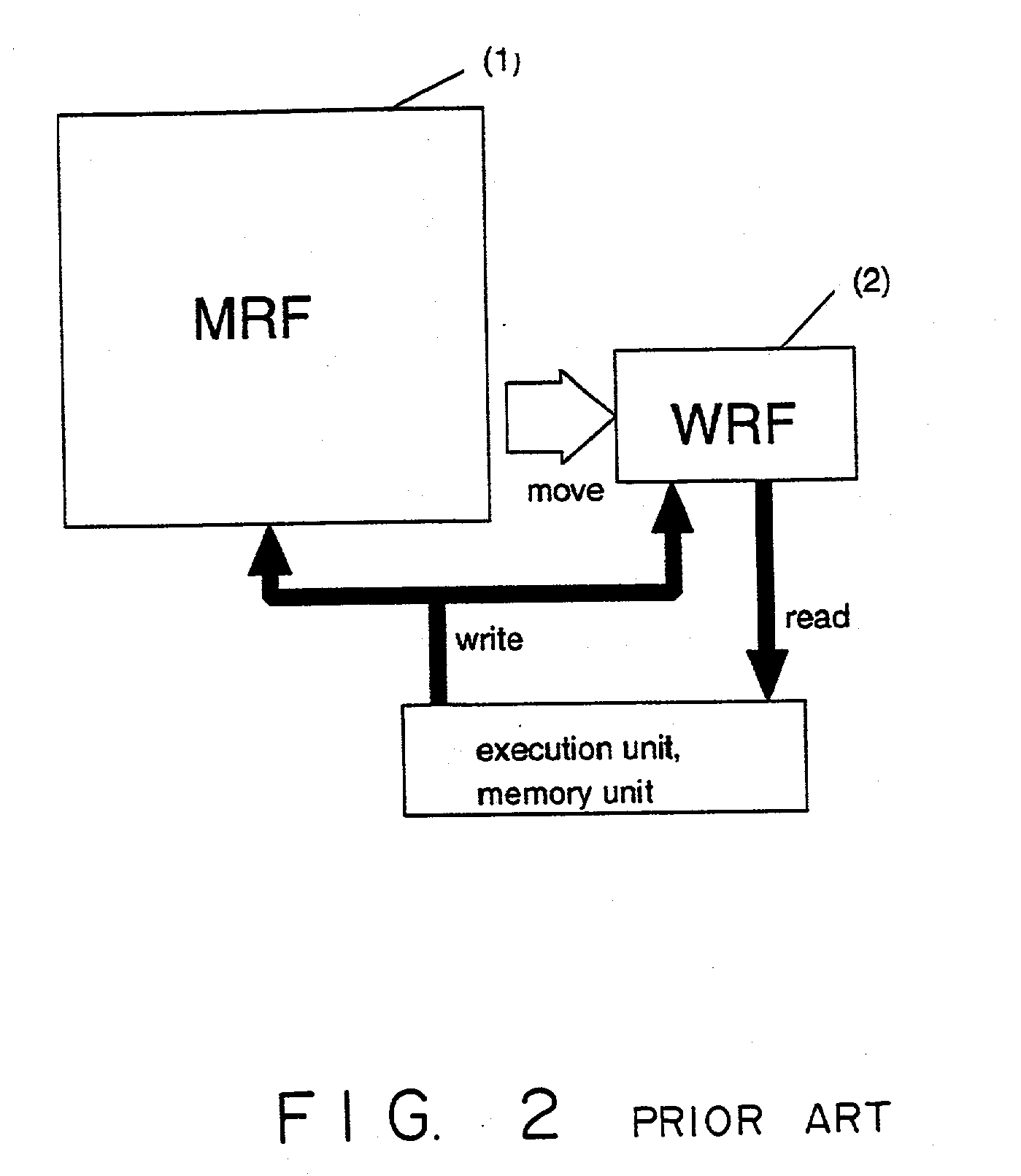

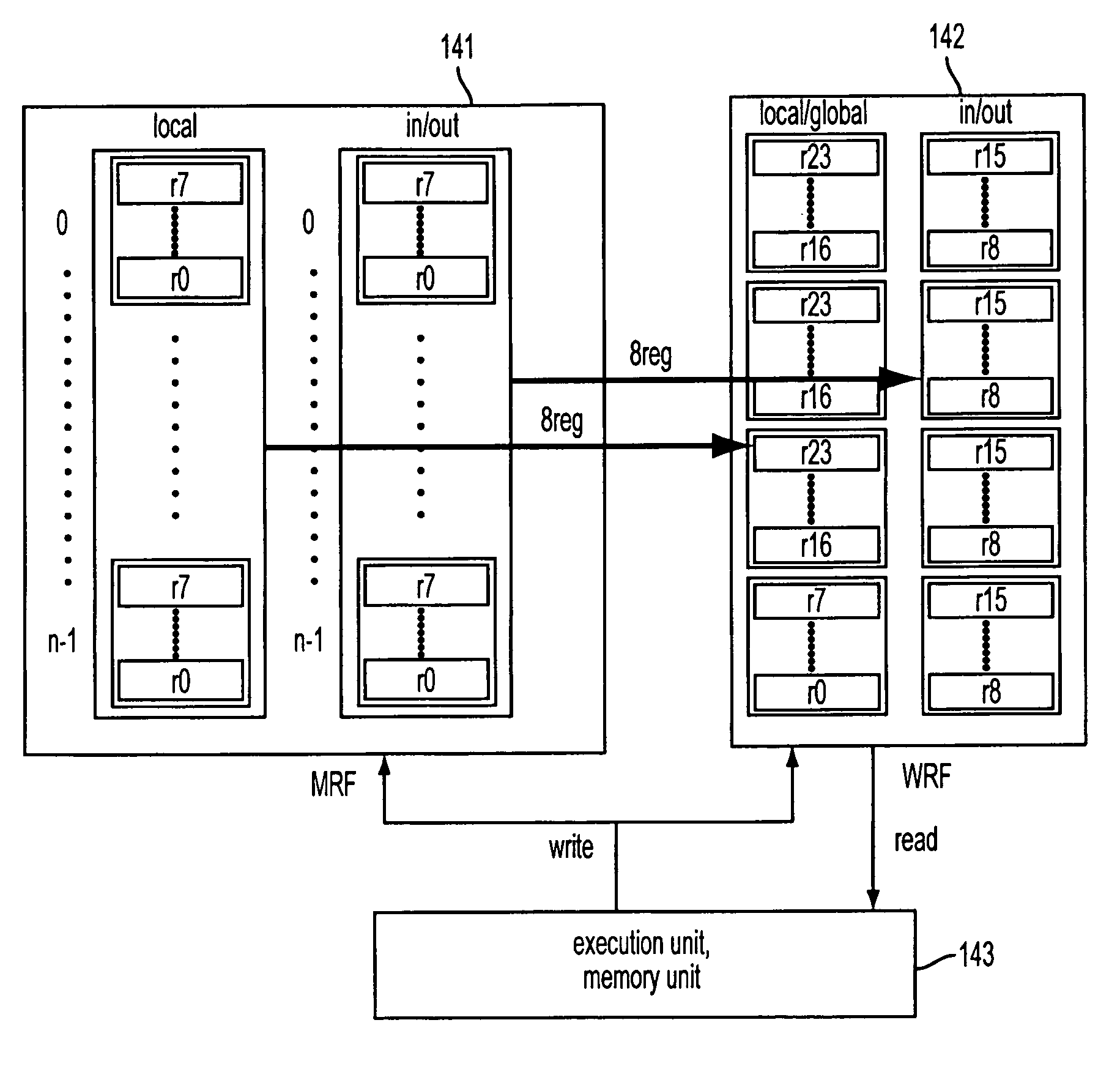

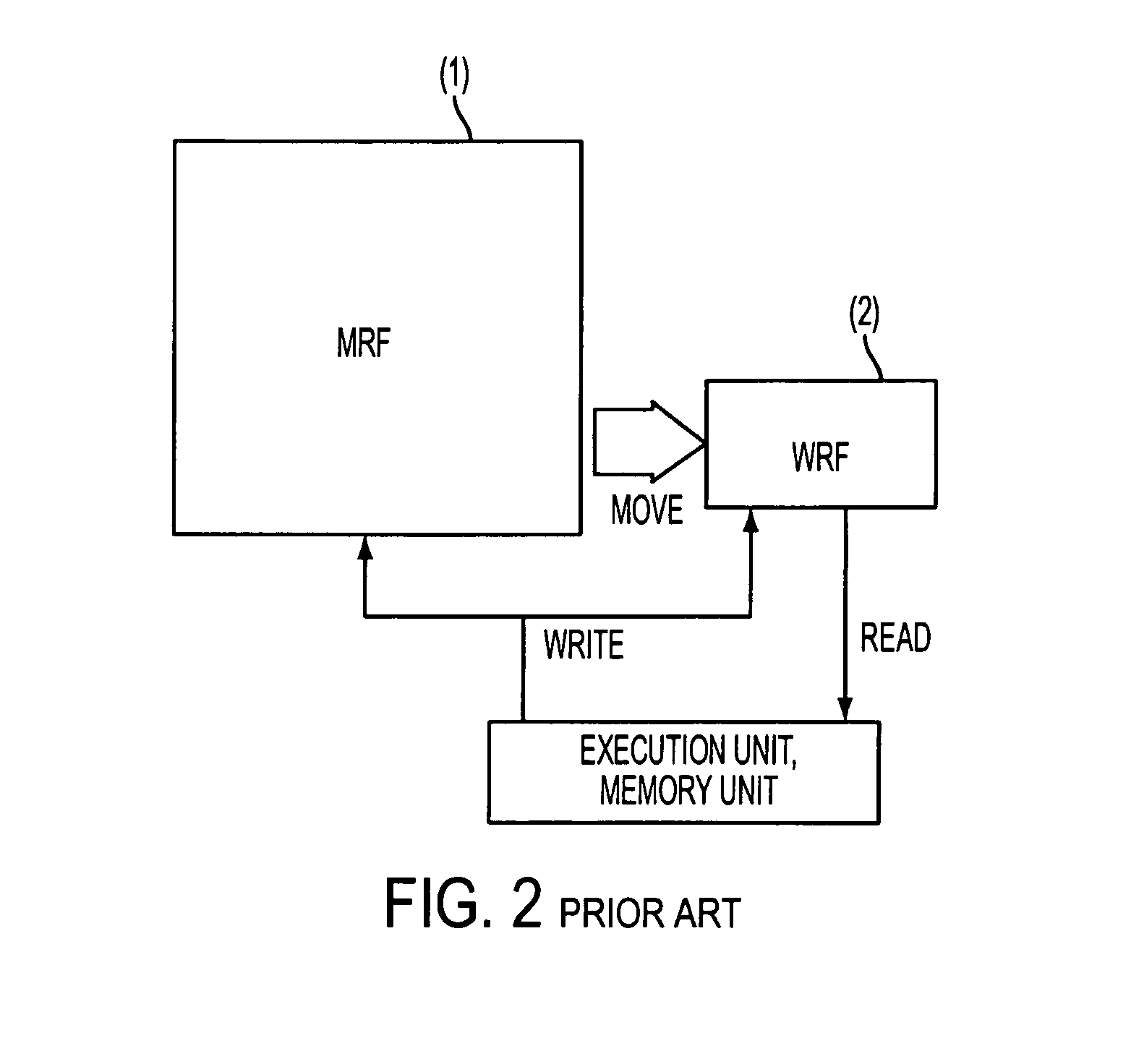

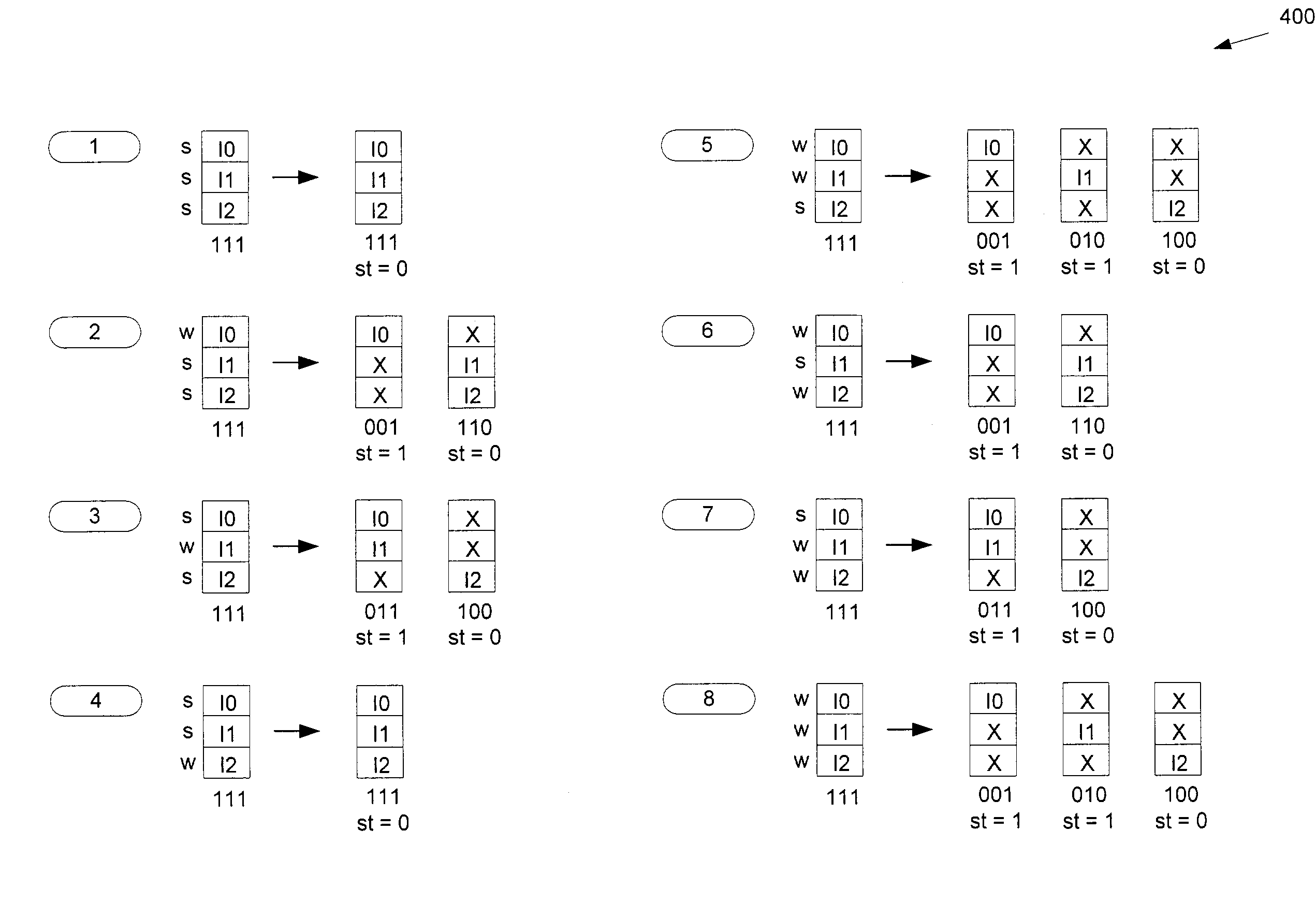

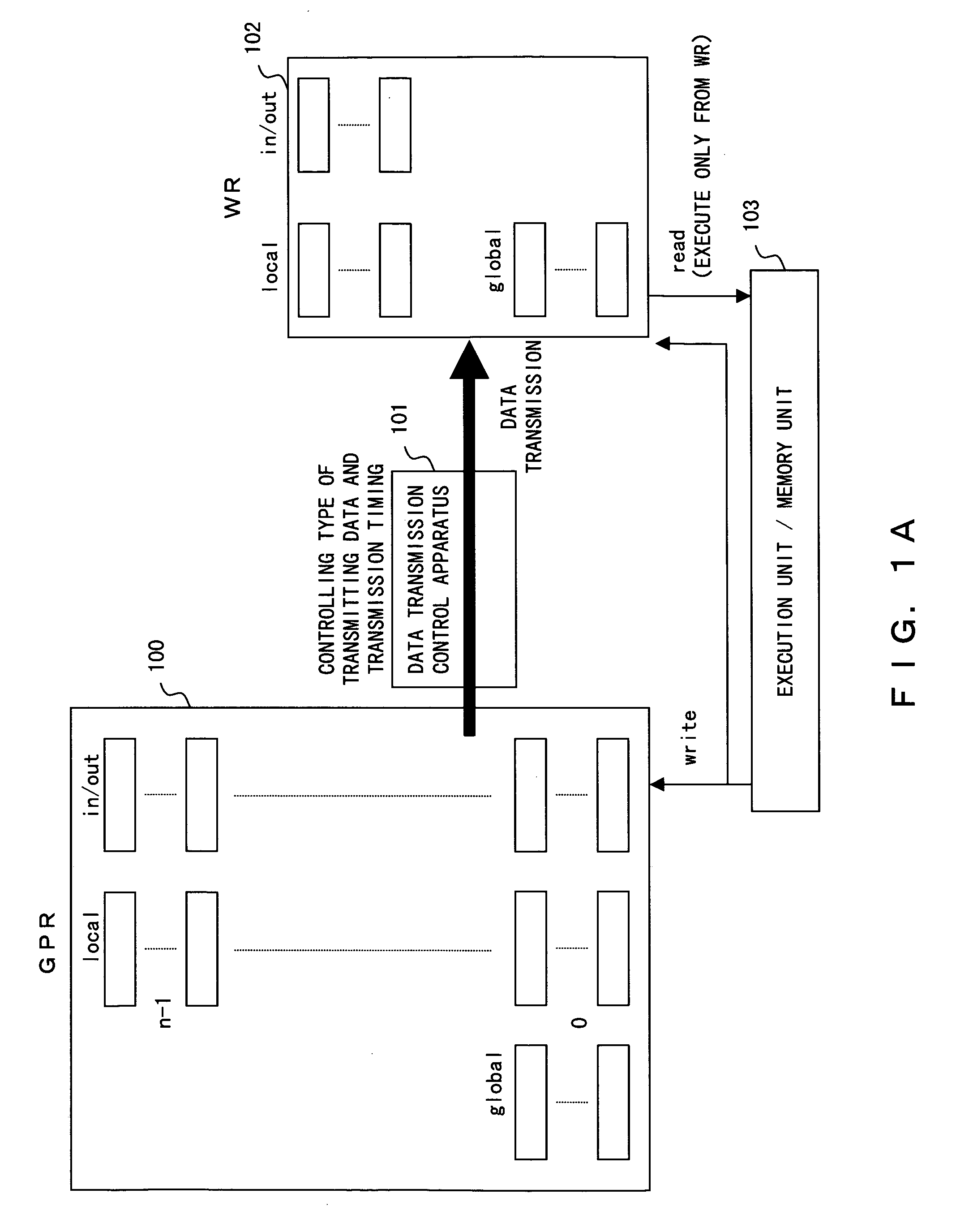

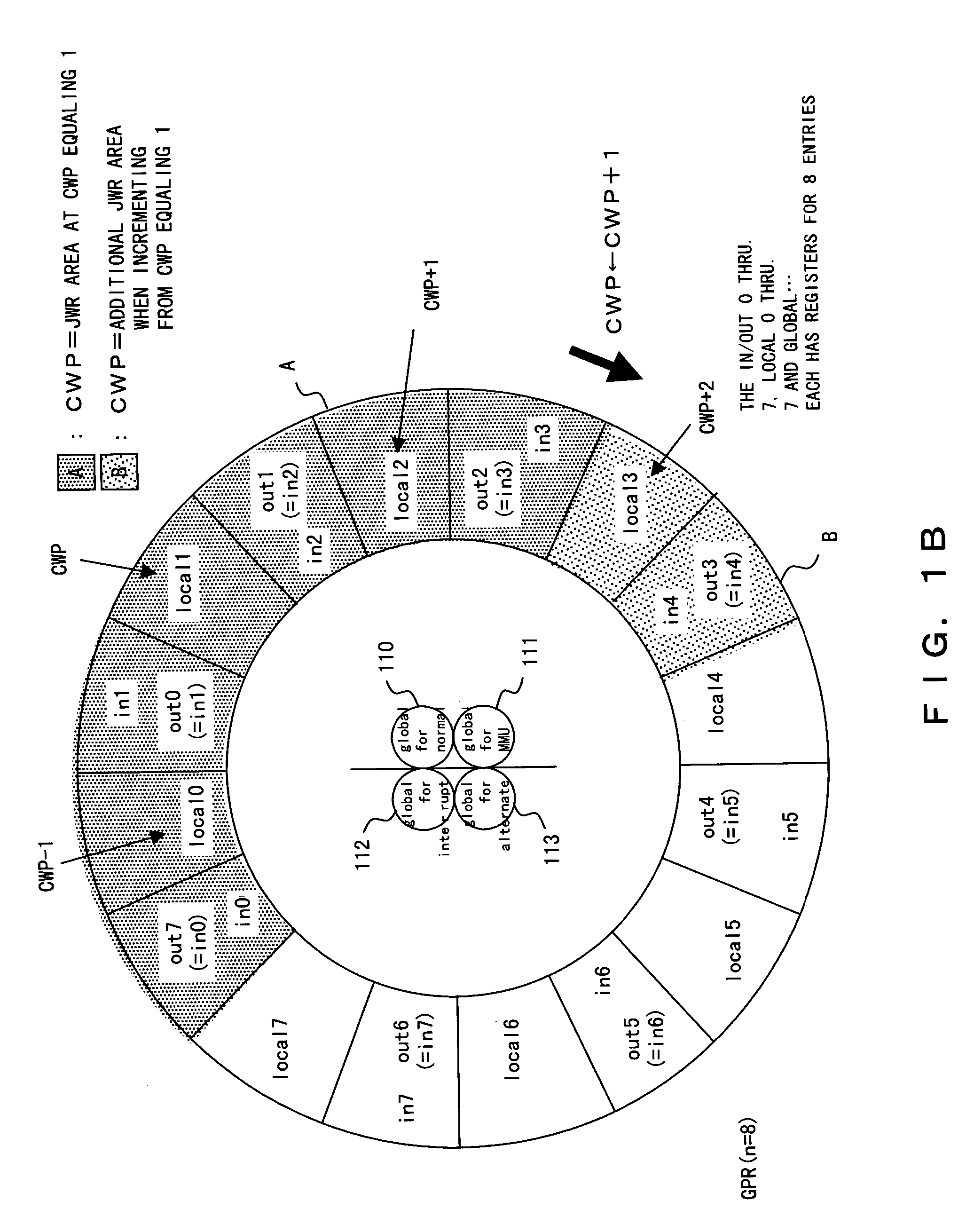

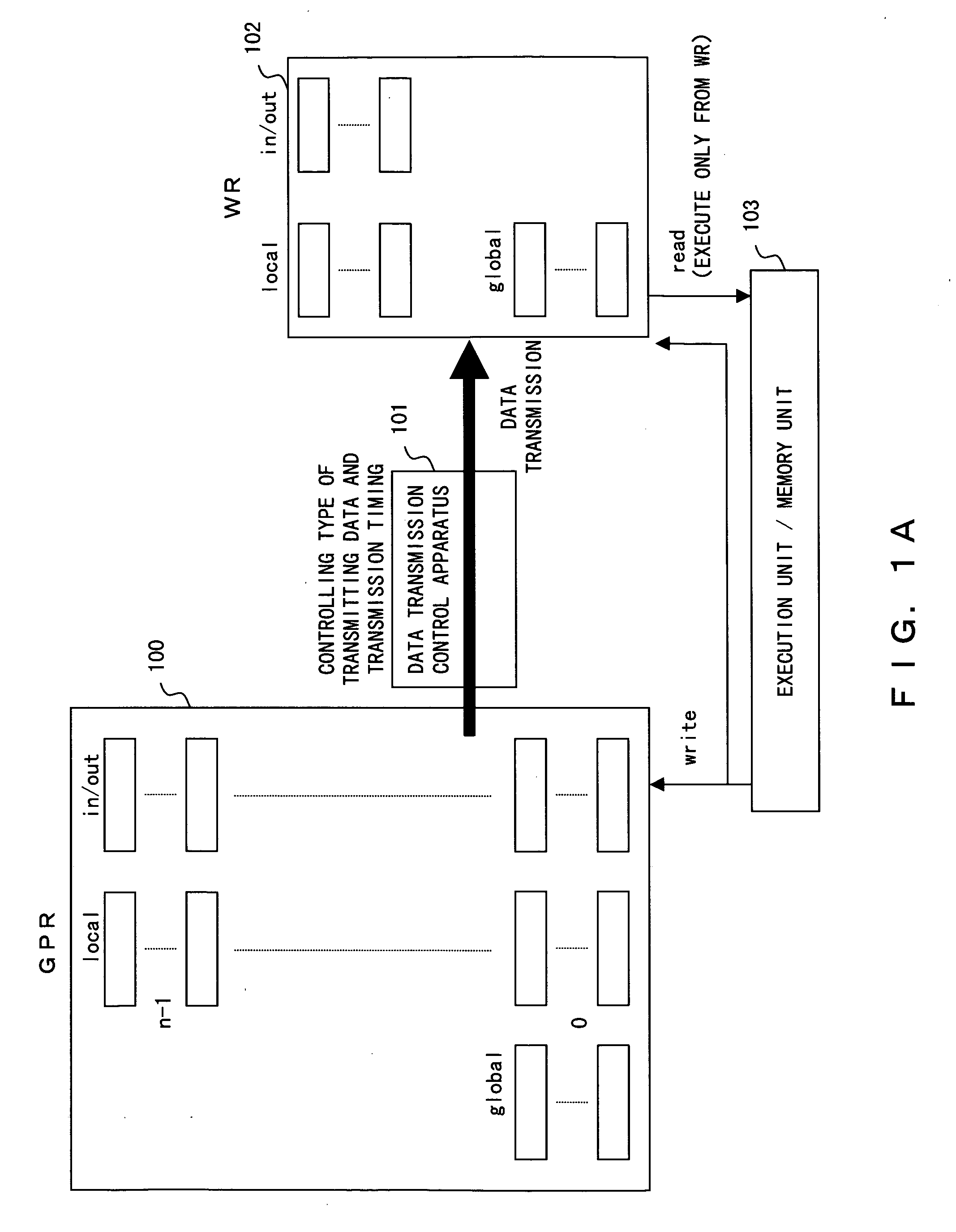

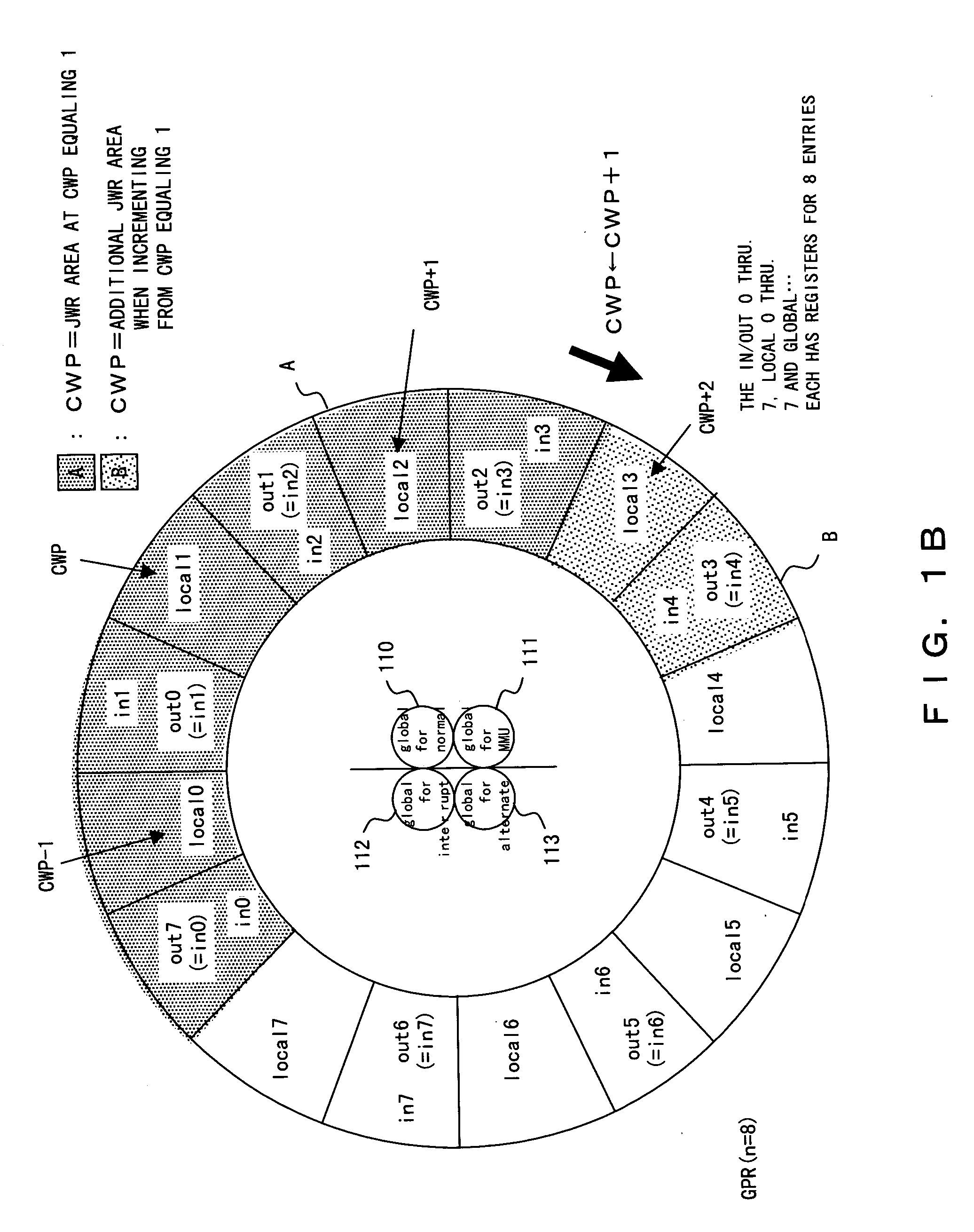

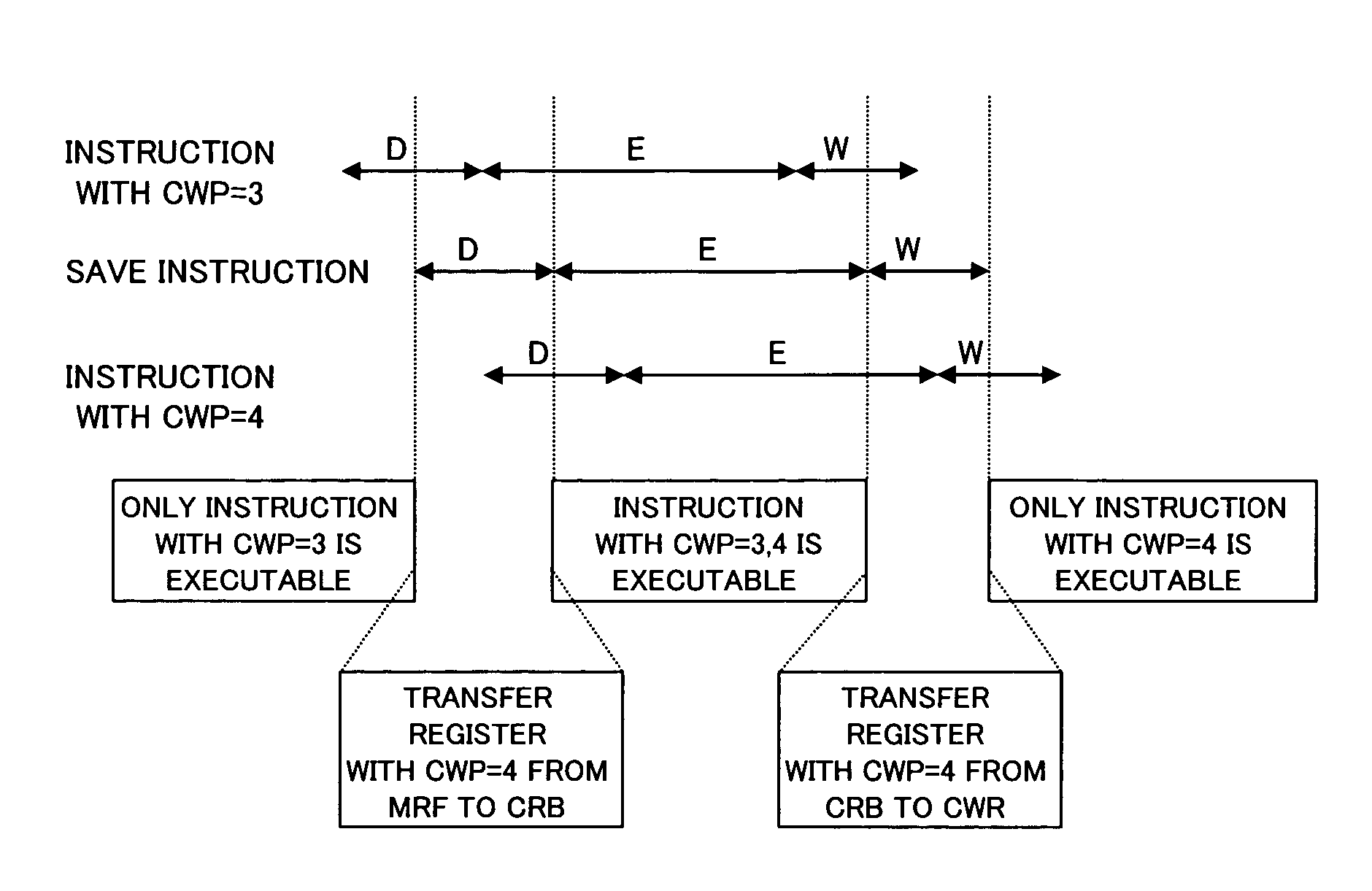

Register file in the register window system and controlling method thereof

InactiveUS20030126415A1Digital computer detailsConcurrent instruction executionRegister windowRegister file

In the structure of register files composed of a master register file and a working register file, when data is read, the working register file is accessed. When data is written, the both the master register file and the working register file are accessed. In the working register file, data of the current window, and data preceded thereby, and data followed thereby are stored. Thus, even if the SAVE instruction or the RESTORE instruction are successively executed, instructions can be processed out of order. As a result, the efficiency of the process is improved.

Owner:FUJITSU LTD

Processor and method providing instruction support for instructions that utilize multiple register windows

A processor including instruction support for large-operand instructions that use multiple register windows may issue, for execution, programmer-selectable instructions from a defined instruction set architecture (ISA). The processor may also include an instruction execution unit that, during operation, receives instructions for execution from the instruction fetch unit and executes a large-operand instruction defined within the ISA, where execution of the large-operand instruction is dependent upon a plurality of registers arranged within a plurality of register windows. The processor may further include control circuitry (which may be included within the fetch unit, the execution unit, or elsewhere within the processor) that determines whether one or more of the register windows depended upon by the large-operand instruction are not present. In response to determining that one or more of these register windows are not present, the control circuitry causes them to be restored.

Owner:ORACLE INT CORP

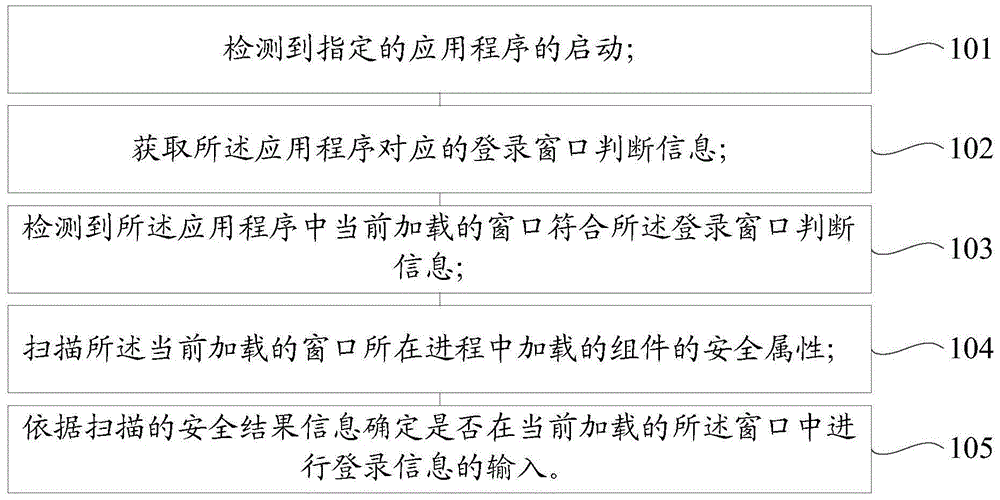

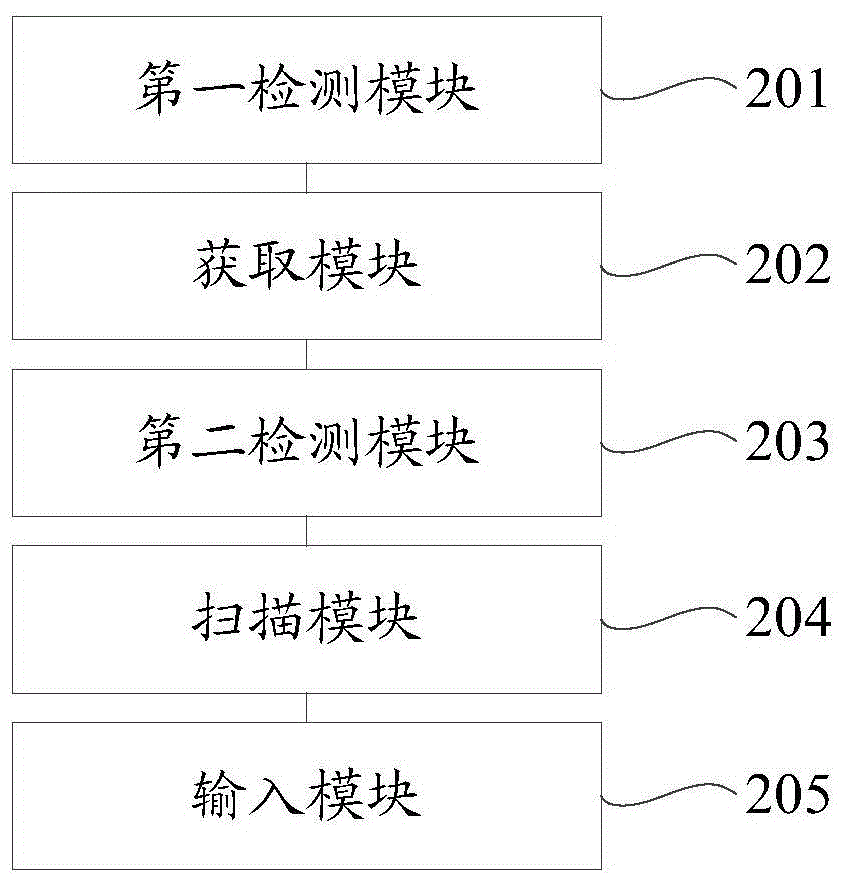

Method and device for registering detecting

InactiveCN104598806AEnsure safetyImprove securityPlatform integrity maintainanceRegister windowPassword

The embodiment of the invention provides a method and device for registering detecting. The method comprises the steps that starting of an appointed application program is detected; registering window judging information corresponding to the application program is obtained; the fact that a currently-loaded window in the application program accords with the judging information of the registering window is detected; the safety attribute of a loaded component in the course where the currently-loaded window is placed is scanned; and according to scanned safety result information, whether registering information recording is carried out in the currently-loaded window is determined. After the application program operates and before registering operation is carried out, the loaded component of the application program is scanned, the fact that a trojan horse cannot be started with the application program is guaranteed, the safety of operation such as paying, registering and network communication is guaranteed, the problem that the trojan horse is started with the application program is effectively solved, malicious acts such as stealing of an account number, a password and key data are avoided, and the safety of the application program in operation such paying, registering and network communication is greatly improved.

Owner:BEIJING QIHOO TECH CO LTD +1

Register window management using first pipeline to change current window and second pipeline to read operand from old window and write operand to new window

In one embodiment, a processor is configured to execute a window swap instruction. The processor comprises a register file (that comprises a plurality of registers) and first and second execution units coupled to the register file. A first pipeline associated with the first execution unit has a first number of pipeline stages, and a second pipeline associated with the second execution unit has a second number of pipeline stages. The first execution unit is configured to change the current register window from the first register window to the second register window in the register file in response to the instruction. The second execution unit is configured to perform an operation defined by the instruction and write the result to the register file. The second number of pipeline stages exceeds the first number, whereby the second register window is established in the register file prior to writing the result.

Owner:ORACLE INT CORP

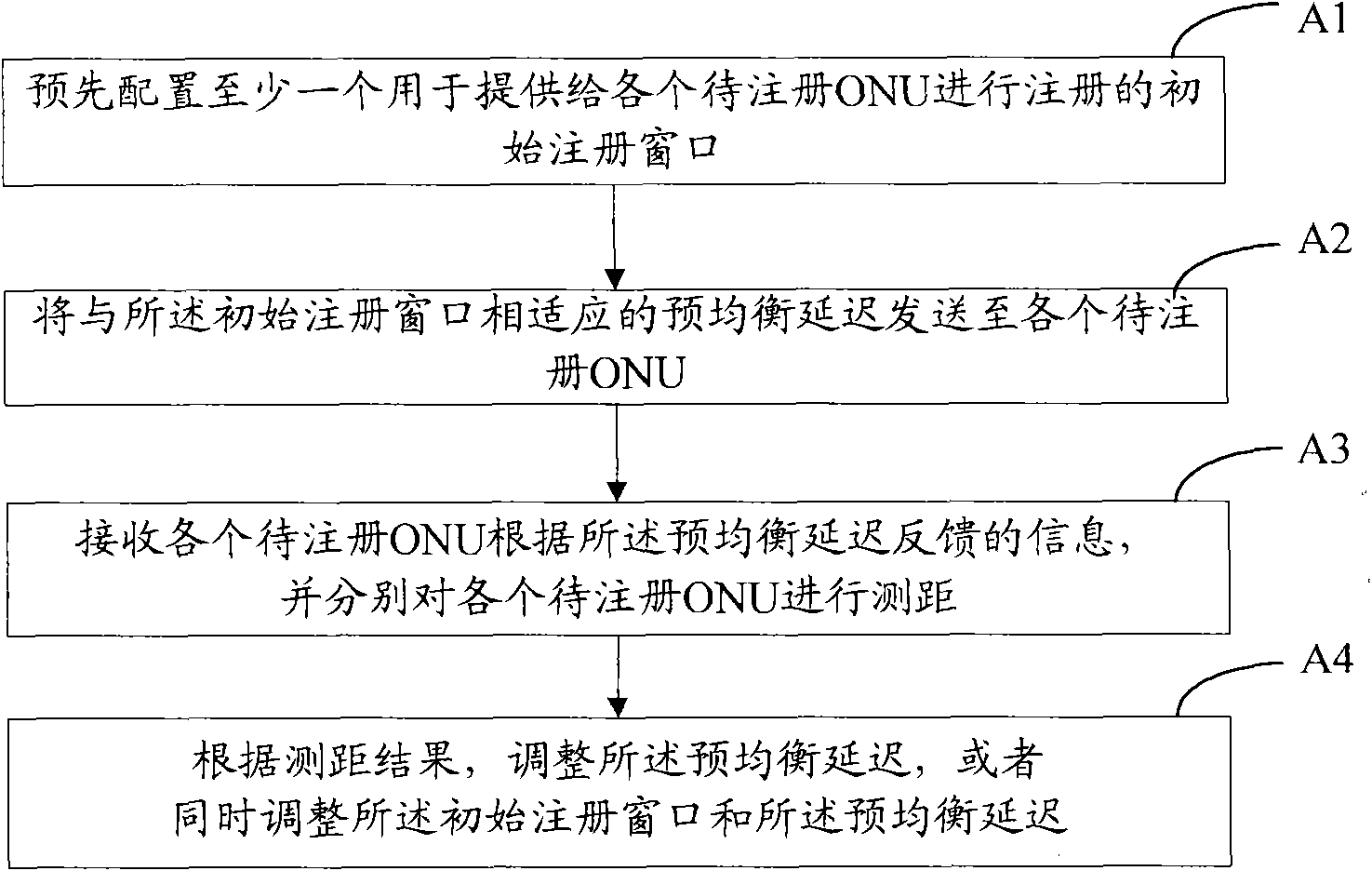

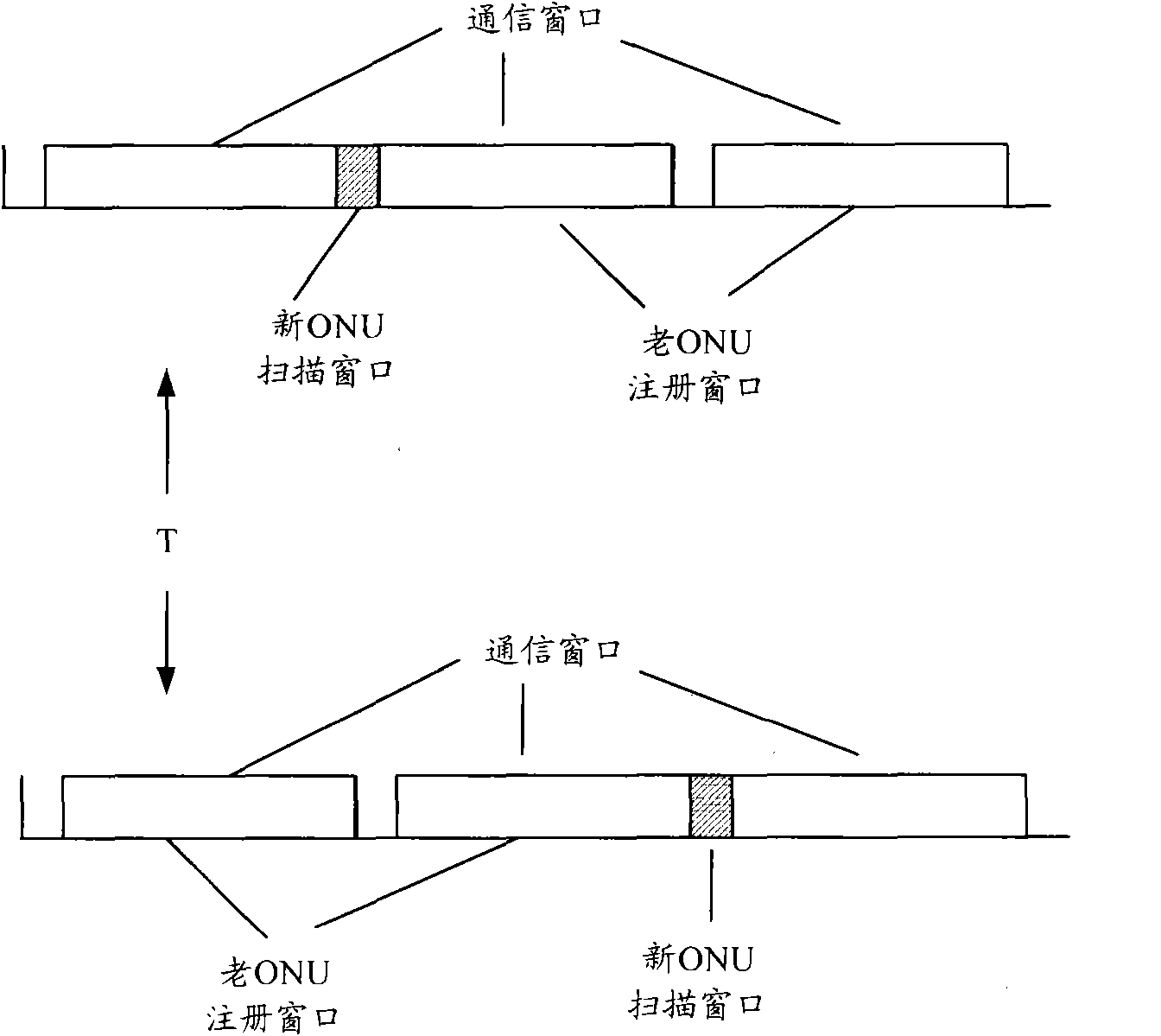

Method, system and device for adjusting register window of passive optical network (PON)

ActiveCN102104428ARealize communicationMultiplex system selection arrangementsTime-division multiplexRegister windowComputer terminal

The embodiment of the invention relates to the technical field of communications and discloses a method, system and device for adjusting a register window of a passive optical network (PON). The method comprises the following steps: sending pre-equalized delay adapting to a preset initial register window to an optical network unit (ONU) to be registered; receiving information fed back by the ONU to be registered in accordance with the pre-equalized delay, and carrying out range measurement on the ONU to be registered; according to a range measurement result, adjusting the pre-equalized delay and sending the adjusted pre-equalized delay to the ONU to be registered, or simultaneously adjusting the initial register window and the pre-equalized delay, and sending the adjusted pre-equalized delay to the ONU to be registered; and receiving registration information sent by the ONU to be registered in accordance with the adjusted pre-equalized delay, and carrying out interaction with the ONU to be registered so as to register the ONU to be registered. According to the embodiment of the invention, an ONU in the PON can be ensured to carry out normal communication with an optical line terminal (OLT).

Owner:HUAWEI TECH CO LTD

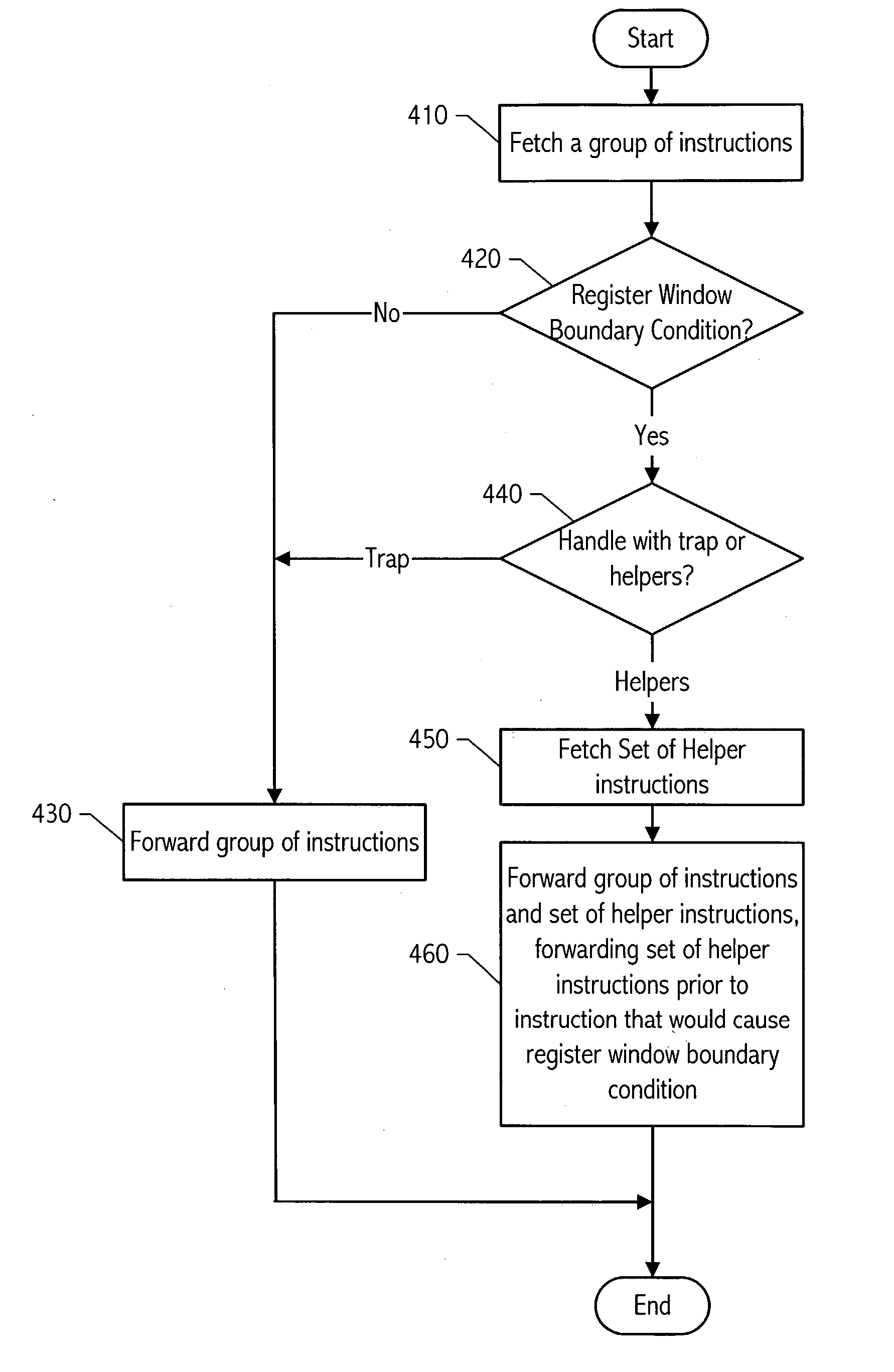

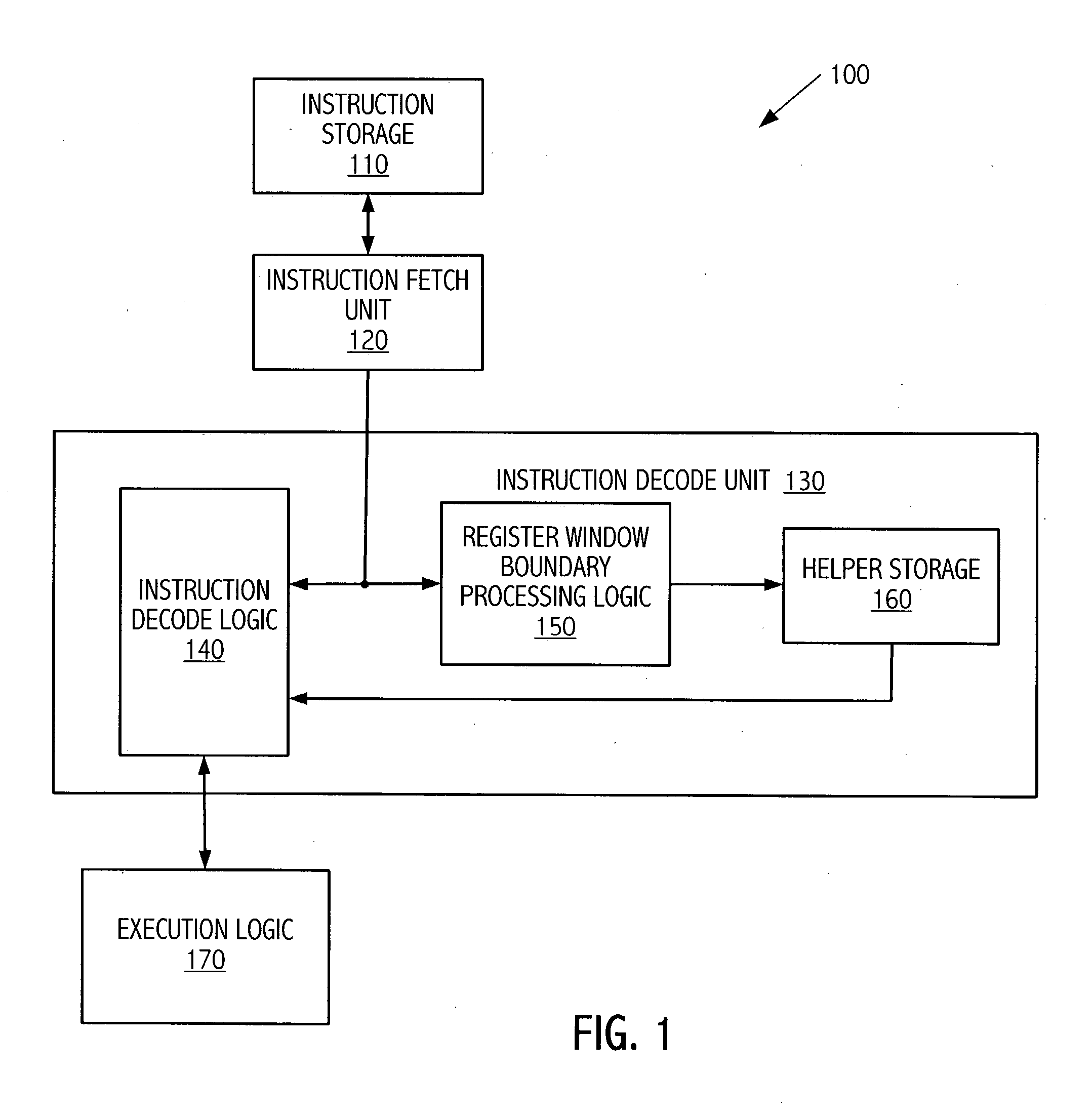

Method and system to handle register window fill and spill

InactiveUS20040215941A1Digital computer detailsConcurrent instruction executionRegister windowParallel computing

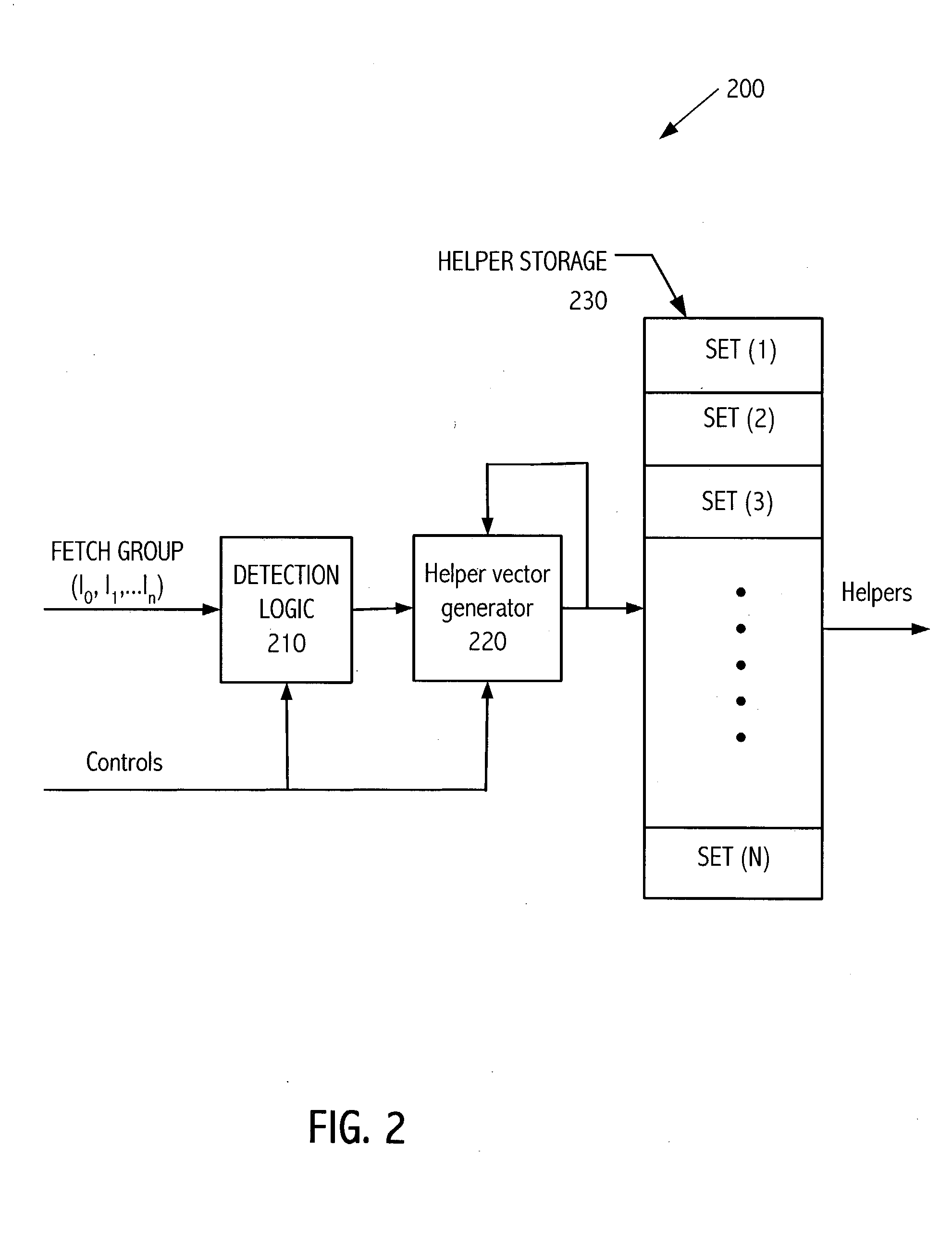

A technique for handling window-fill and / or window-spill operations that improves the performance of a processor over traditional techniques is presented. The window-fill and window-spill operations can be handled in hardware using helper instructions (helpers) prior to the generation of a trap (exception). Fetched instructions are examined prior to forwarding for execution to detect a potential register window boundary condition necessitating, for example, a window-fill or window-spill operation. Vectors are generated for a helper storage within the processor to retrieve helpers for resolving the condition. The helpers are forwarded for execution prior to the instruction that would cause the condition. In some embodiments, to improve the processing, individual helper storages are implemented for every condition. The use of helpers to resolve a register window boundary condition eliminates the generation of a trap and the use of trap handler code.

Owner:SUN MICROSYSTEMS INC

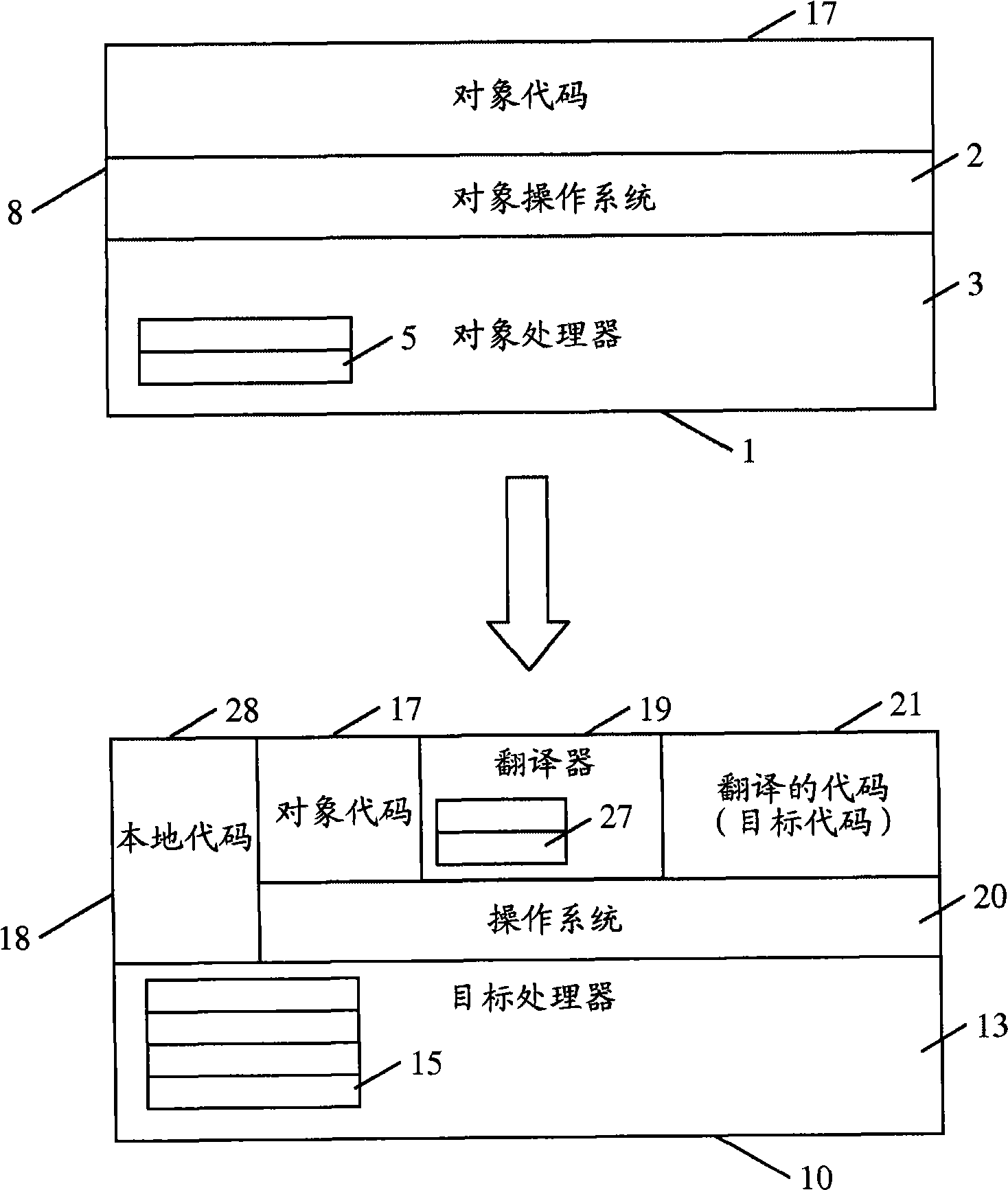

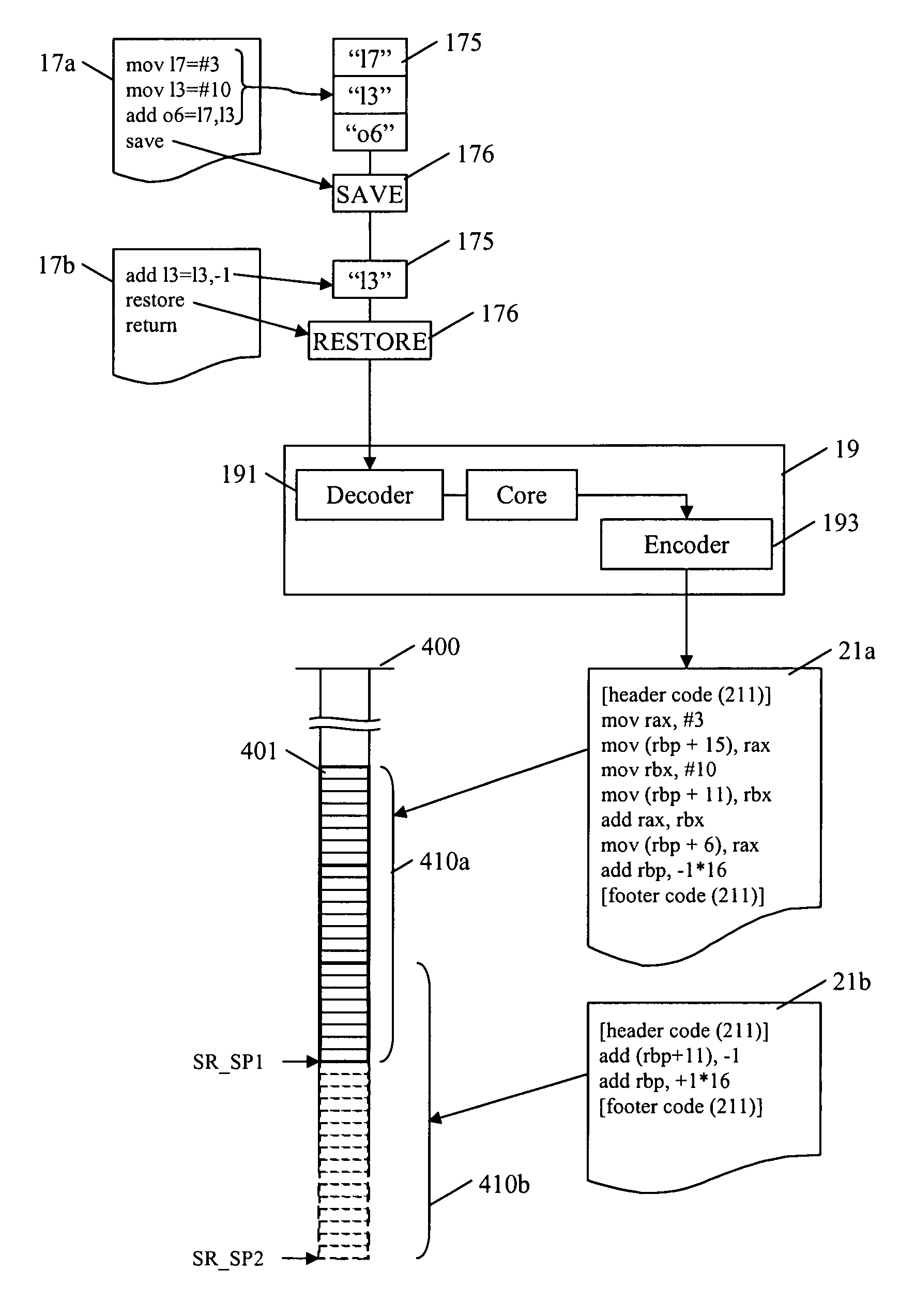

Computer system and method of adapting a computer system to support a register window architecture

ActiveUS20080209175A1Avoid expensiveEasy to operateLink editingDigital computer detailsGeneral purposeComputer architecture

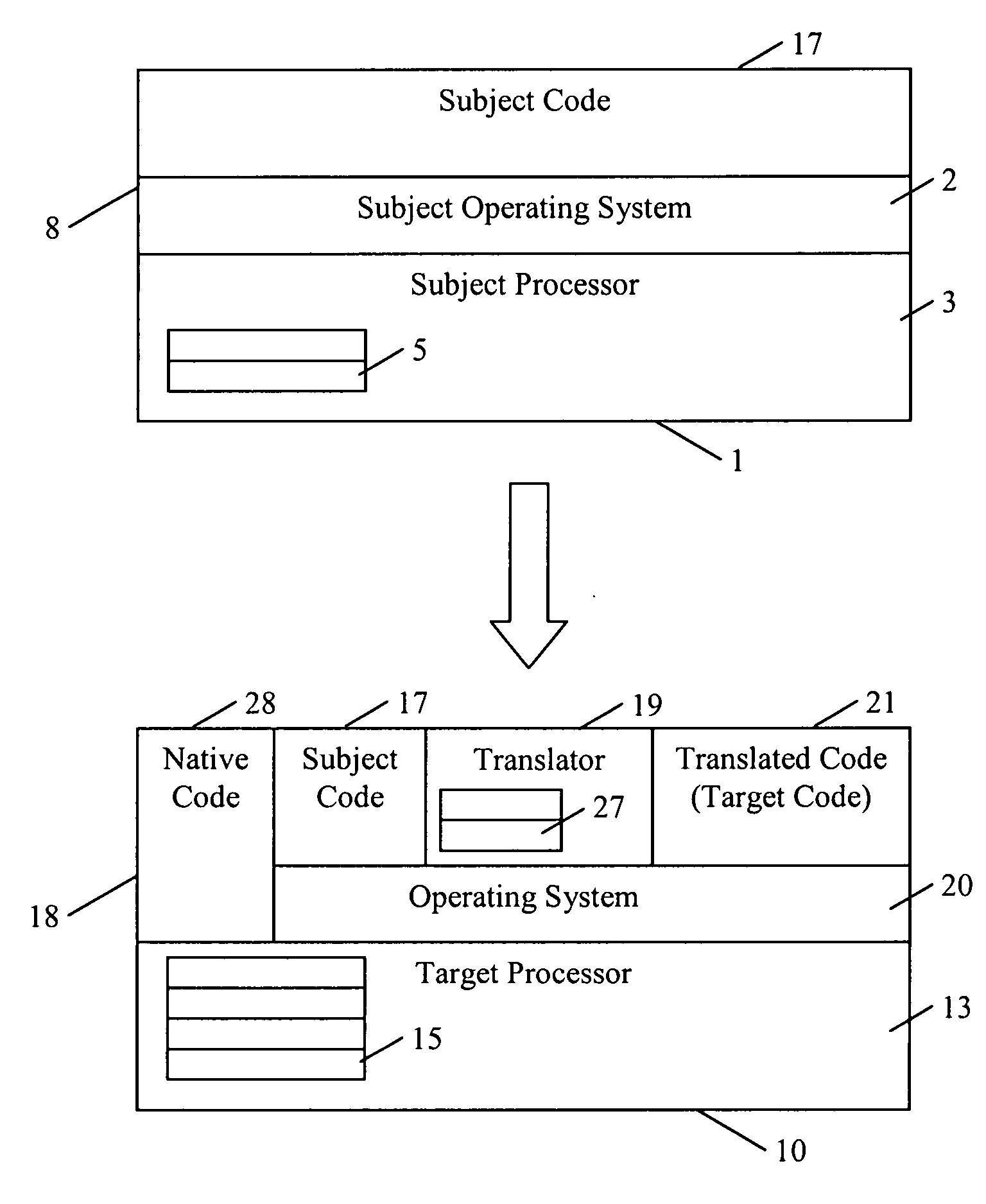

A target computing system 10 is adapted to support a register window architecture, particularly for use when converting non-native subject code 17 instead into target code 21 executed by a target processor 13. A subject register stack data structure (an “SR stack”) 400 in memory has a plurality of frames 410 each containing a set of entries 401 corresponding to a subset of subject registers 502 of one register window 510 in a subject processor 3. The SR stack 400 is accessed by the target code 21 executing on the target processor 13. The SR stack 400 stores a large plurality of such frames 410 and thereby avoids overhead such as modelling automatic spill and fill operations from the windowed register file of the subject architecture. In one embodiment, a target computing system 10 having sixteen general purpose working registers is adapted to support a register window architecture reliant upon a register file containing tens or hundreds of subject registers 502.

Owner:IBM CORP

Register file in the register window system and controlling method thereof

InactiveUS7093110B2Improve information processing abilityDigital computer detailsConcurrent instruction executionRegister windowRegister file

Owner:FUJITSU LTD

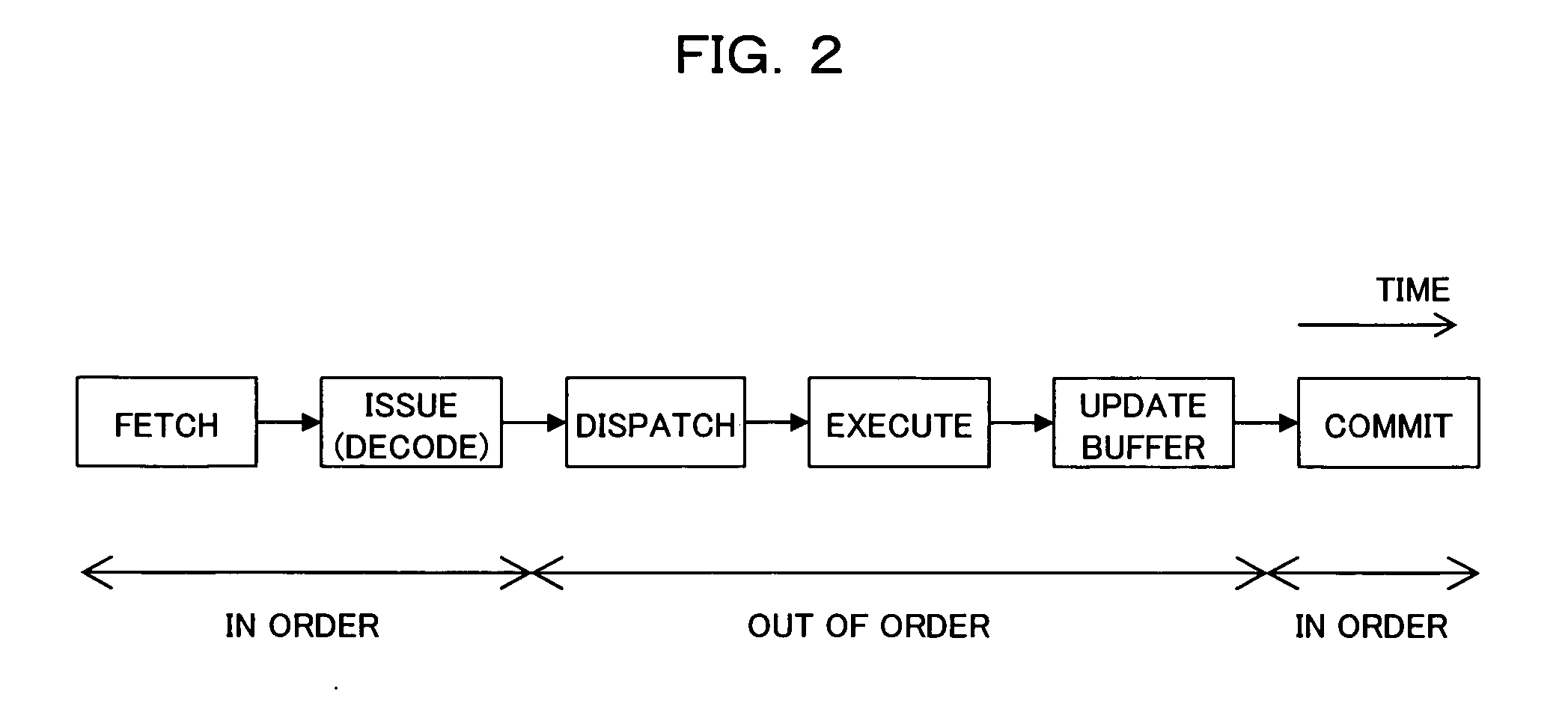

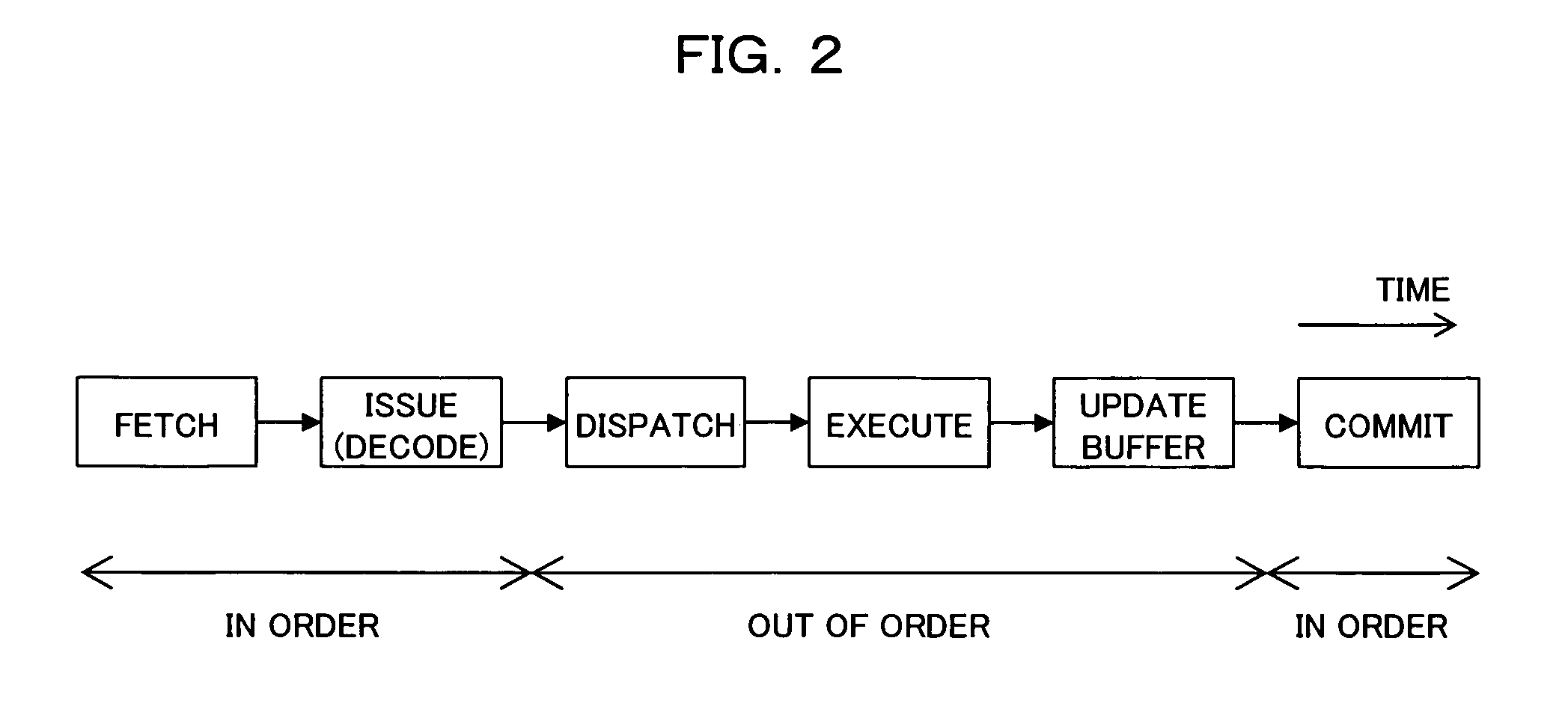

Method and apparatus to handle window management instructions without post serialization in an out of order multi-issue processor supporting multiple strands

ActiveUS7203821B2Digital computer detailsConcurrent instruction executionRegister windowParallel computing

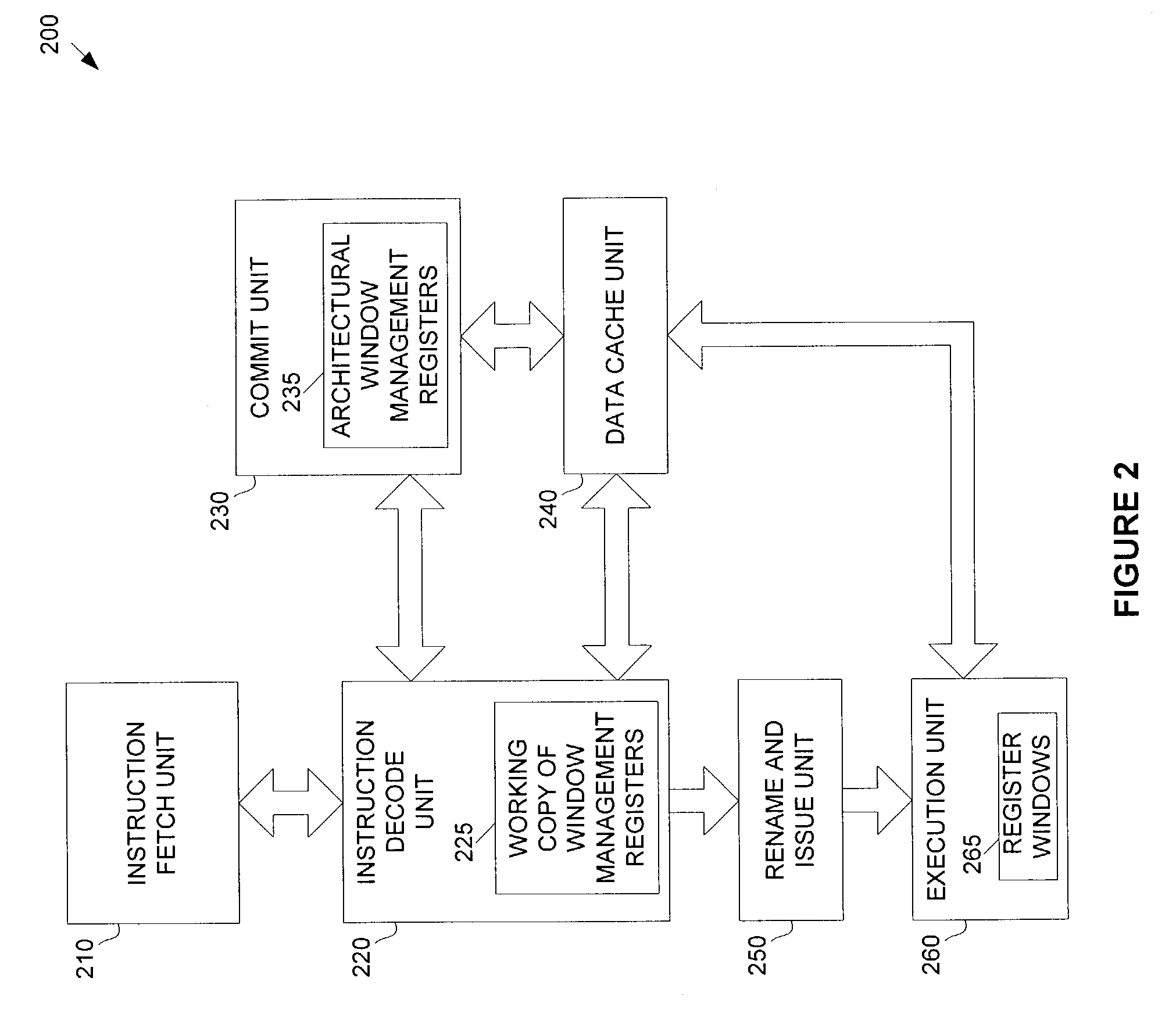

A method and apparatus for handling window management instructions without post serialization in an out-of-order multi-issue processor includes an instruction decode unit arranged to decode the window management instruction. A plurality of register windows are indexed by a current window pointer, and a working copy of the current window pointer is stored in a register in the instruction decode unit. The instruction decode unit uses the working copy of the current window pointer to handle the window management instruction.

Owner:ORACLE INT CORP

Processor transferring multiple working register windows transfers global registers only for select exception handling

InactiveUS7210027B2Improve executionReduce the amount requiredProgram initiation/switchingDigital computer detailsRegister windowData transmission

Owner:FUJITSU LTD

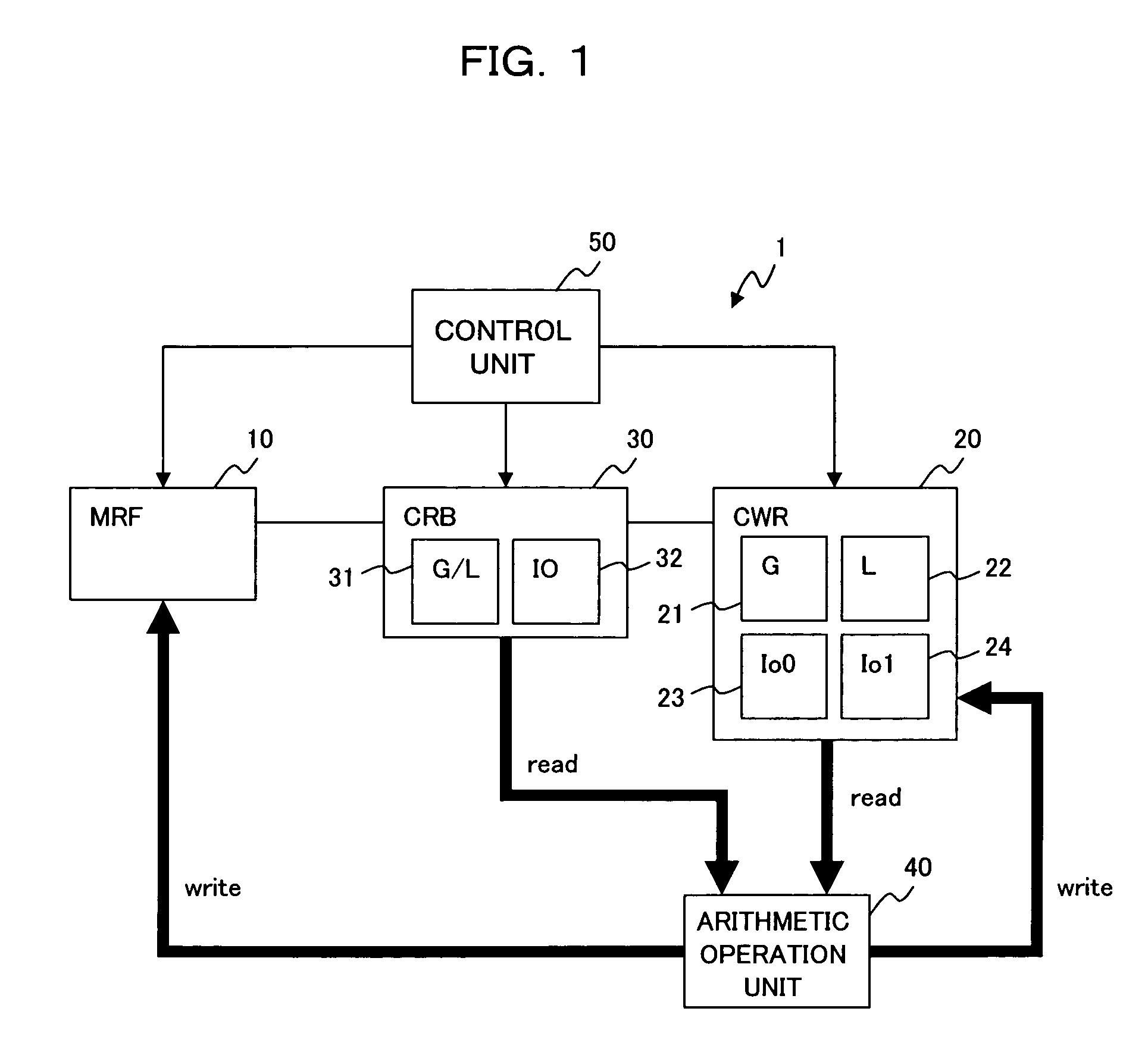

Arithmetic operation apparatus, information processing apparatus, and register file control method

InactiveUS20070067612A1Reduced hardware resourceImprove data read throughputLife-buoysDigital computer detailsInformation processingRegister window

The present apparatus reduces hardware resources and improves data read throughput in an information processing apparatus employing the out-of-order instruction execution method. The apparatus includes: an arithmetic operation unit which executes a window switching instruction and an instruction relating to data stored in the current register or data held in the replacing buffer; and a control unit which transfers, if a window switching instruction is decoded at execution of the window switching instruction by the arithmetic operation unit, data of the register window which is to be specified by the current window pointer upon completion of execution of the window switching instruction, to the replacing buffer.

Owner:FUJITSU LTD

System for protecting sensitive data from user code in register window architecture

InactiveUS7681000B2Digital data processing detailsAnalogue secracy/subscription systemsComputer hardwareRegister window

A system for protecting supervisor mode data from user code in a register window architecture of a processor is provided. The system, when transitioning from supervisor mode to user mode, setting at least one invalid window bit in the invalid window mask of the architecture additional to the invalid window bit set for the reserved window of the invalid window mask. The additional bit is set for a transition window between supervisor and user data windows.

Owner:MEMJET TECH LTD

Arithmetic processing unit

InactiveUS20080229080A1Register arrangementsDigital computer detailsArithmetic processing unitRegister window

An arithmetic processing unit includes a register file provided with multiple register windows, an arithmetic executor executes an instruction with data retained in the register file as an operand, and a current window pointer which retains address information specifying a register window which becomes a current window, and a controller. The controller controls the address information retained by the current window pointer is updated, when a window switching instruction for indicating switching of the current window has been decoded. The arithmetic executor reads data in a first register window specified by the address information before being updated and data in a second register window specified by the updated address information from the register file, after the decoding of said window switching instruction has been started until commit of the window switching instruction is started.

Owner:FUJITSU LTD

Computer system and method of adapting a computer system to support a register window architecture

ActiveCN101523349AEasy to operateSoftware simulation/interpretation/emulationGeneral purposeRegister window

A target computing system (10) is adapted to support a register window architecture, particularly for use when converting non-native subject code (17) instead into target code (21) executed by a target processor (13). A subject register stack data structure (an ''SR stack'') (400) in memory has a plurality of frames (410) each containing a set of entries (401) corresponding to a subset of subject registers (502) of one register window (510) in a subject processor (3). The SR (10) stack (400) is accessed by the target code (21) executing on the target processor (13). The SR stack (400) stores a large plurality of such frames 410 and thereby avoids overhead such as modelling automatic spill and fill operations from the windowed register file of the subject architecture. In one embodiment, a target computing system (10) having sixteen general purpose working registers is adapted to support a register window architecture reliant upon a (15) register file containing tens or hundreds of subject registers (502).

Owner:IBM CORP

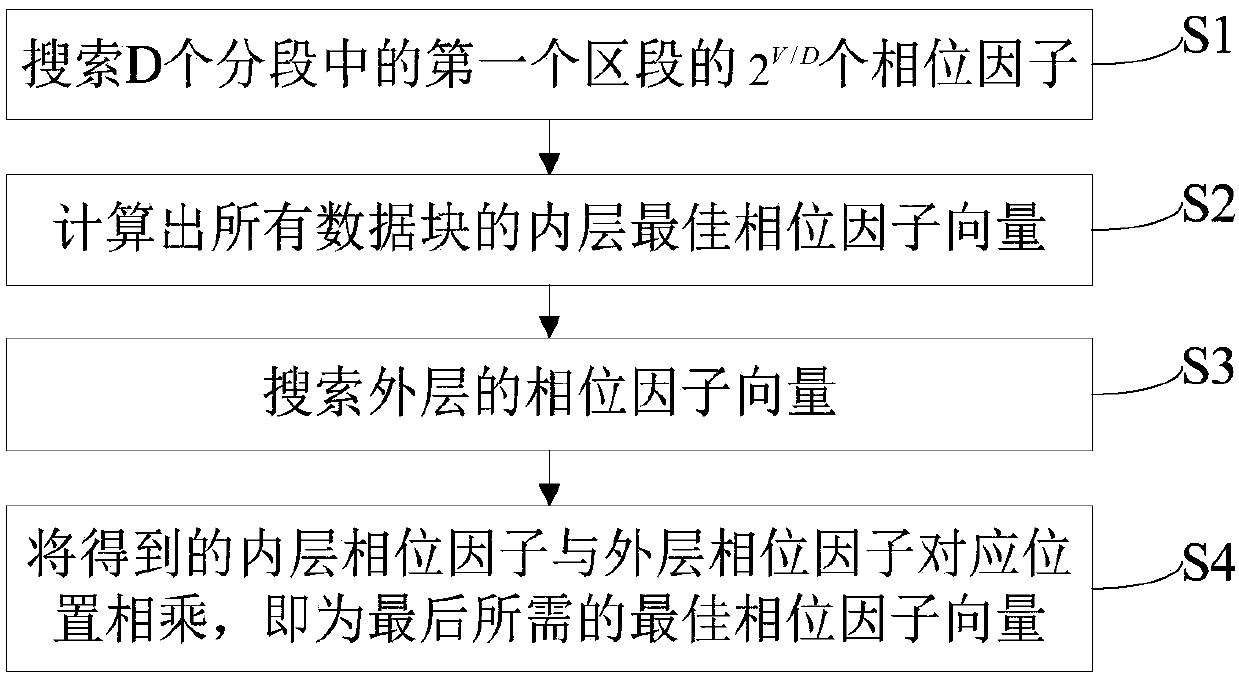

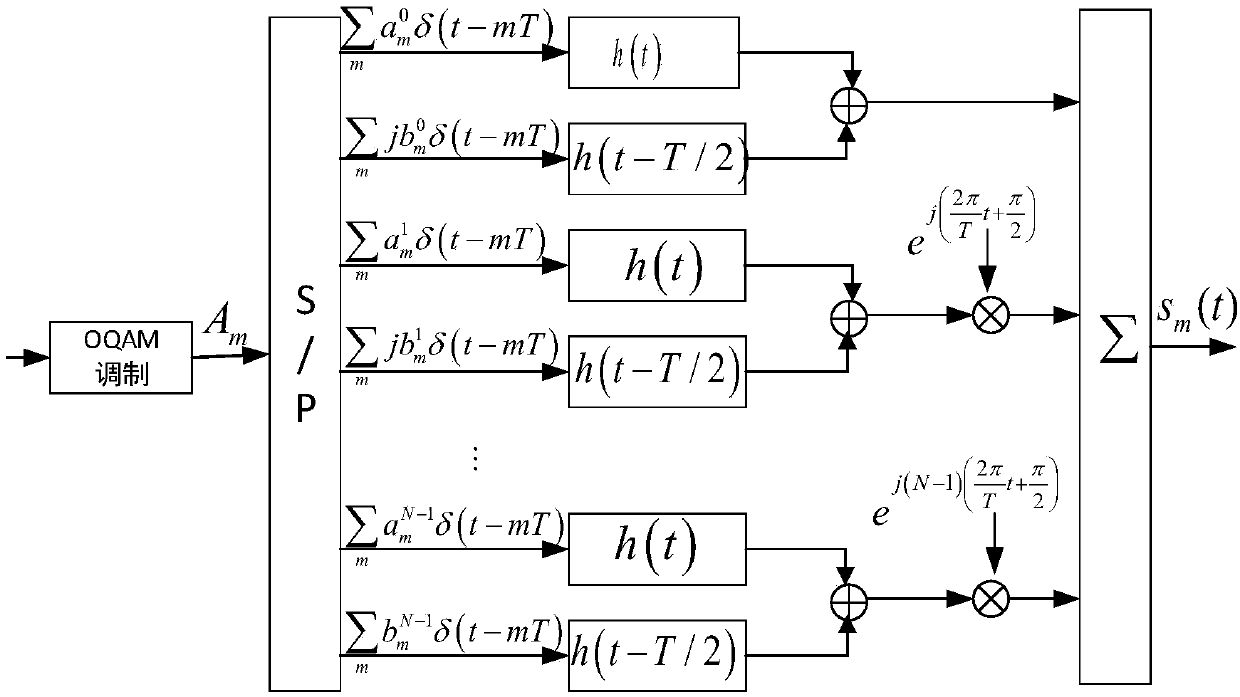

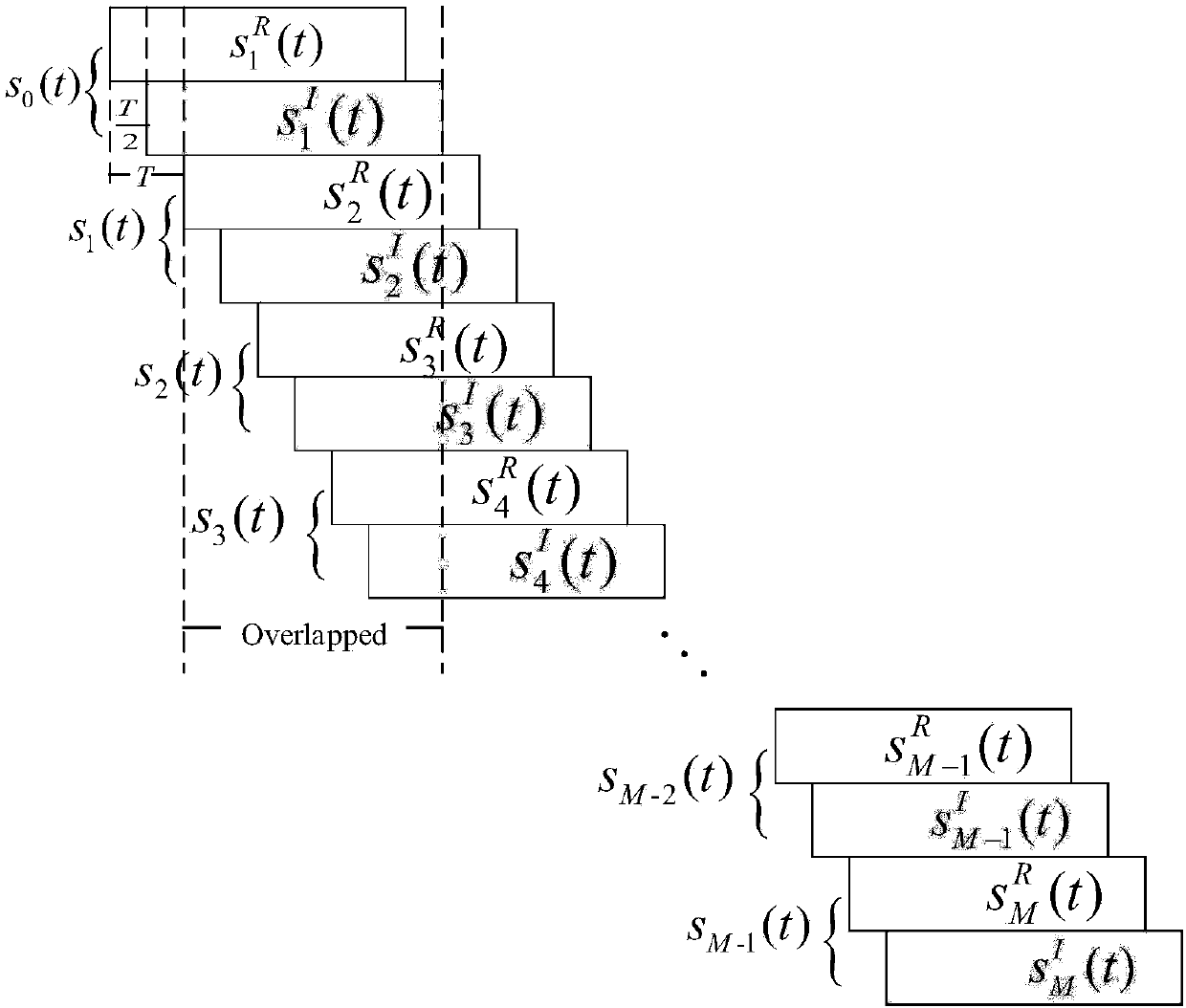

Method for inhibiting high peak-to-average power ratio of FBMC-OQAM system

InactiveCN107911330AEnhanced inhibitory effectExpand your searchMulti-frequency code systemsMultiple carrier systemsRegister windowPhase factor

The invention relates to the technical field of wireless communication, and particularly relates to a method for inhibiting a high peak-to-average power ratio of an FBMC-OQAM system. The method comprises the following steps: searching a phase factor of a first section in D sections; calculating optimal phase factor vectors of inner layers of all data blocks; searching phase factor vectors of outerlayers; and multiplying the obtained phase factor vectors of inner layers with the phase factor vectors of outer layers at corresponding positions to obtain the finally necessary optimal phase factorvector. According to the method, the phase factors are divided into odd and even vectors to iterate separately, thereby enlarging the search range and seeking the optimal solution, then in combination with the FBMC-OQAM system, the overlapped parts of the data blocks are used, so that the phase factor vector with the minimum PARP of the sum of a weighted signal of the current symbol block and thesignal in a register window is used as the optimal phase factor vector, then the performance of the PAPR is inhibited without increasing the calculation amount.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

Data processing apparatus

InactiveUS20060020777A1Improving execution cycleAmount of transmission data can be reducedDigital computer detailsConcurrent instruction executionRegister windowData transmission

In a data processing apparatus using a register window method performing data transmission from a master register to a work register during an exception handling, detecting a trap, discriminating whether or not a data transmission is required for the global registers by the trap, and transmitting data from the master register to the work register for only the global registers if the trap requires transmitting data for the global registers, thereby providing the data processing apparatus performing data transmission to the global registers if the occurring trap requires data for the global registers.

Owner:FUJITSU LTD

Register window system and method that stores the next register window in a temporary buffer

InactiveUS7343478B2Improve data read throughputReduced hardware resourceLife-buoysDigital computer detailsInformation processingRegister window

The present apparatus reduces hardware resources and improves data read throughput in an information processing apparatus employing the out-of-order instruction execution method. The apparatus includes: an arithmetic operation unit which executes a window switching instruction and an instruction relating to data stored in the current register or data held in the replacing buffer; and a control unit which transfers, if a window switching instruction is decoded at execution of the window switching instruction by the arithmetic operation unit, data of the register window which is to be specified by the current window pointer upon completion of execution of the window switching instruction, to the replacing buffer.

Owner:FUJITSU LTD

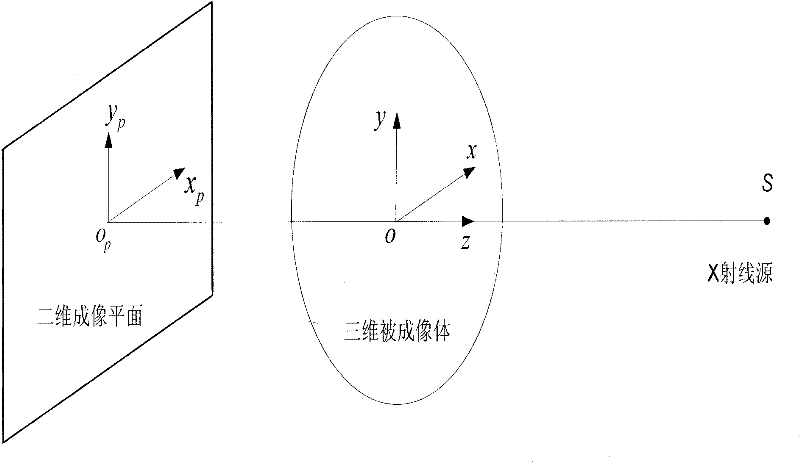

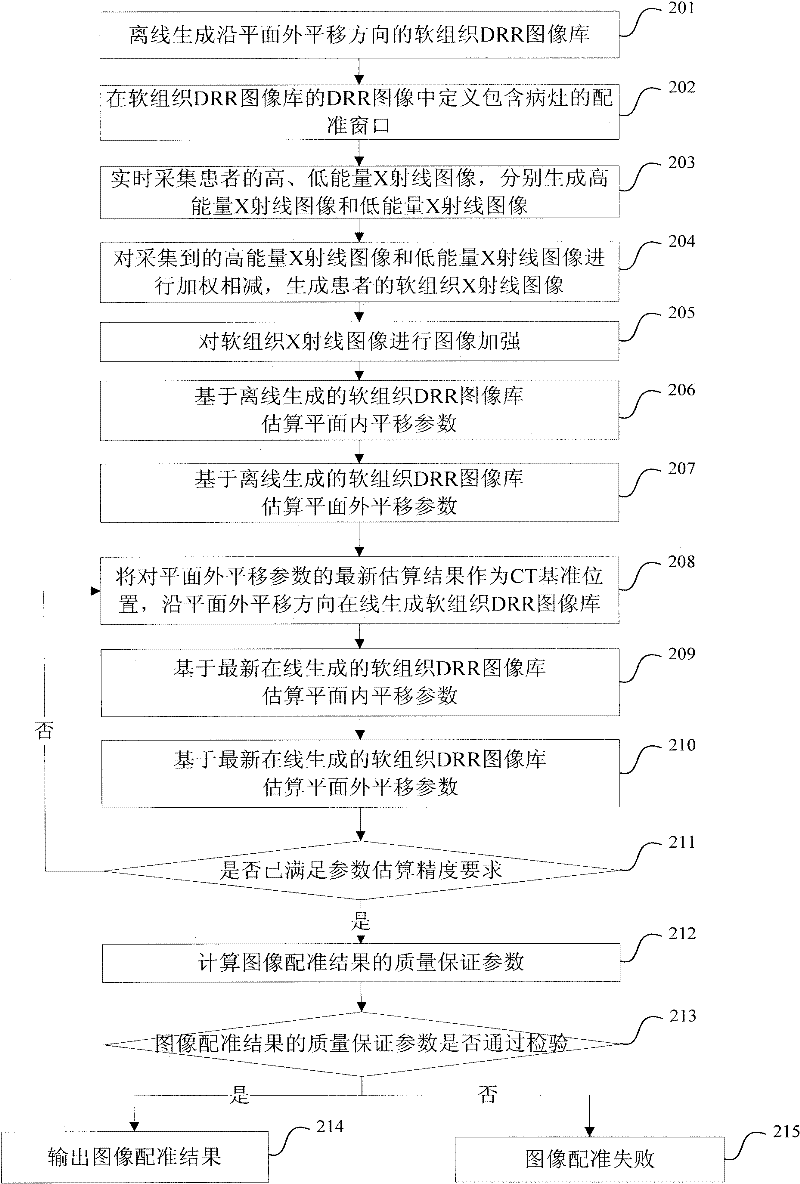

Method and system for positioning soft tissue lesion based on dual-energy X-ray images

The invention discloses a method and system for positioning a soft tissue lesion based on dual-energy X-ray images. The method comprises the following steps of: generating a three-dimensional image of a patient and offline generating a soft tissue DRR (Digitally Reconstructed Radiograph) image library along a plane inside translation direction; acquiring high- and low-energy X-ray images of the patient and generating a soft tissue X-ray image of the patient; taking the soft tissue X-ray image as a registered image and estimating values of a plane inside translation parameter and a plane outside translation parameter by using a registering window including the lesion in the DRR image in the soft tissue DRR image library generated offline; adjusting the three-dimensional image by a newest parameter estimation result for the plane outside translation parameter and generating the soft tissue DRR image library along the plane outside translation direction on line; and taking the soft tissue X-ray image as the registered image and further estimating the values of the plane inside translation parameter and the plane outside translation parameter by using the registering window including the lesion in the DRR image in the soft tissue DRR image library generated on line.

Owner:江苏瑞尔医疗科技有限公司

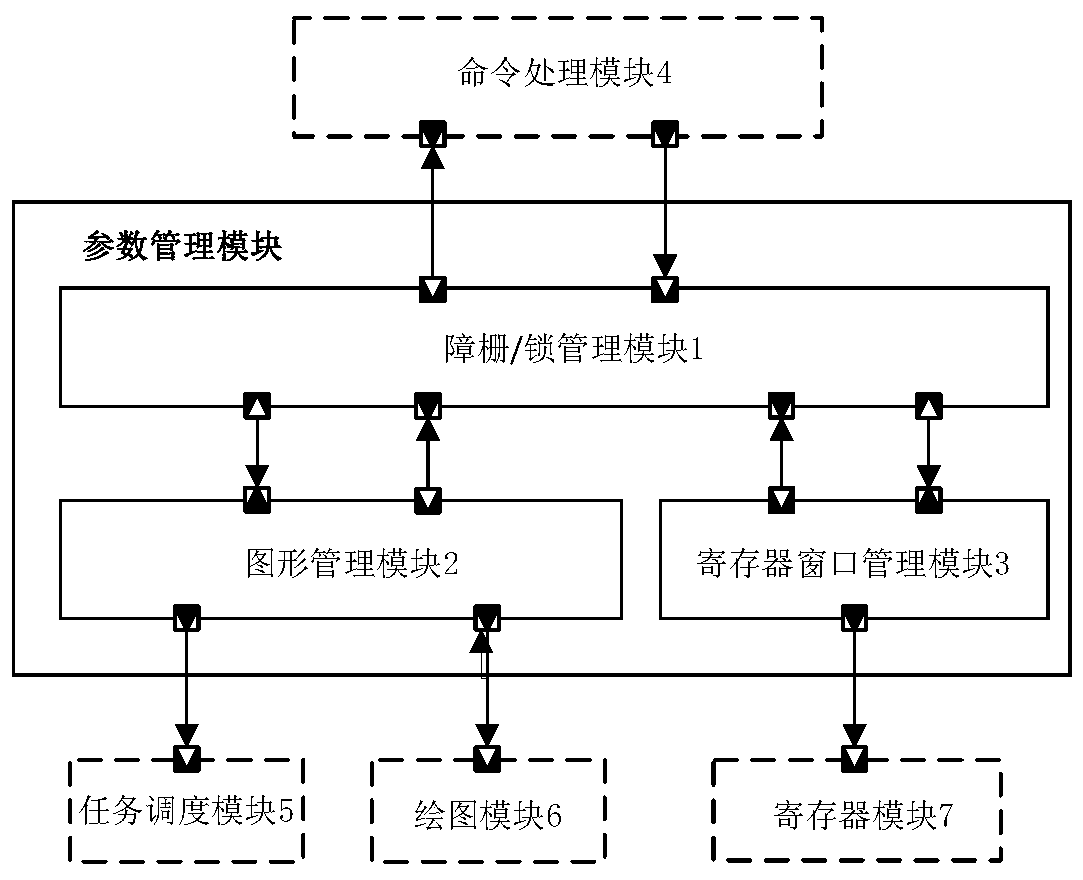

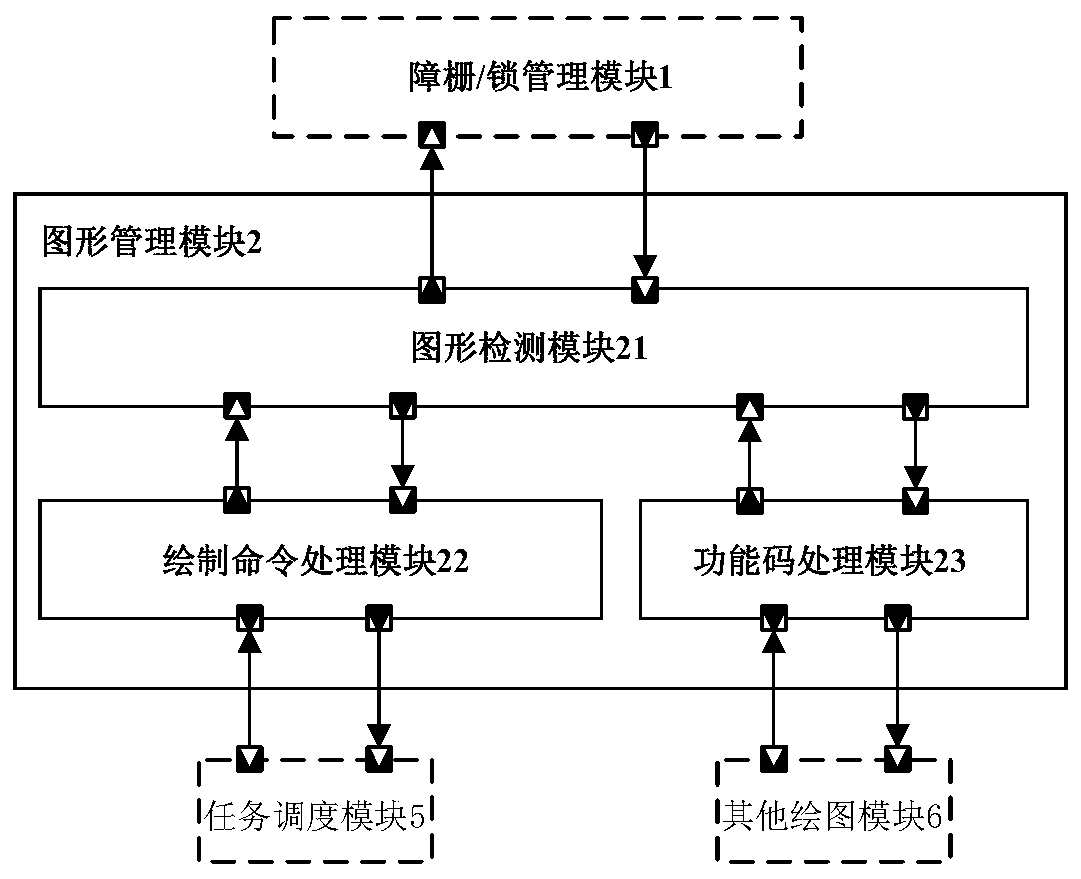

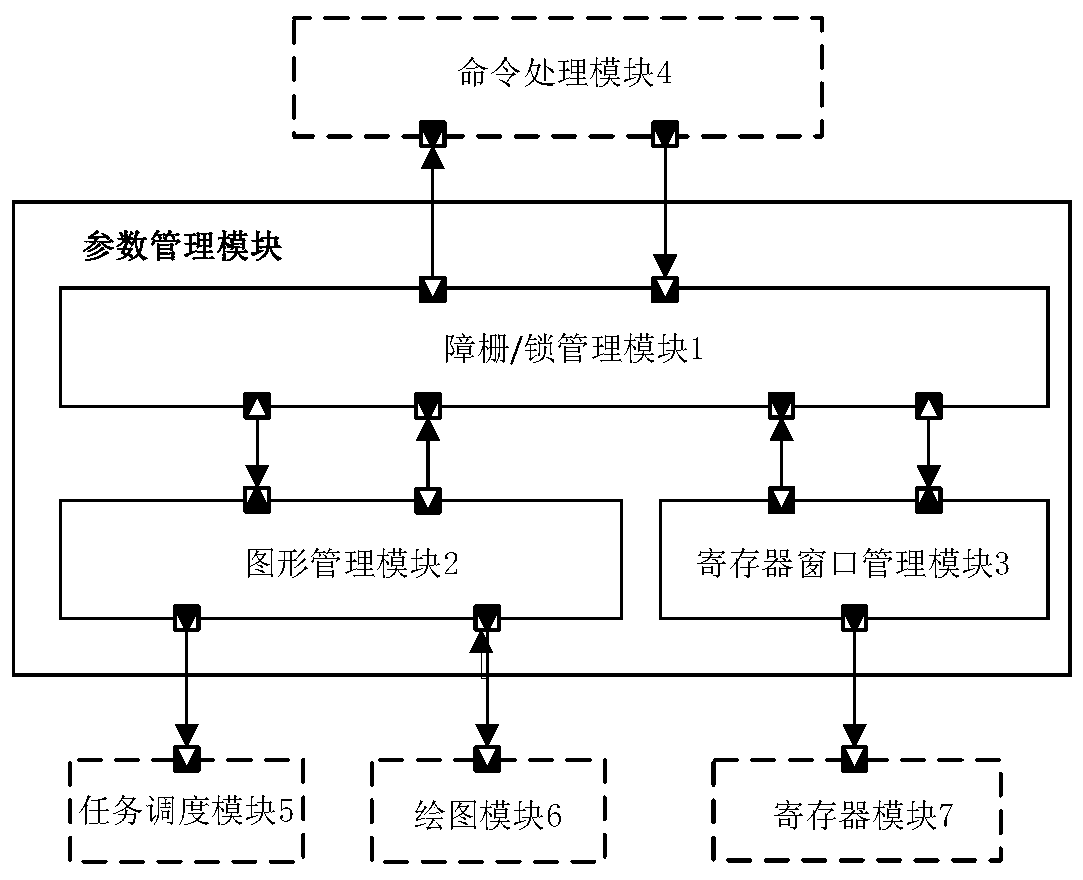

A GPU-oriented parameter management method based on SystemC

ActiveCN109840878ARealize distributionRealize managementMultiprogramming arrangementsProcessor architectures/configurationSystemCGraphics

The invention relates to the technical field of computer hardware modeling. The invention provides a GPU-oriented parameter management method based on SystemC. The method comprises the following steps: step 1, executing barrier / lock management, calculating a new barrier state according to the current barrier state and the FIFO state, when judging that the GraphRegLock is 0, outputting the GraphRegLock to a graphic management module (2) through a transaction-level interface, and executing the step 2, otherwise, outputting the GraphGrawLock to a register window management module (3) through thetransaction-level interface when the GraphGrawLock is 0 and the GraphFunction is 0, and executing the step 3; Step 2, executing graph drawing command parameter and function code parameter management;And step 3, executing read-write management of register parameters.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

Computer system and method of adapting a computer system to support a register window architecture

ActiveUS8001535B2Avoid expensiveEasy to operateLink editingDigital computer detailsGeneral purposeComputer architecture

A target computing system 10 is adapted to support a register window architecture, particularly for use when converting non-native subject code 17 instead into target code 21 executed by a target processor 13. A subject register stack data structure (an “SR stack”) 400 in memory has a plurality of frames 410 each containing a set of entries 401 corresponding to a subset of subject registers 502 of one register window 510 in a subject processor 3. The SR stack 400 is accessed by the target code 21 executing on the target processor 13. The SR stack 400 stores a large plurality of such frames 410 and thereby avoids overhead such as modelling automatic spill and fill operations from the windowed register file of the subject architecture. In one embodiment, a target computing system 10 having sixteen general purpose working registers is adapted to support a register window architecture reliant upon a register file containing tens or hundreds of subject registers 502.

Owner:INT BUSINESS MASCH CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com