Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

32 results about "Bridging fault" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electronic engineering, a bridging fault consists of two signals that are connected when they should not be. Depending on the logic circuitry employed, this may result in a wired-OR or wired-AND logic function. Since there are O(n^2) potential bridging faults, they are normally restricted to signals that are physically adjacent in the design.

System for mapping logical functional test data of logical integrated circuits to physical representation using pruned diagnostic list

InactiveUS6553329B2Digital circuit testingResistance/reactance/impedenceComputer hardwareFunctional testing

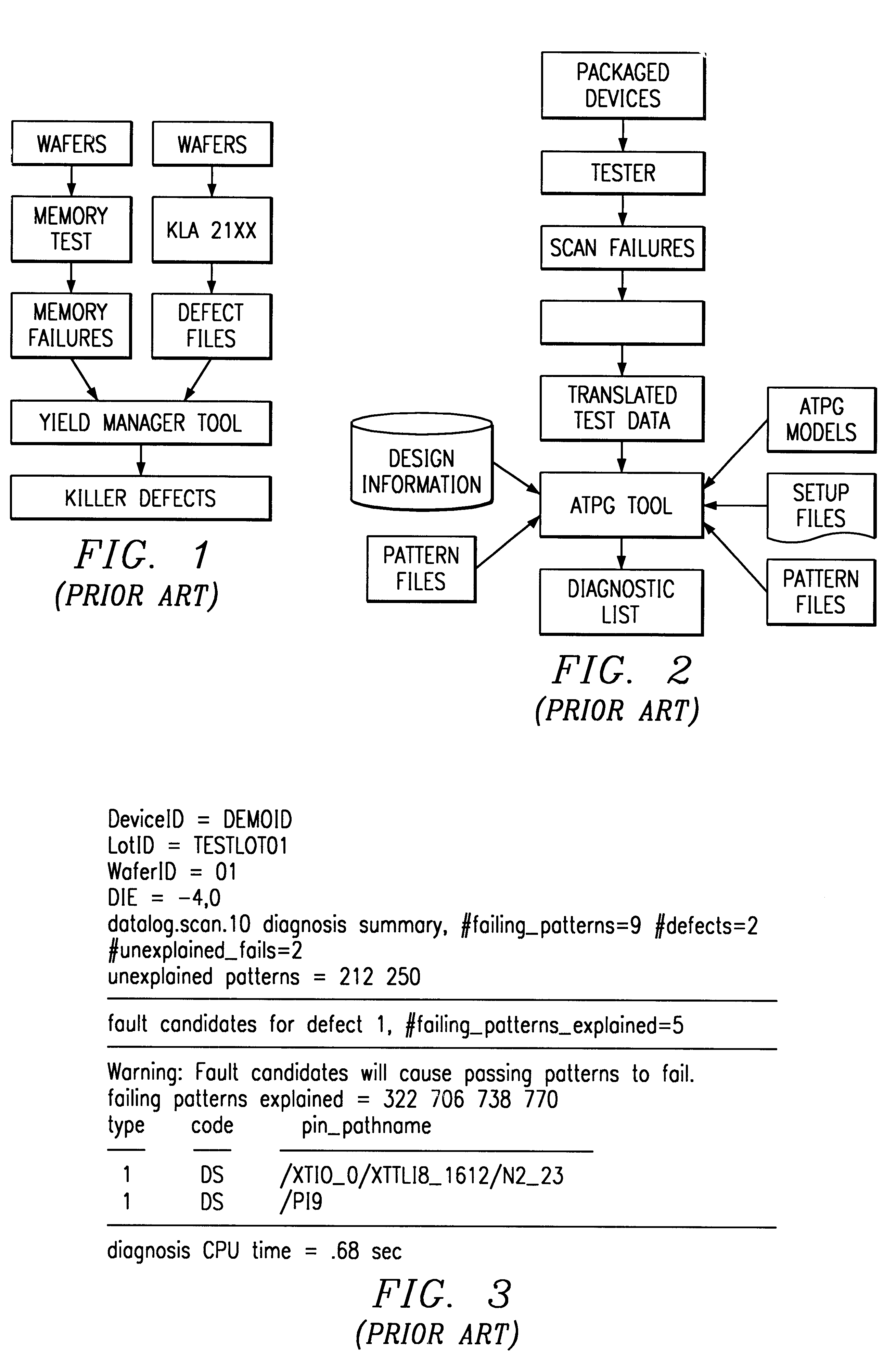

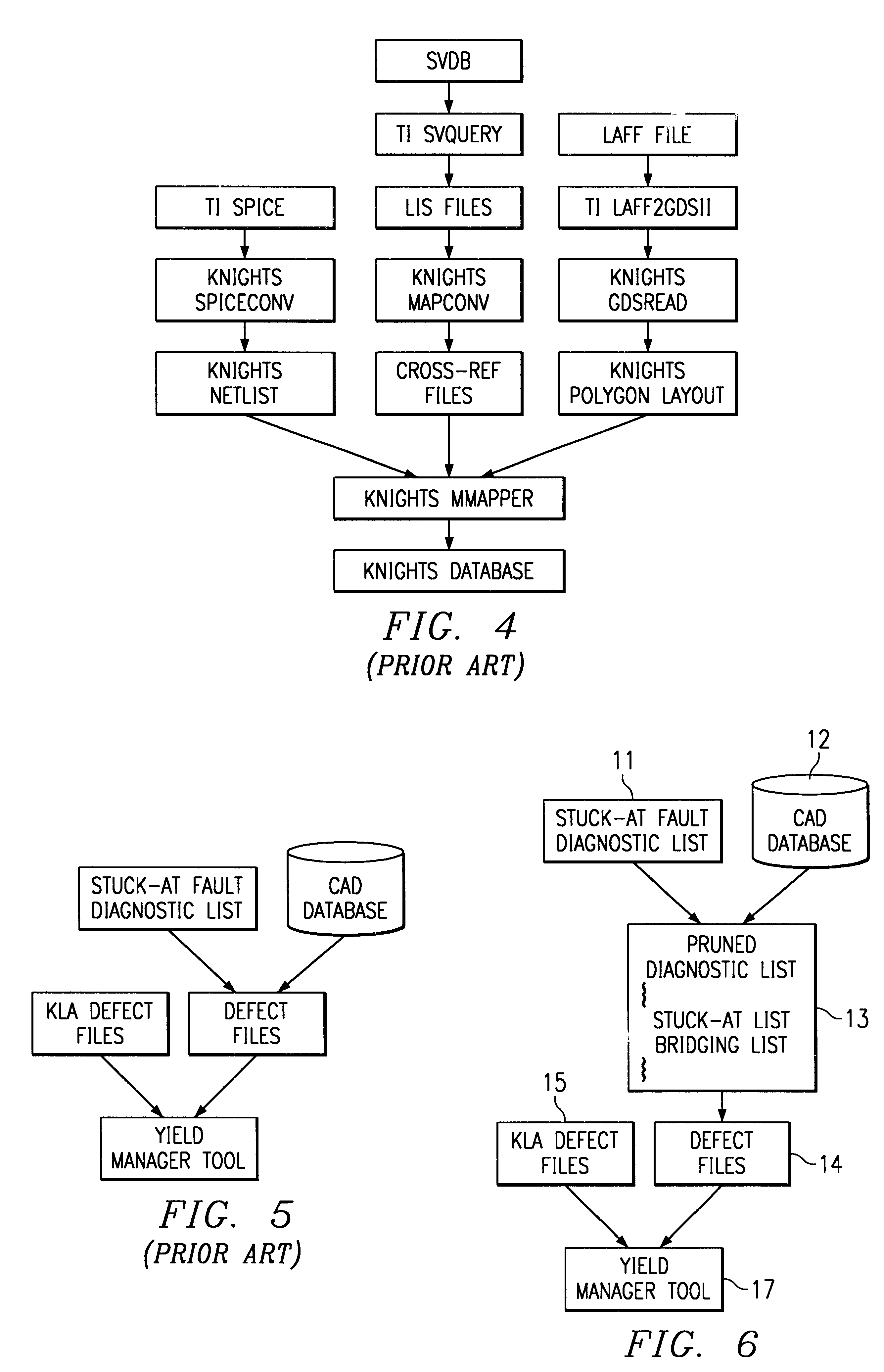

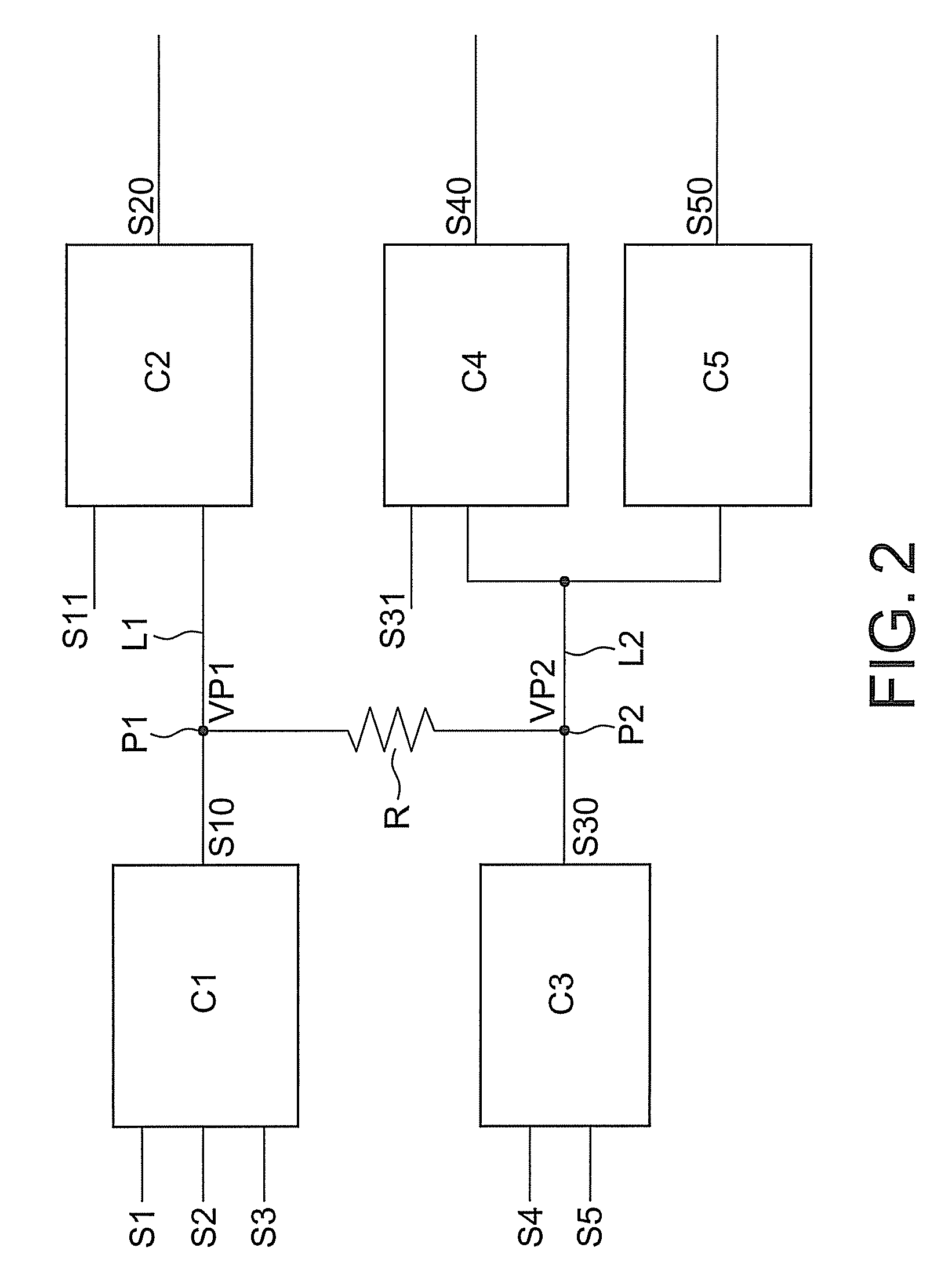

An improved method for mapping logical function test data of logical integrated circuits to physical representations uses a pruned diagnostic list. The steps include creating a final logical diagnostic list of potential bridging faults in response to testing the circuit for stuck-at faults at a plurality of nets of the circuit, receiving the physical data associated with nets of the circuit, applying adjacency criteria to the physical data, generating a pruned diagnostic list of potential bridging faults in response to applying the adjacency criteria, performing in-line inspection to obtain second localized probable defect data and correlating second localized portable defect data with the pruned diagnostic list.

Owner:HARRIS KAYOT +1

System for mapping logical functional test data of logical integrated circuits to physical representation using pruned diagnostic list

InactiveUS20020010560A1Digital circuit testingResistance/reactance/impedenceComputer hardwareFunctional testing

An improved method for mapping logical function test data of logical integrated circuits to physical representations uses a pruned diagnostic list. The steps include creating a final logical diagnostic list of potential bridging faults in response to testing the circuit for stuck-at faults at a plurality of nets of the circuit, receiving the physical data associated with nets of the circuit, applying adjacency criteria to the physical data, generating a pruned diagnostic list of potential bridging faults in response to applying the adjacency criteria, performing in-line inspection to obtain second localized probable defect data and correlating second localized portable defect data with the pruned diagnostic list.

Owner:HARRIS KAYOT +1

Method for monitoring bridge fault on basis of video image

The invention discloses a method for monitoring a bridge fault on the basis of a video image and belongs to the technical field of a bridge monitoring method. The method is characterized by comprising the following steps of: (1) obtaining a video data of a preset position on a bridge; (2) comparing the video data; (3) obtaining a bridge fault condition; and (4) evaluating the use condition of the bridge and early warning. The invention aims to provide a high-detection-efficiency, high-accuracy and low-cost method for monitoring the bridge fault on the basis of the video image. The method is used for monitoring the bridge fault in real time.

Owner:广东省公路管理局

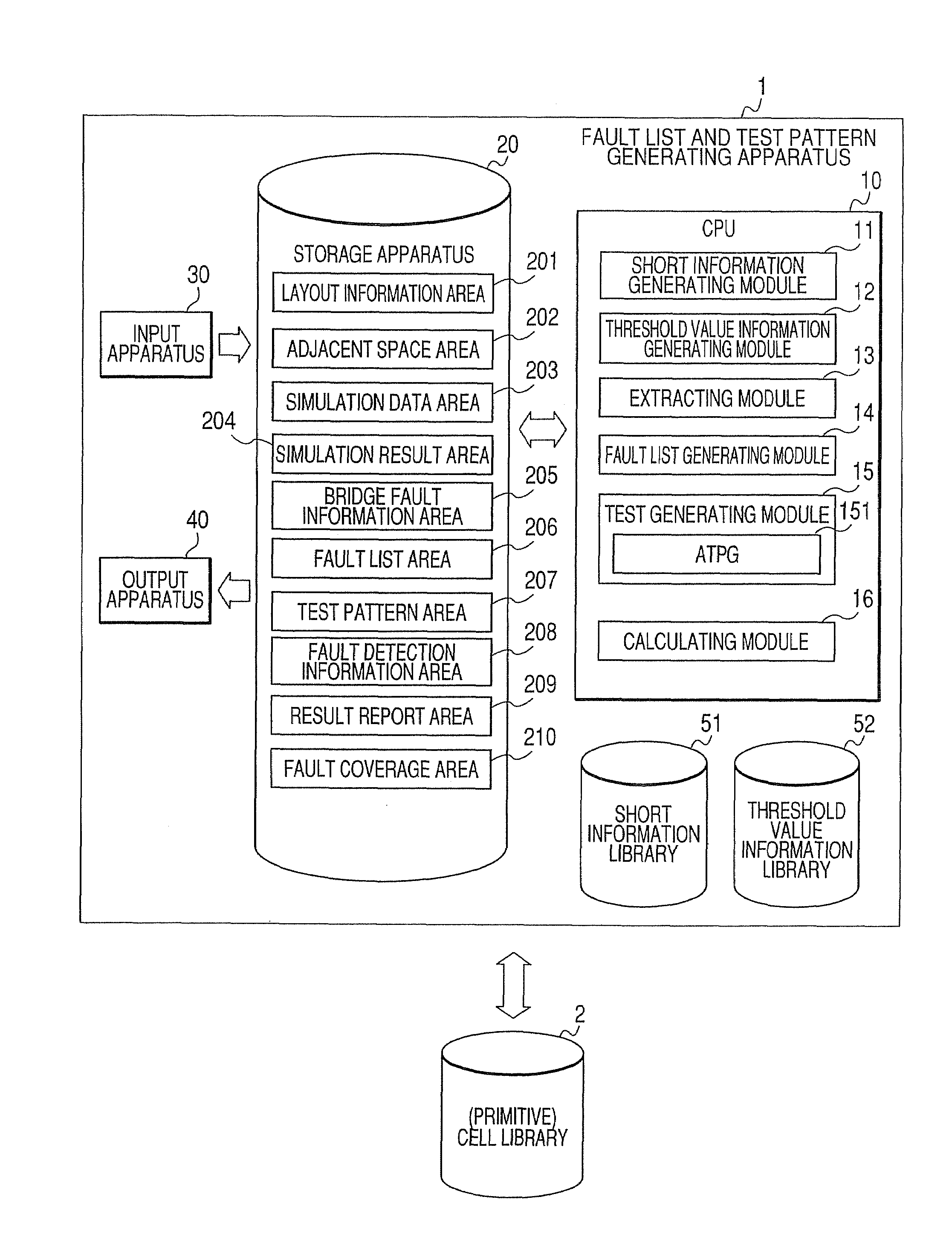

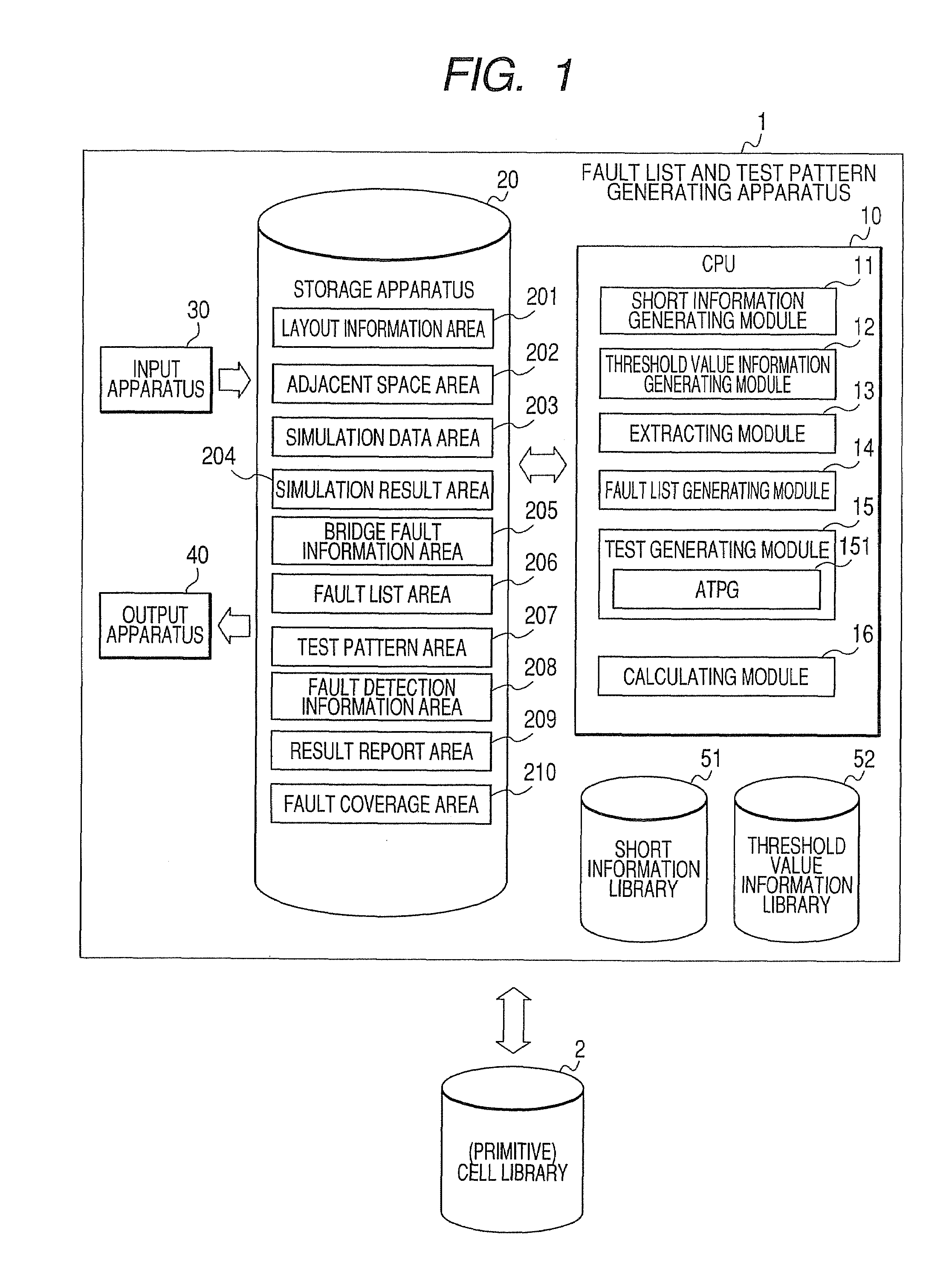

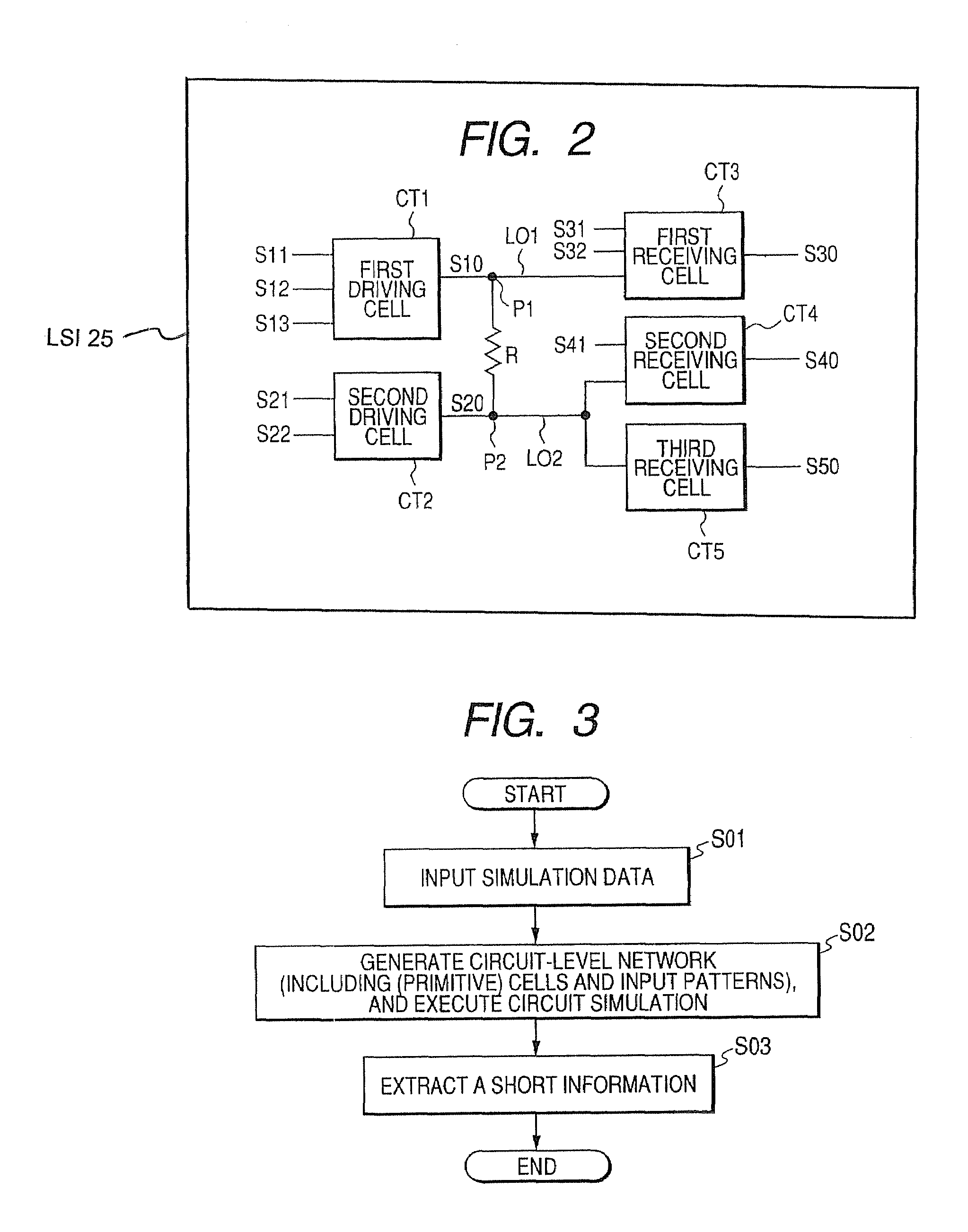

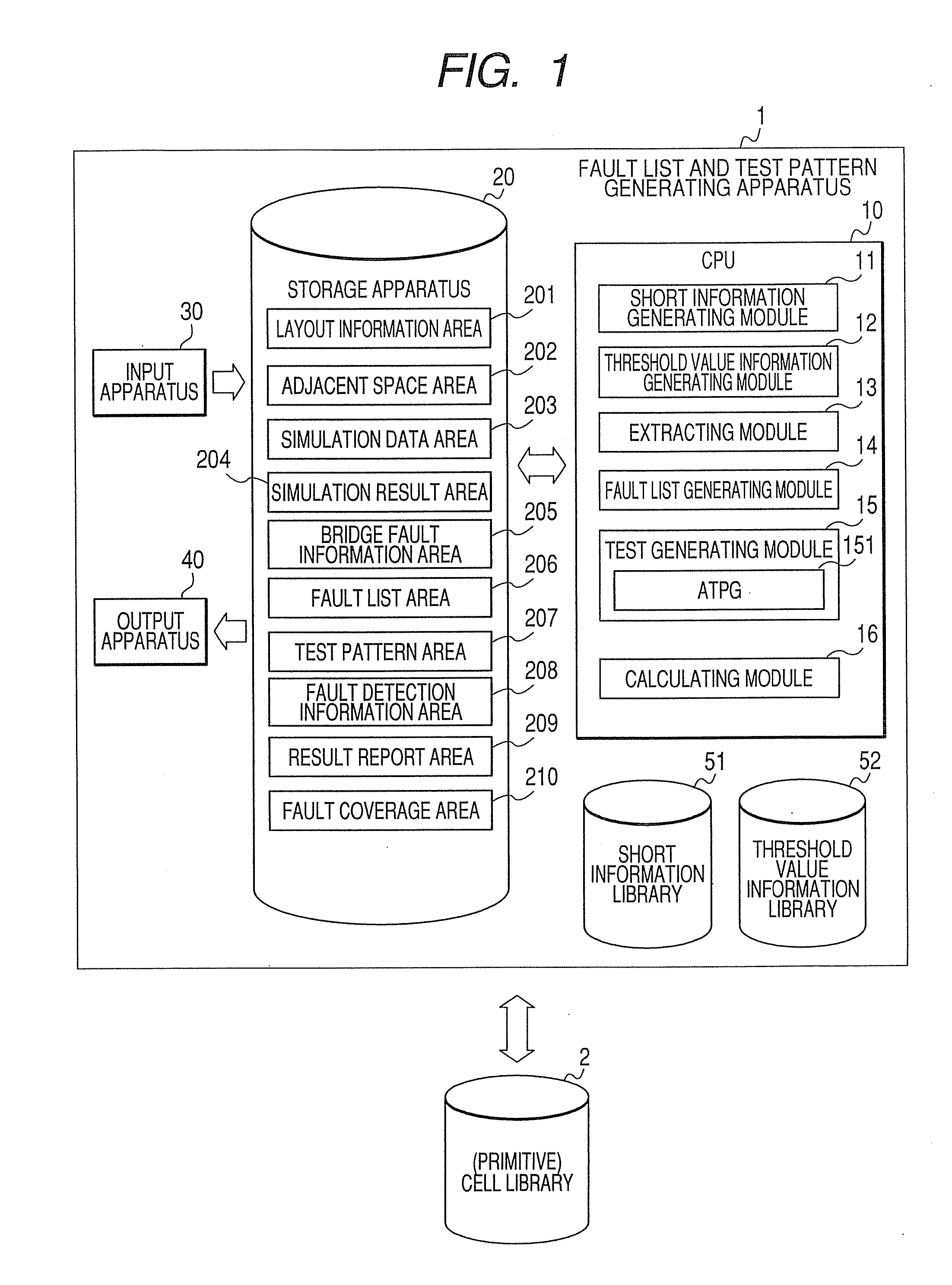

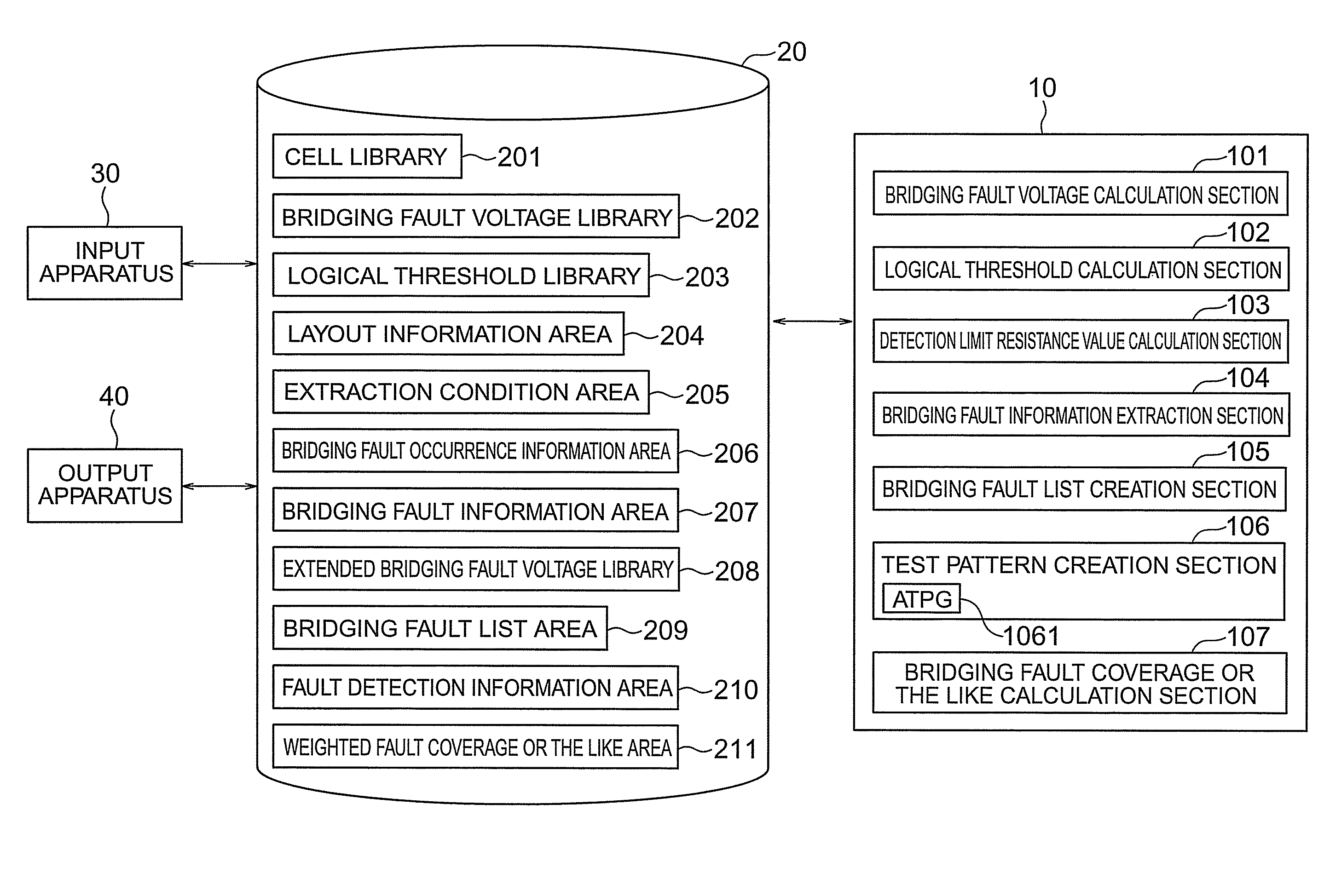

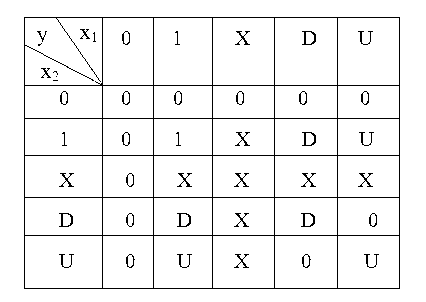

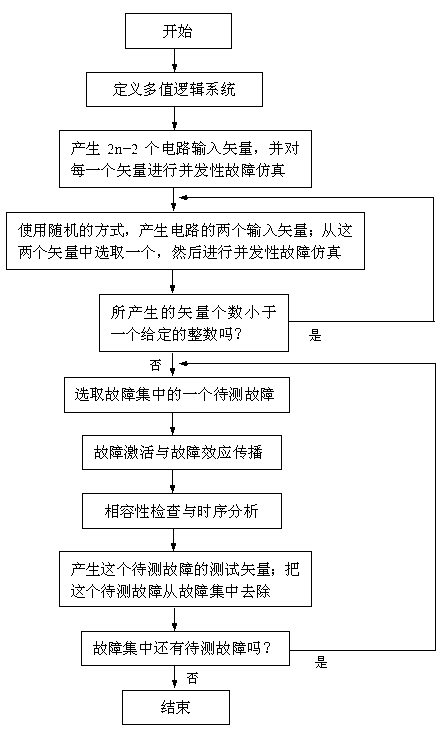

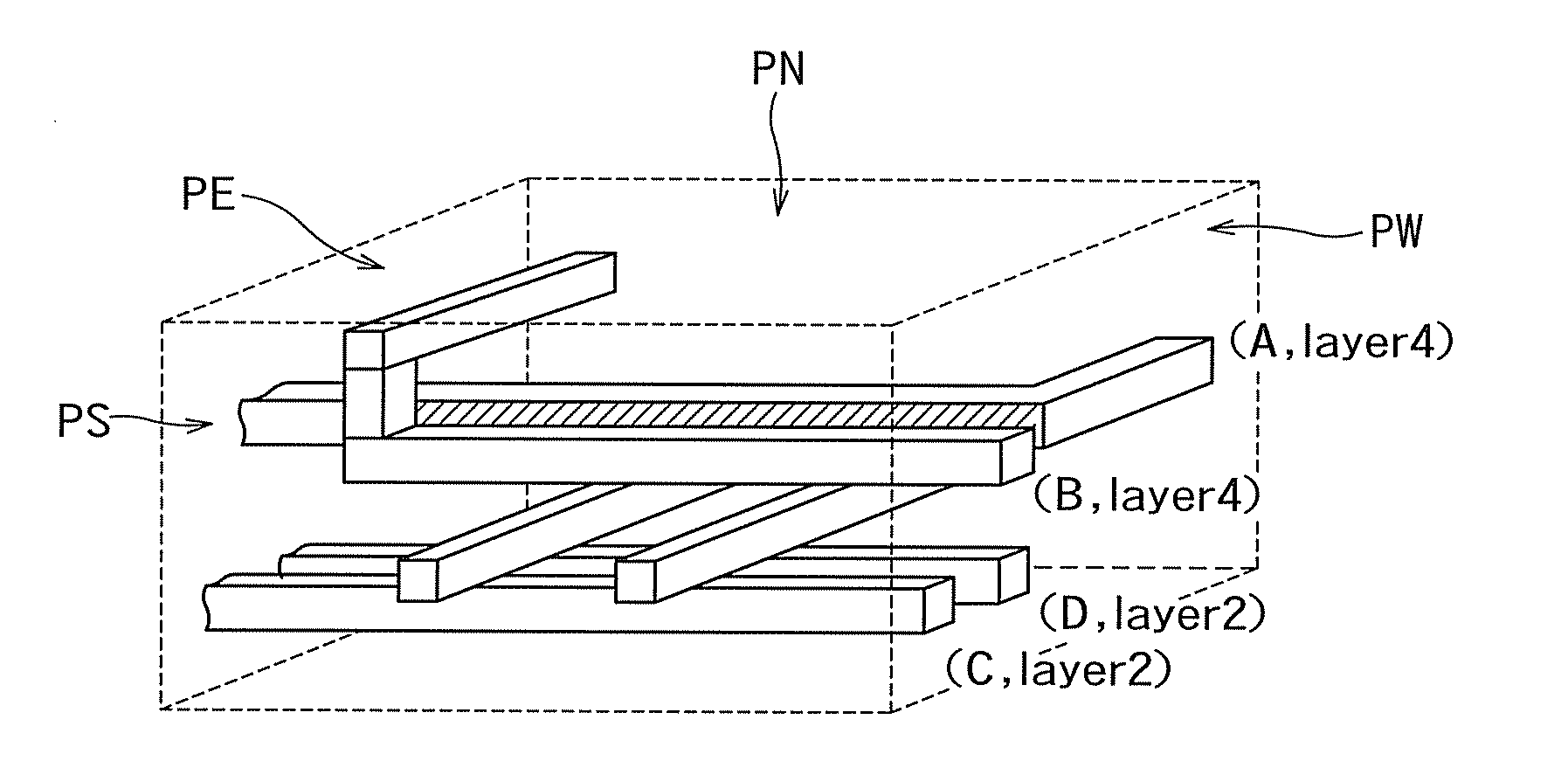

Fault list and test pattern generating apparatus and method, fault list generating and fault coverage calculating apparatus and method

The test pattern generating apparatus contains a module configured to generate short information indicative of a relationship between a logical value of an input signal of a cell and a voltage of an electrically shorted portion assumed at an output terminal of the cell; a module configured to calculate a logical threshold value of the input terminal of the cell so as to generate logical threshold value information; a module configured to extract a bridge fault information from layout information of an LSI; a module configured to generate a bridge fault list including a bridge fault type based on the bridge fault information, the short information, and the logical threshold value information; and a module configured to generate a test pattern which detects bridge faults in an adjacent signal wire pair and a bridge fault type.

Owner:KK TOSHIBA

Fault list and test pattern generating apparatus and method, fault list generating and fault coverage calculating apparatus and method

ActiveUS20070260408A1Resistance/reactance/impedenceElectronic circuit testingFault coverageElectricity

The test pattern generating apparatus comprises a module configured to generate short information indicative of a relationship between a logical value of an input signal of a cell and a voltage of an electrically shorted portion assumed at an output terminal of the cell; a module configured to calculate a logical threshold value of the input terminal of the cell so as to generate logical threshold value information; a module configured to extract a bridge fault information from layout information of an LSI; a module configured to generate a bridge fault list including a bridge fault type based on the bridge fault information, the short information, and the logical threshold value information; and a module configured to generate a test pattern which detects bridge faults in an adjacent signal wire pair and a bridge fault type.

Owner:KK TOSHIBA

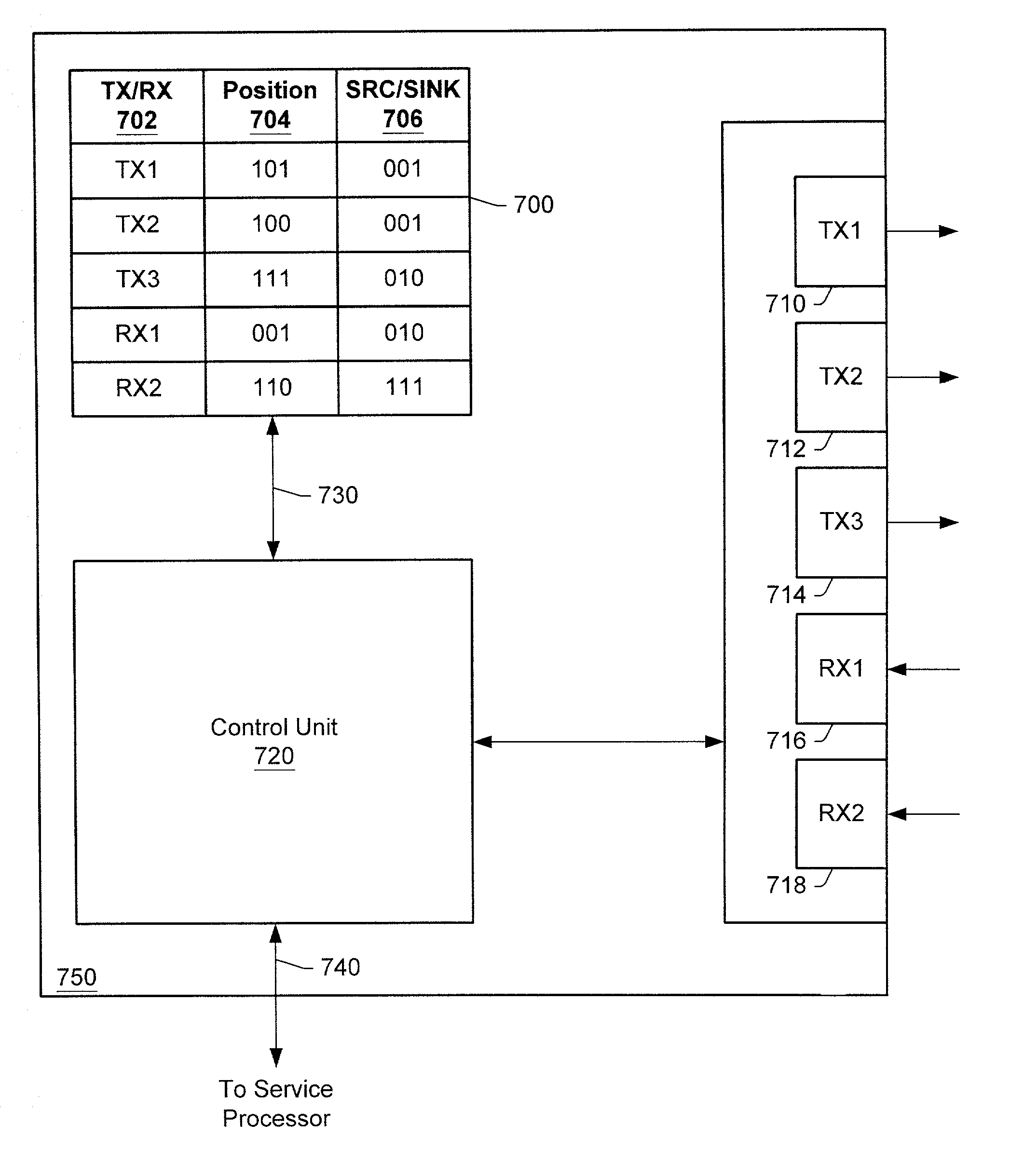

IBIST interconnect and bridge fault detection scheme

A method and mechanism for detecting interconnect and bridge defects. Contact points in a chip are assigned placement designation such that no two adjacent points have the same designation. A transmitter, receiver, and optional transmitter / receiver test are then run. During the transmitter test, transmitters with a given designation drive a particular test pattern while other transmitters drive a different test pattern. Receivers compare received test patterns against expected patterns. During a receiver test, transmitters drive a test pattern corresponding to the placement designation of the receivers to which they are coupled. During a particular receiver test, transmitters coupled to receivers of a given designation drive a particular stream, while other transmitters drive a different stream. Receivers then compare received streams against an expected stream. Finally, the placement designation of a transmitter or receiver of an adjacent transmitter / receiver pair may be temporarily assigned an alternate designation. A transmitter or receiver test is then run and receivers check received test patterns against expected patterns.

Owner:ORACLE INT CORP

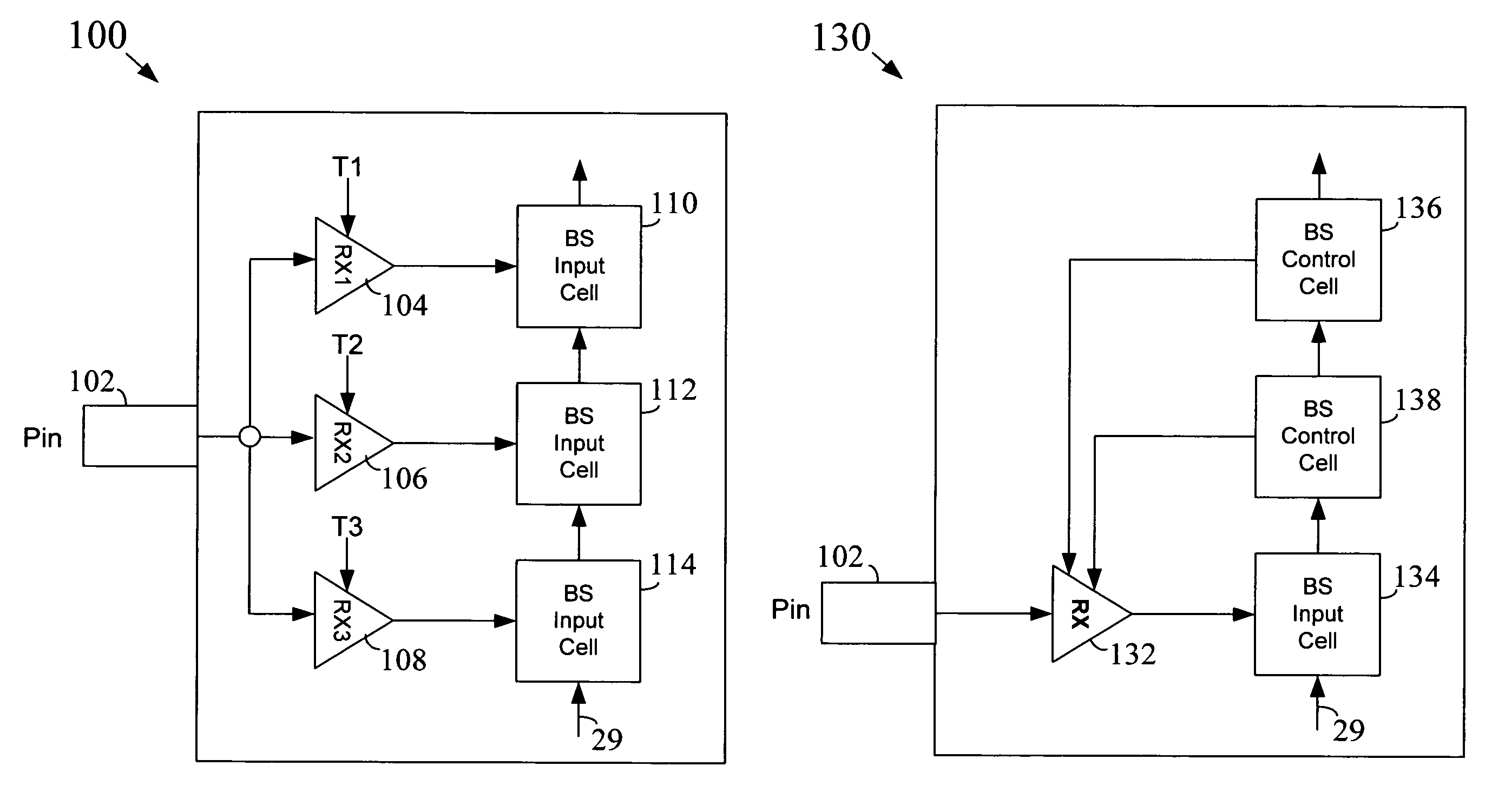

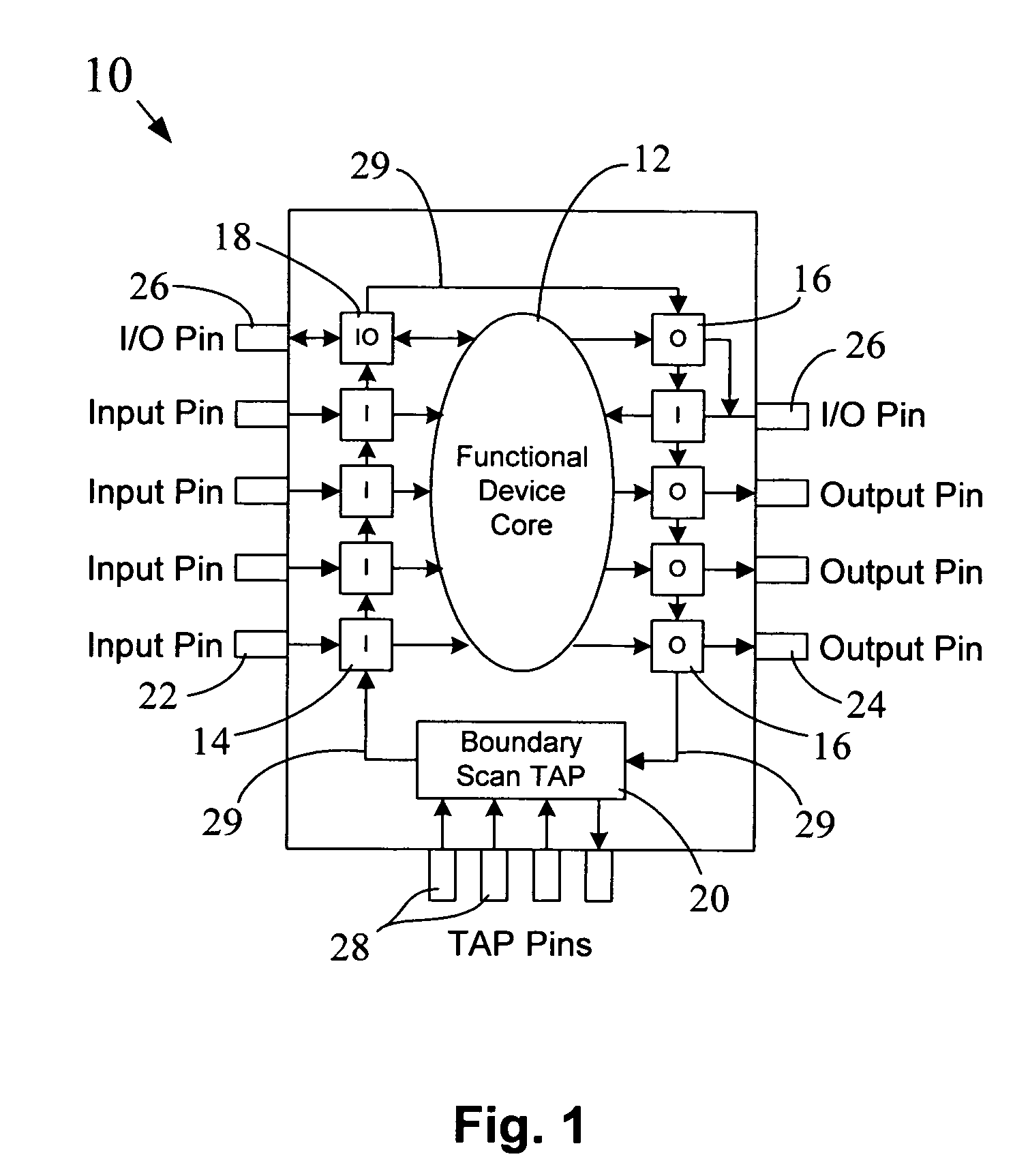

Apparatus for use in detecting circuit faults during boundary scan testing

A boundary scan compatible device includes functionality for use in diagnosing the presence of bridging faults within associated circuitry. In at least one embodiment, a boundary scan compatible device includes functionality for detecting an intermediate signal level on an electrical node of the device (e.g., a pin on a circuit package, etc.) that is indicative of a bridging fault. Various structures are provided that are capable of detecting an intermediate signal level.

Owner:CORELIS

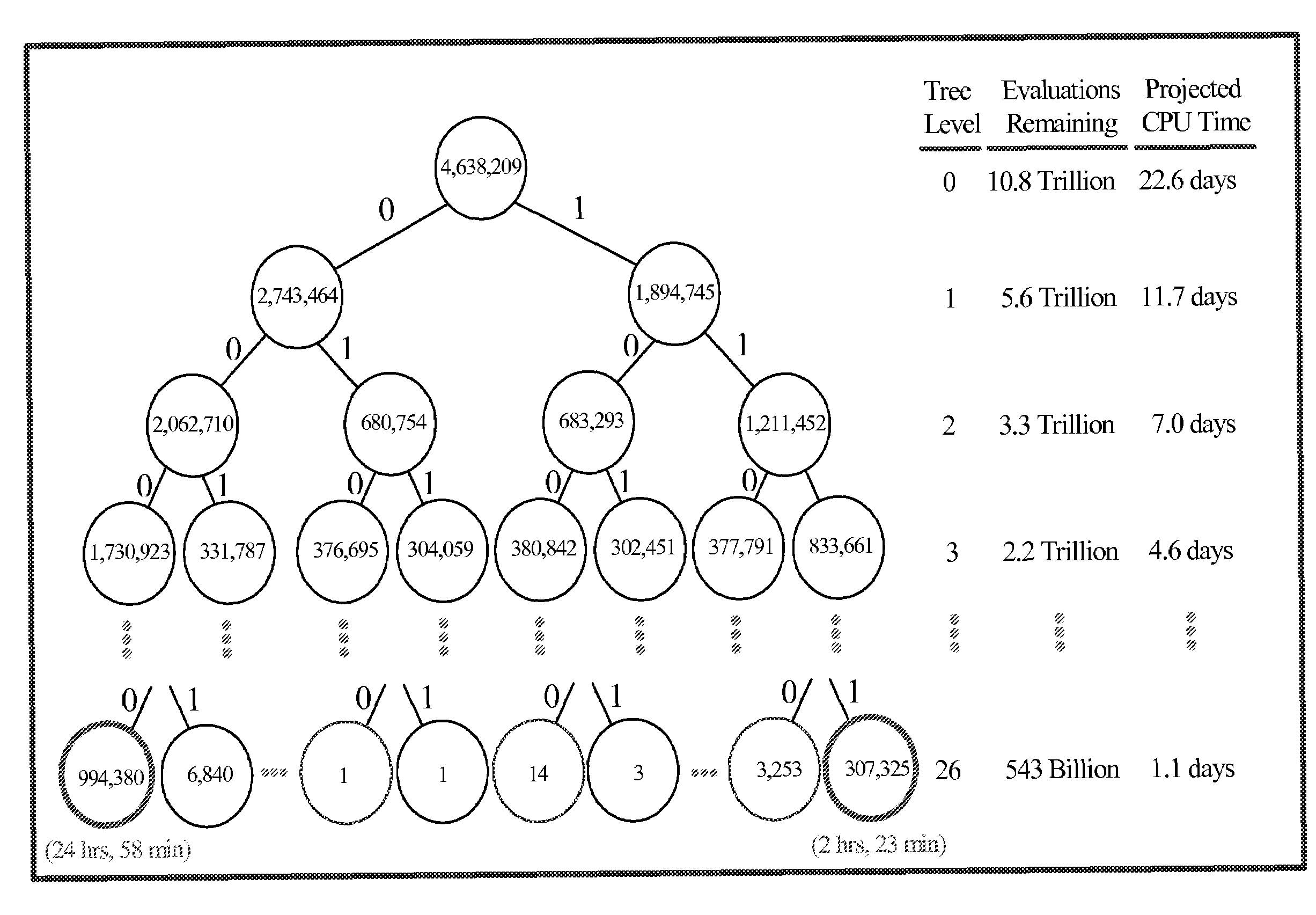

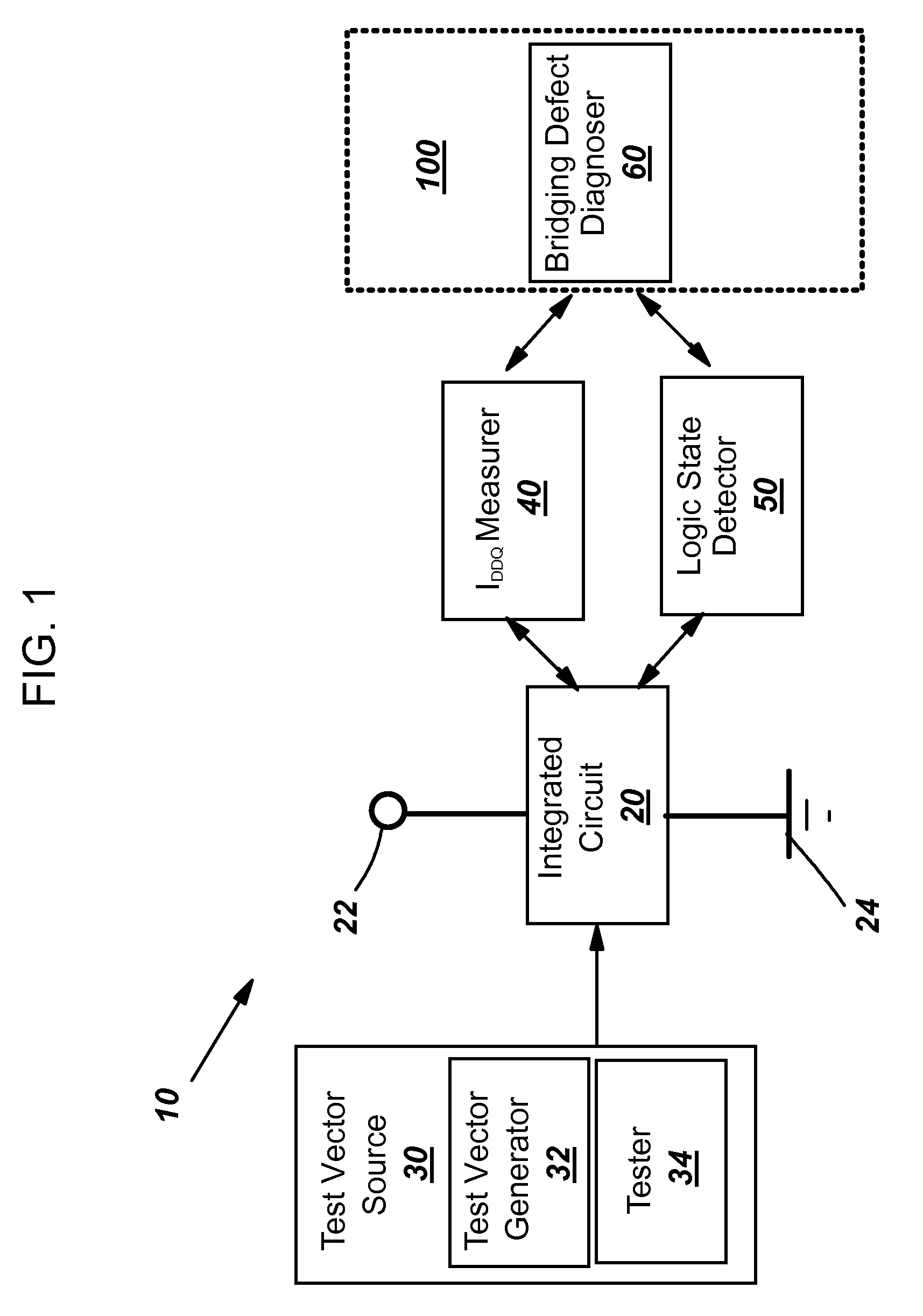

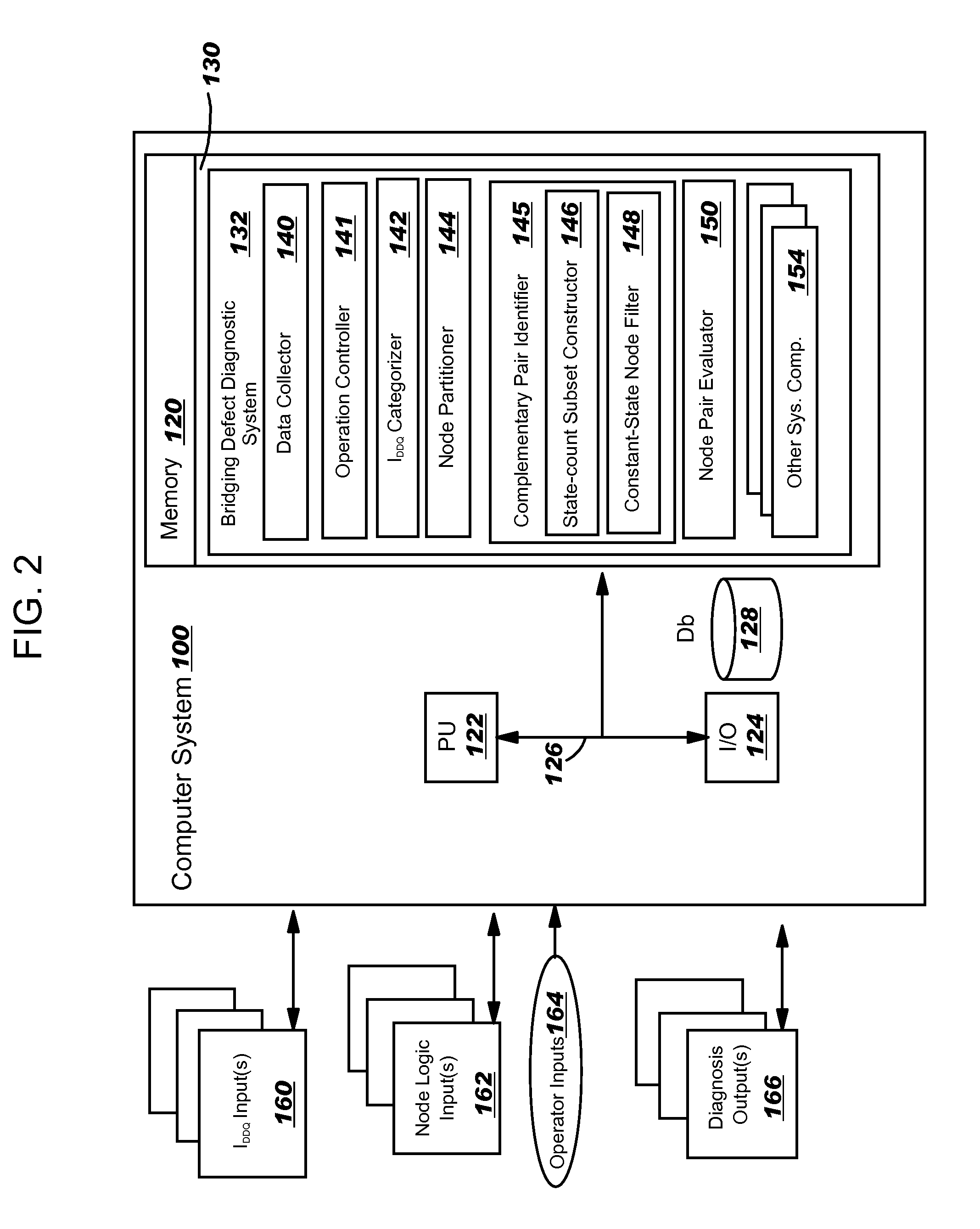

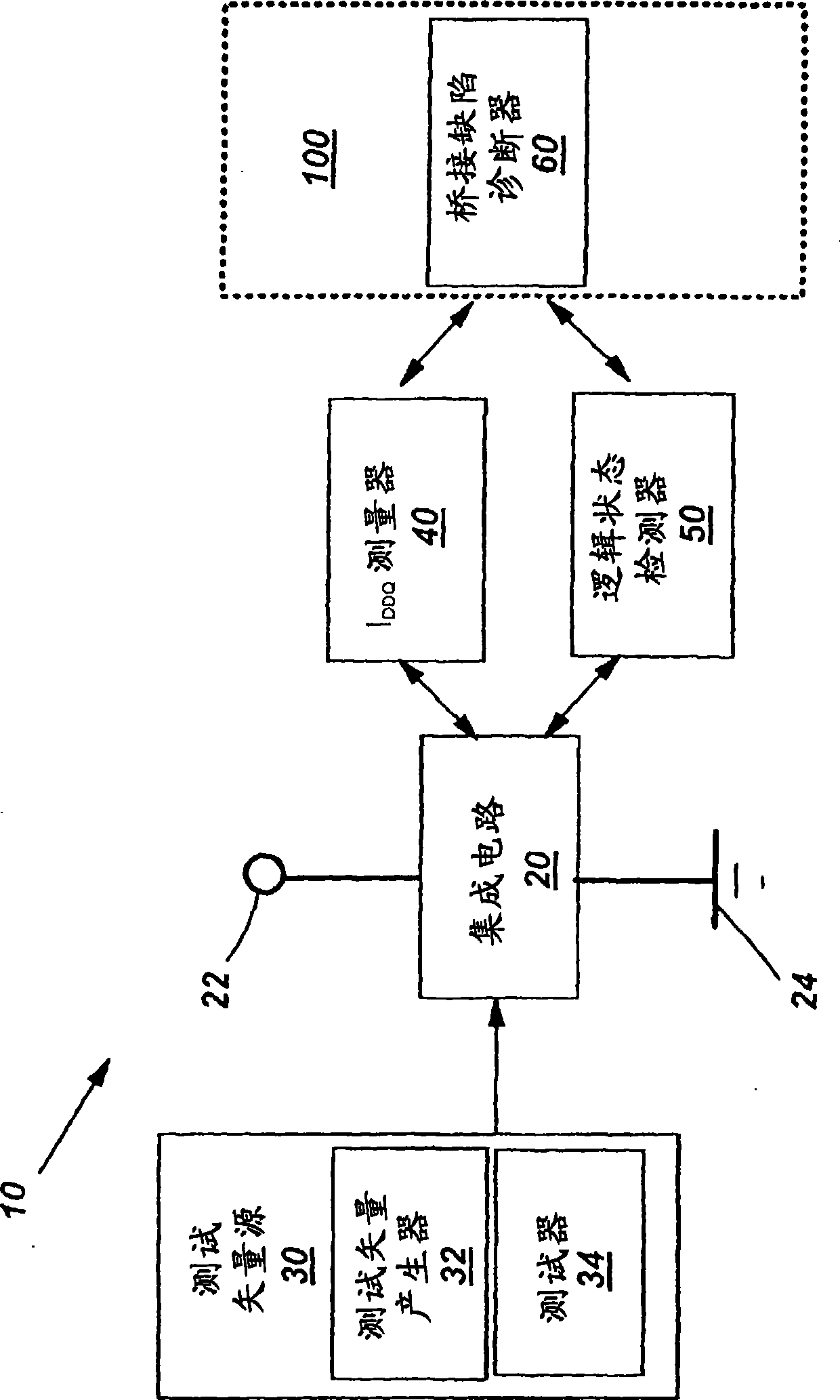

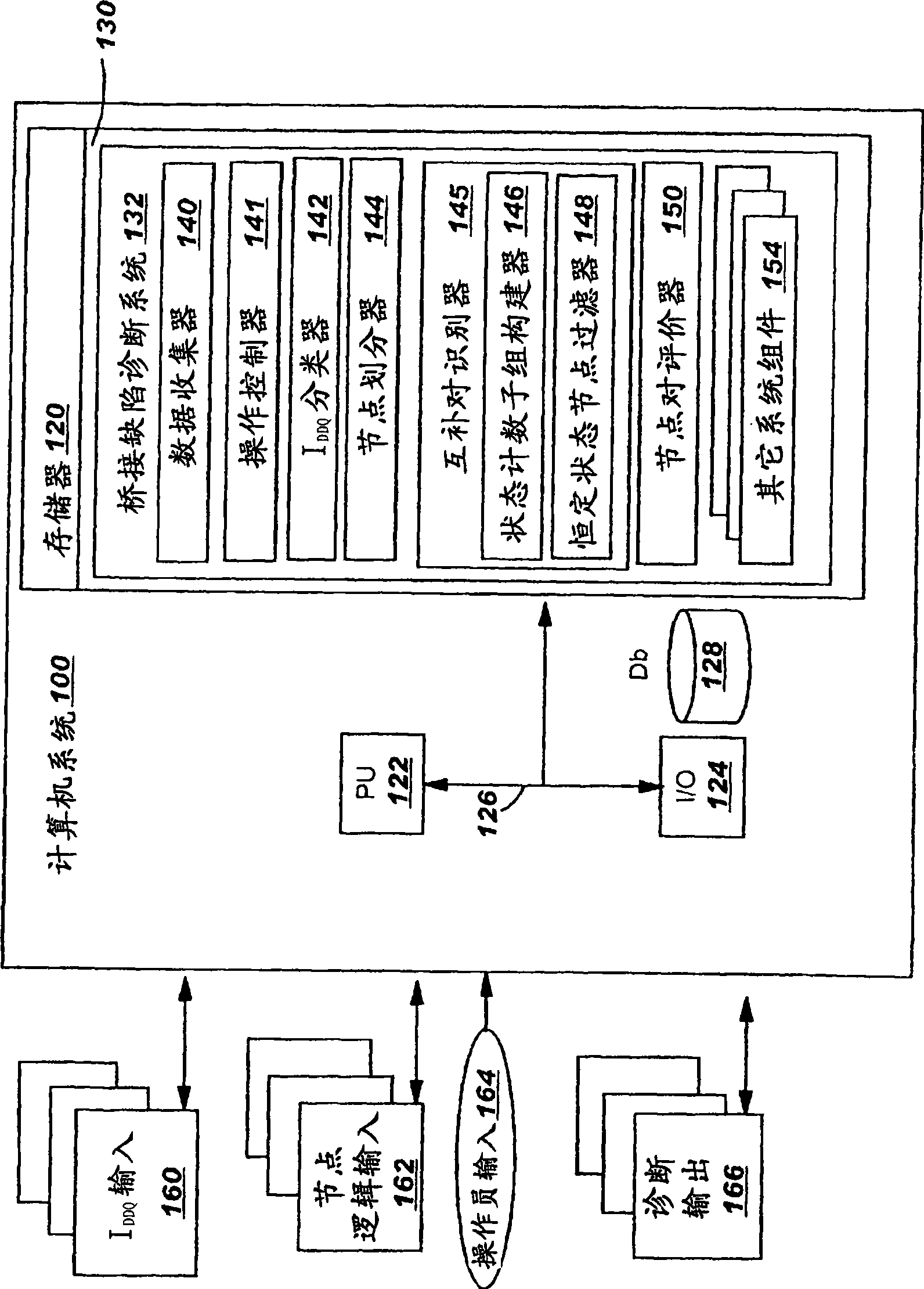

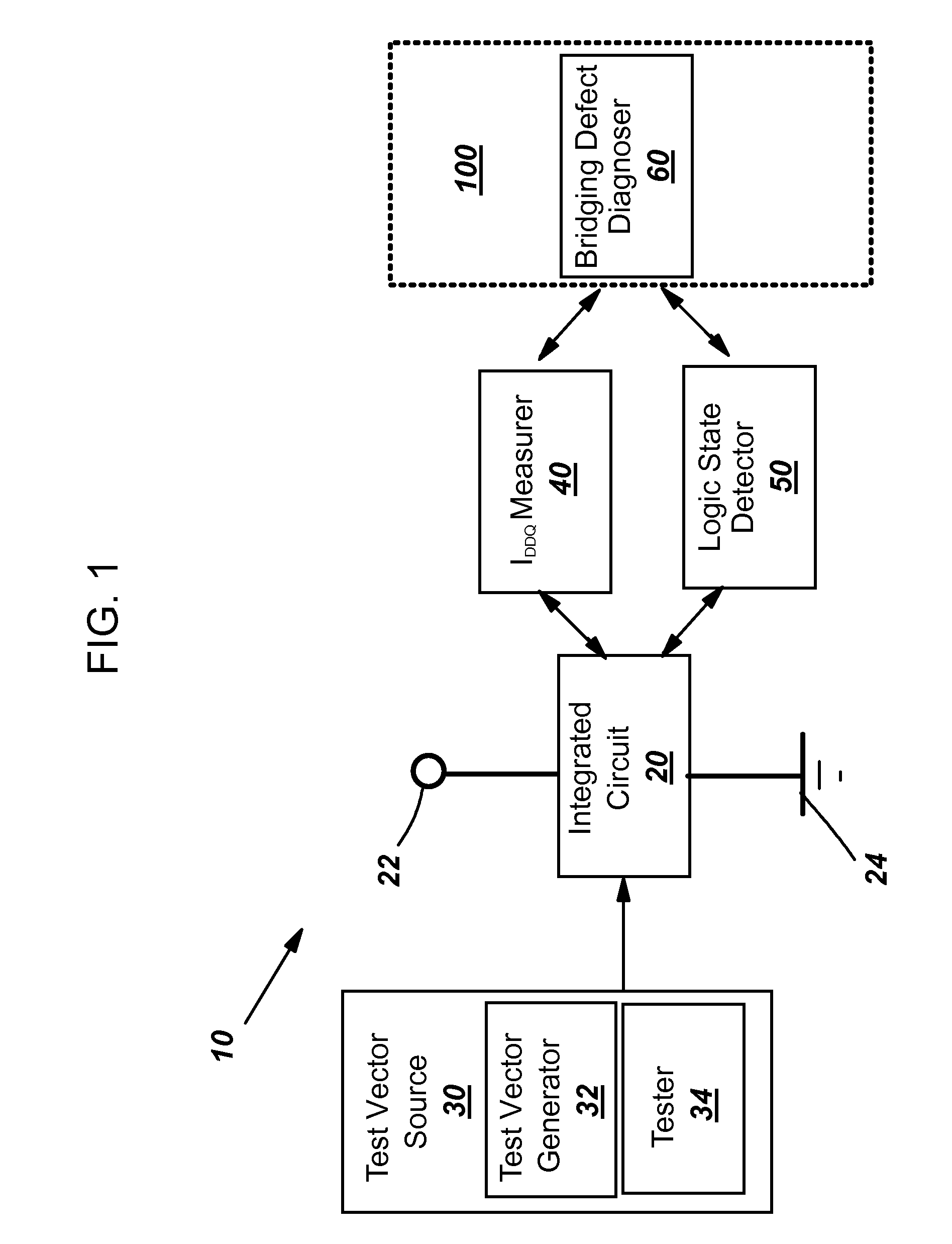

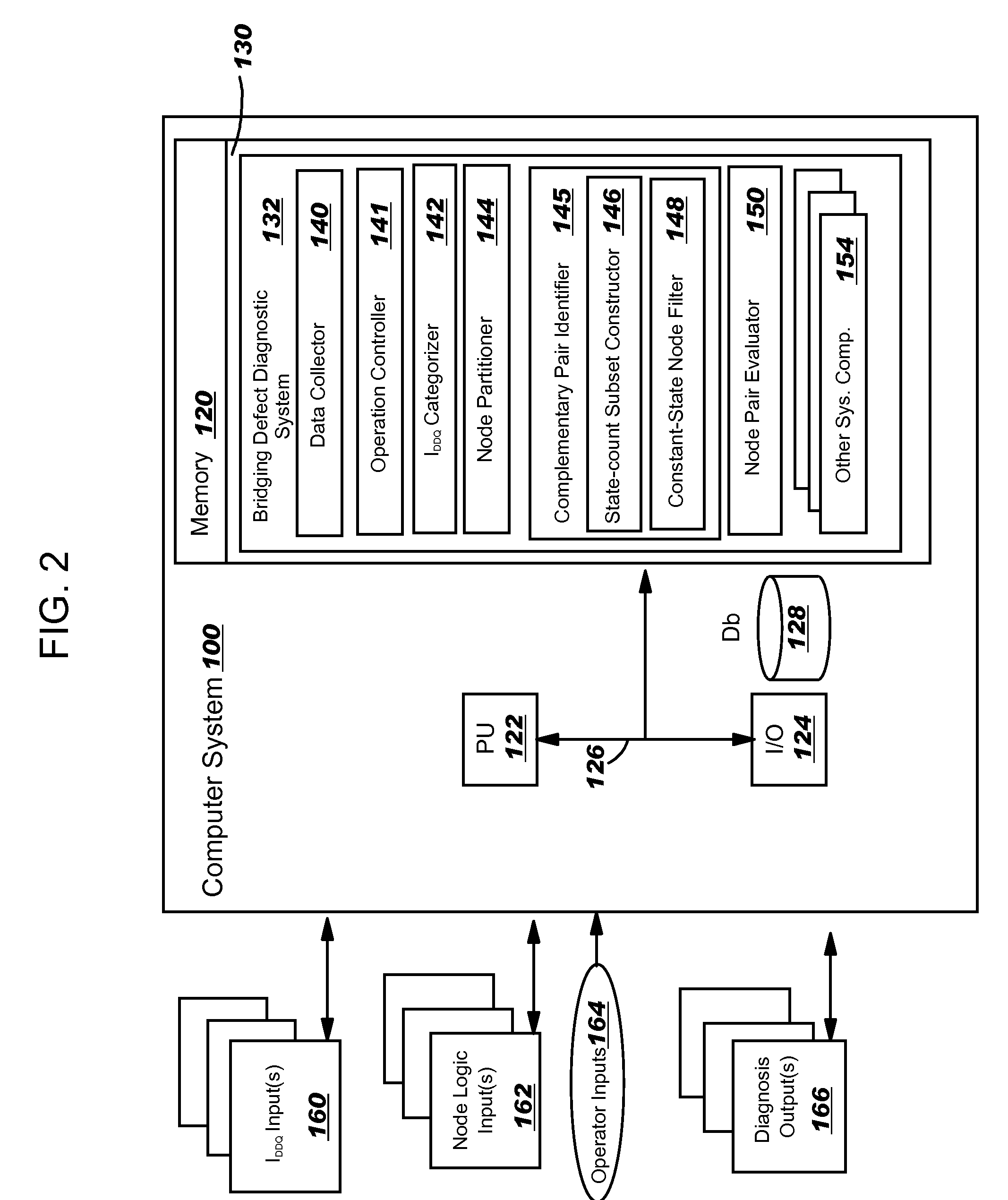

Exhaustive diagnosis of bridging defects in an integrated circuit including multiple nodes using test vectors and IDDQ measurements

InactiveUS7352170B2Software simulation/interpretation/emulationSpecial data processing applicationsTheoretical computer scienceIntegrated circuit layout

A method, system and computer program product for diagnosing a bridging defect in an integrated circuit including multiple nodes are disclosed. Quiescent power supply current (IDDQ) of the integrated circuit (IC) is measured under multiple test vectors. Logic states of the nodes on the IC are also obtained under the multiple test vectors. The nodes are partitioned into sets based on their logic states under low-current test vectors. Large sets are further divided into subsets (“state-count subsets”) based on the logic states of nodes under high-current test vectors. For large sets, explicit evaluation under the IDDQ bridge fault model is performed only on pairs of nodes belonging to subsets having complementary state counts, to save system resources in computation. Exhaustive diagnosis considering all pairs of nodes on the IC is thus feasibly achieved due to the saving of system resources.

Owner:GLOBALFOUNDRIES INC

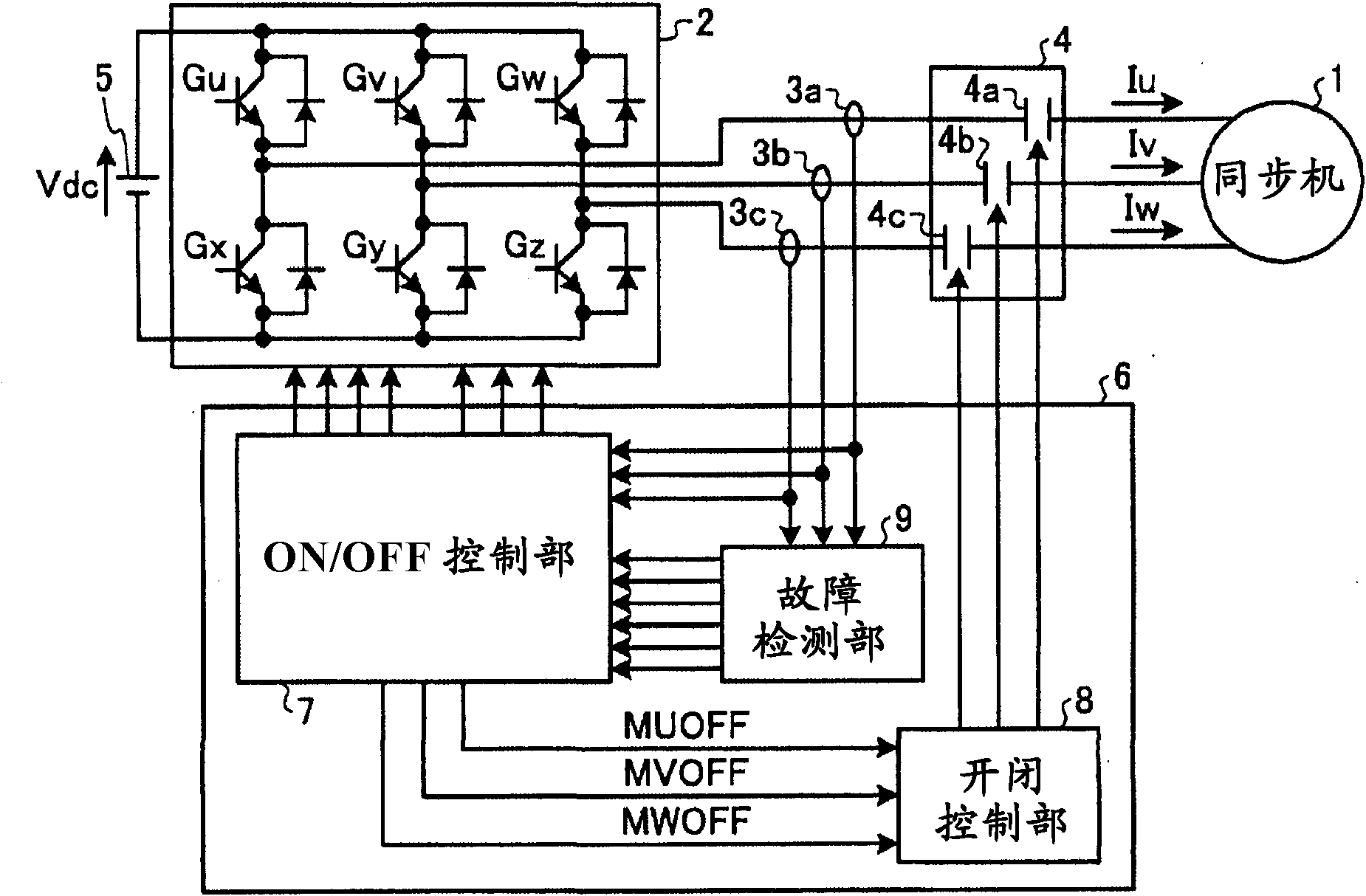

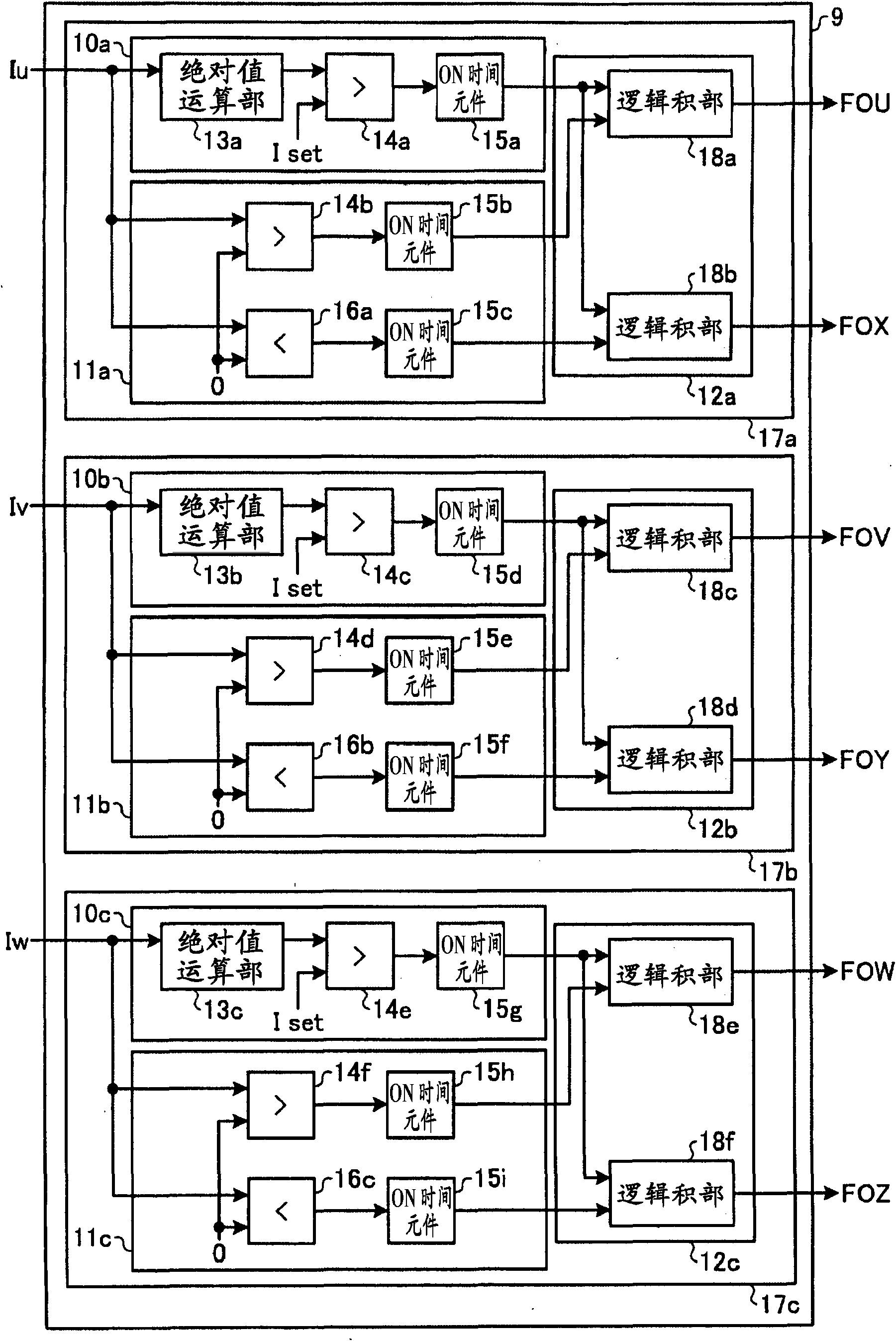

Power converting apparatus for an electric car

InactiveCN102577069AReduce the burden onSuppresses Transitional VoltageAC motor controlElectric motor controlEngineeringElectric cars

Disclosed is a power converting apparatus which is provided with a power converter (2) which has switching elements (Gu - Gz) and drives a synchronous machine (1), an opening / closing unit (4), current detectors (3a - 3c), and a control unit (6) which performs on / off control of the switching elements (Gu -Gz) and opening / closing control of the opening / closing unit (4) based on the currents detected by the current detectors (3a - 3c). The control unit (6) has a fault detection unit (9) which detects whether there is a bridging fault in any of the switching elements (Gu - Gz) and outputs a signal indicating the detection results; an ON / OFF control unit (7) which, when a first phase (e.g. the U phase) involves a bridging fault, sets one of the switching elements constituting another phase (the V phase or the W phase) to an on operating state, and also outputs a signal to open the opening / closing unit (4); and an opening / closing control unit (8) which, when a second phase (e.g. the W phase) has a switching element set to an on operating state by the ON / OFF control unit, for the third phase (e.g. the V phase) other than the first phase or the second phase, opens the V phase opening / closing unit (4b) which is connected to the third phase.

Owner:MITSUBISHI ELECTRIC CORP

Exhaustive diagnosis of bridging defects in an integrated circuit

InactiveCN101460951ASpecial data processing applicationsMarginal circuit testingTheoretical computer scienceLogic state

A method, system and computer program product for diagnosing a bridging defect in an integrated circuit including multiple nodes (20) are disclosed. Quiescent power supply current (IDDQ) of the integrated circuit (IC) is measured (40) under multiple test vectors (30). Logic states of the nodes on the IC are also obtained (20) under the multiple test vectors (30). The nodes are partitioned (S3) into sets based on their logic states under low-current test vectors. Large sets are further divided into subsets ('state-count subsets') (S 5-1) based on the logic states of nodes under high-current test vectors. For large sets, explicit evaluation under the IDDQ bridge fault model is performed only on pairs of nodes belonging to subsets having complementary state counts (S5-2, S5-3), to save system resources in computation. Exhaustive diagnosis considering all pairs of nodes on the IC is thus feasibly achieved due to the saving of system resources.

Owner:GLOBALFOUNDRIES INC

Exhaustive diagnosis of bridging defects in an integrated circuit

InactiveUS20070296443A1Save system resourcesSoftware simulation/interpretation/emulationSpecial data processing applicationsNODALTheoretical computer science

A method, system and computer program product for diagnosing a bridging defect in an integrated circuit including multiple nodes are disclosed. Quiescent power supply current (IDDQ) of the integrated circuit (IC) is measured under multiple test vectors. Logic states of the nodes on the IC are also obtained under the multiple test vectors. The nodes are partitioned into sets based on their logic states under low-current test vectors. Large sets are further divided into subsets (“state-count subsets”) based on the logic states of nodes under high-current test vectors. For large sets, explicit evaluation under the IDDQ bridge fault model is performed only on pairs of nodes belonging to subsets having complementary state counts, to save system resources in computation. Exhaustive diagnosis considering all pairs of nodes on the IC is thus feasibly achieved due to the saving of system resources.

Owner:GLOBALFOUNDRIES INC

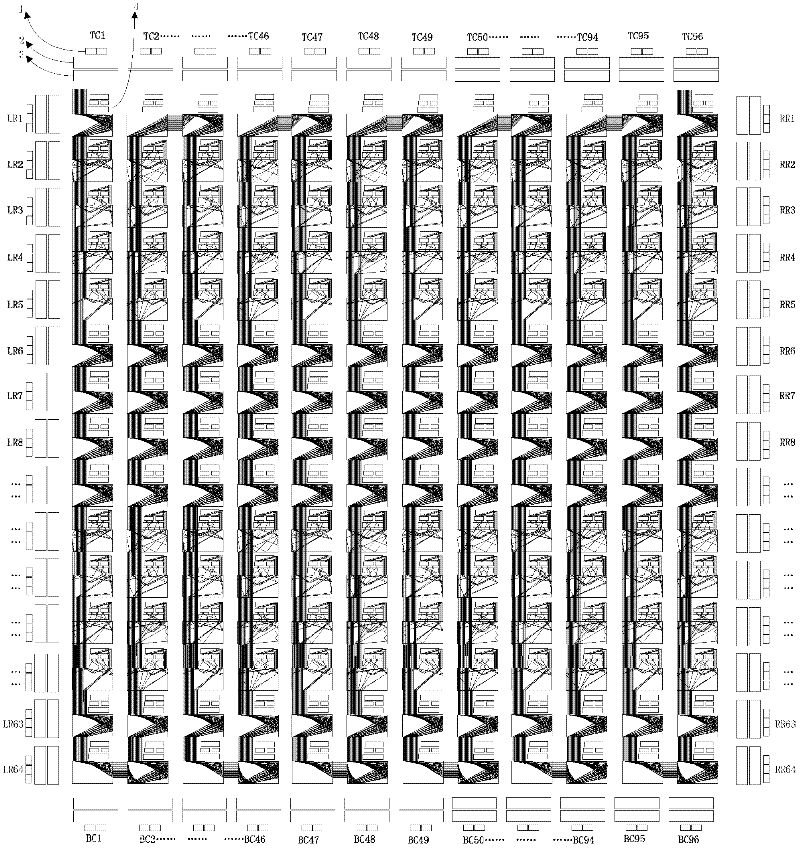

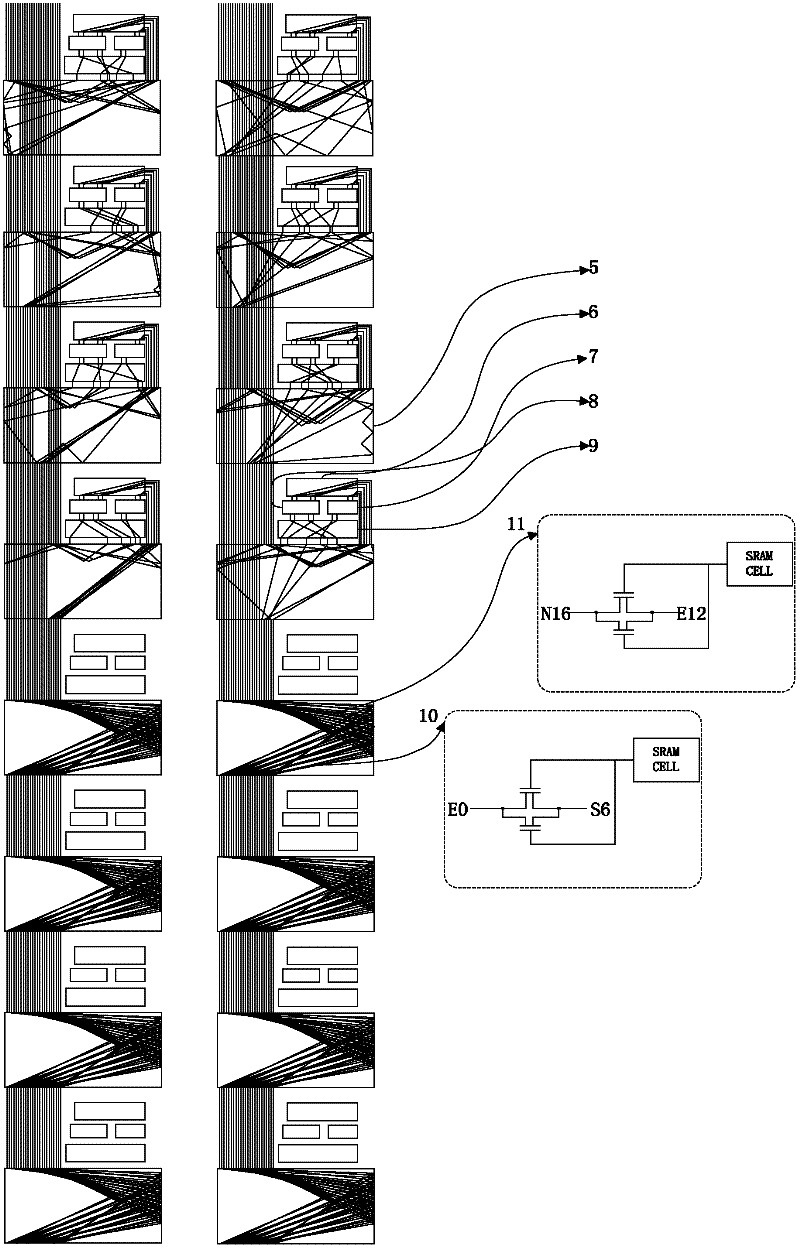

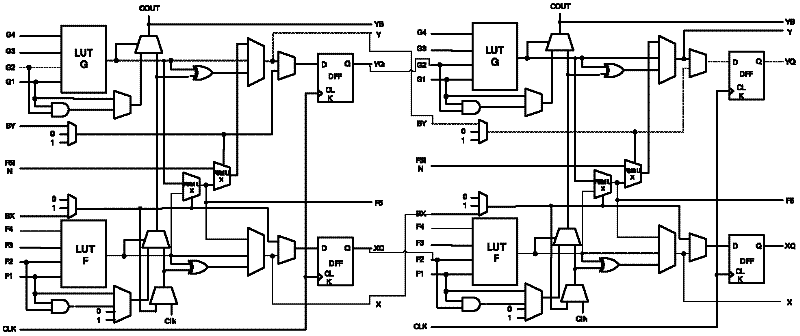

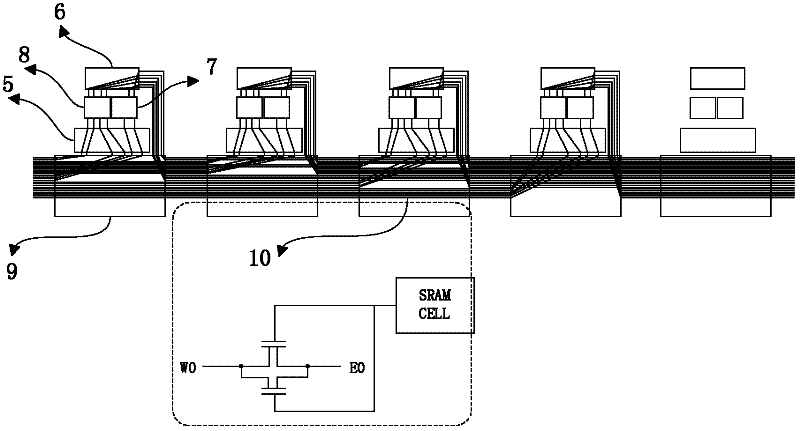

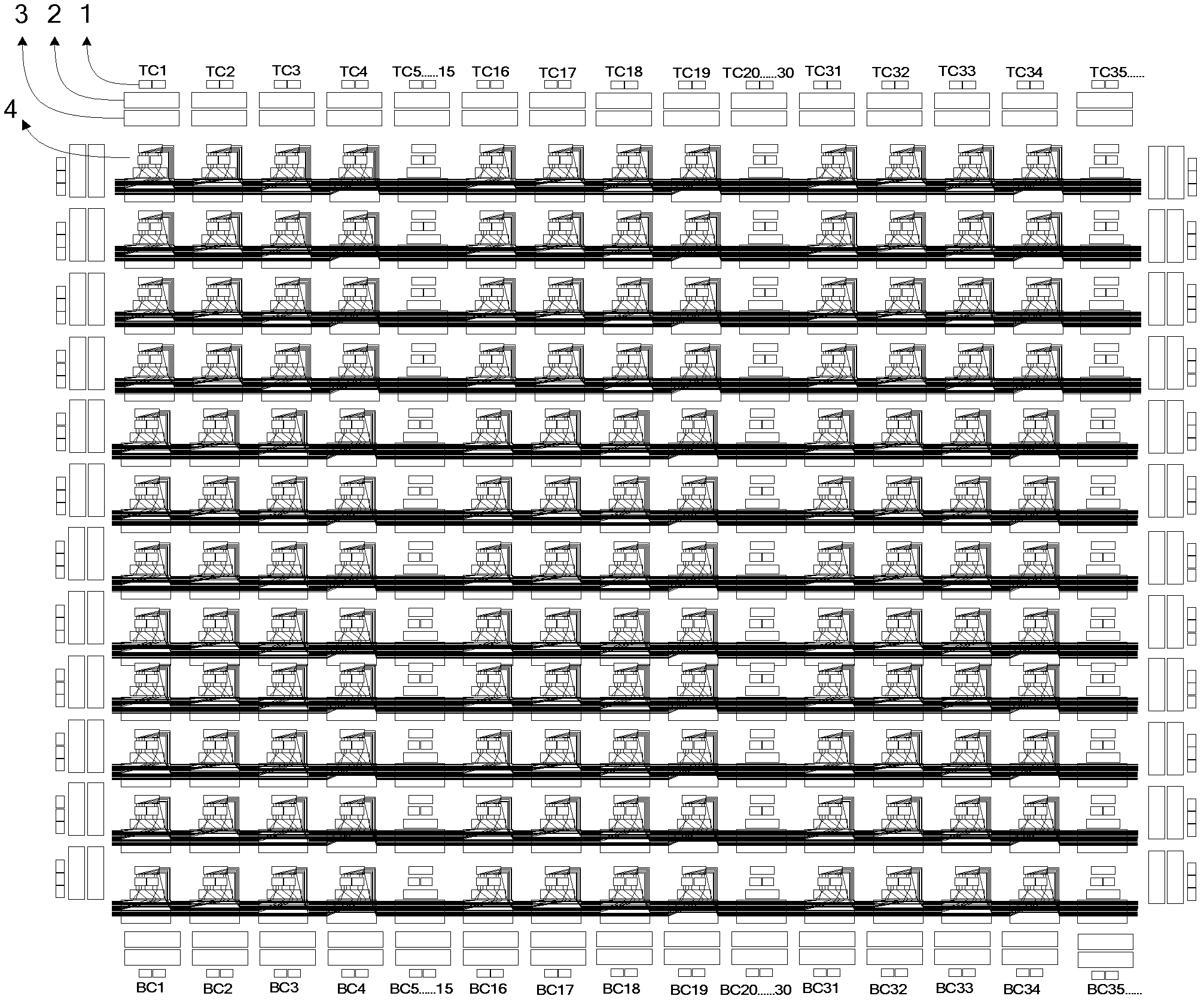

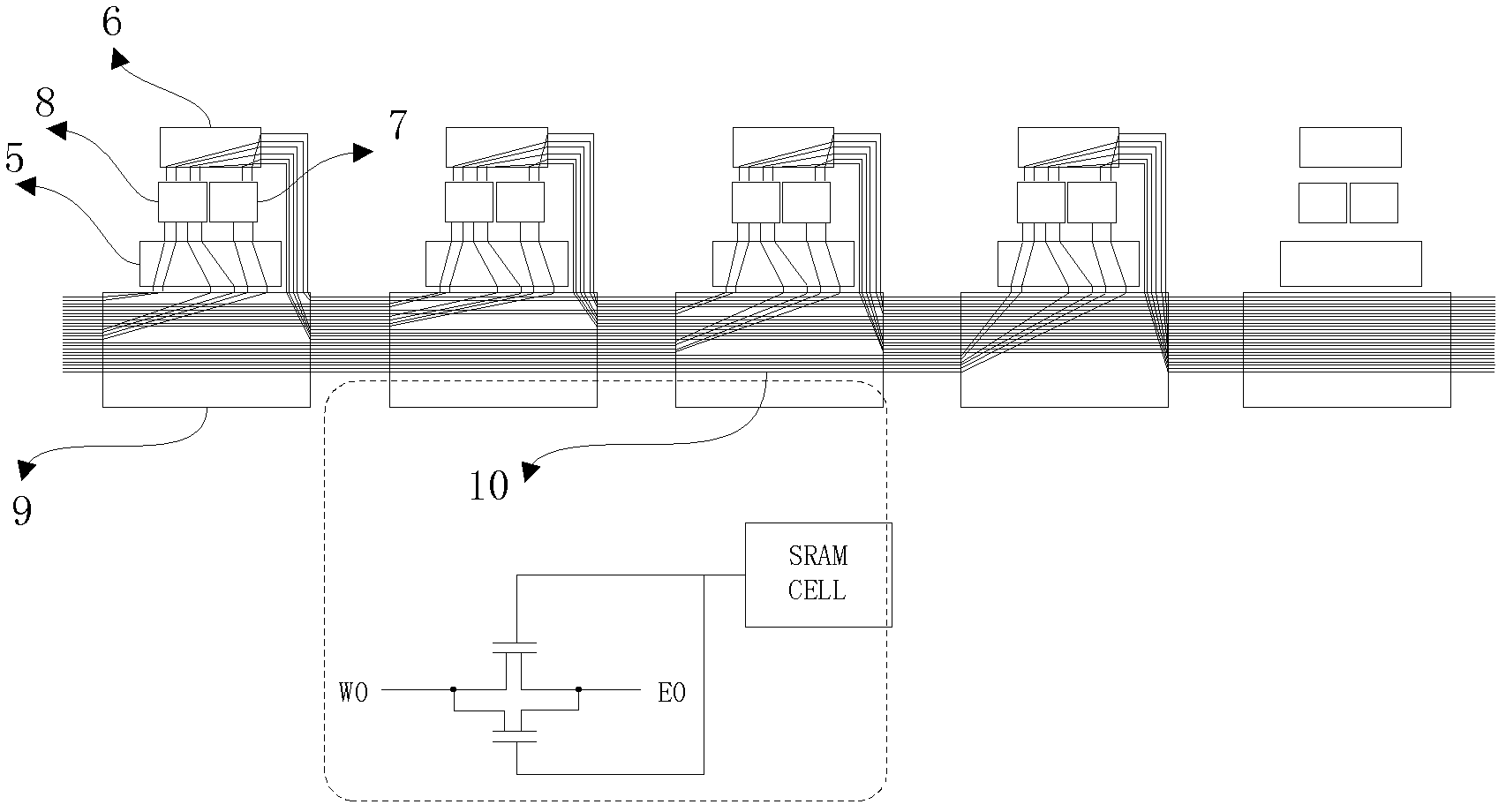

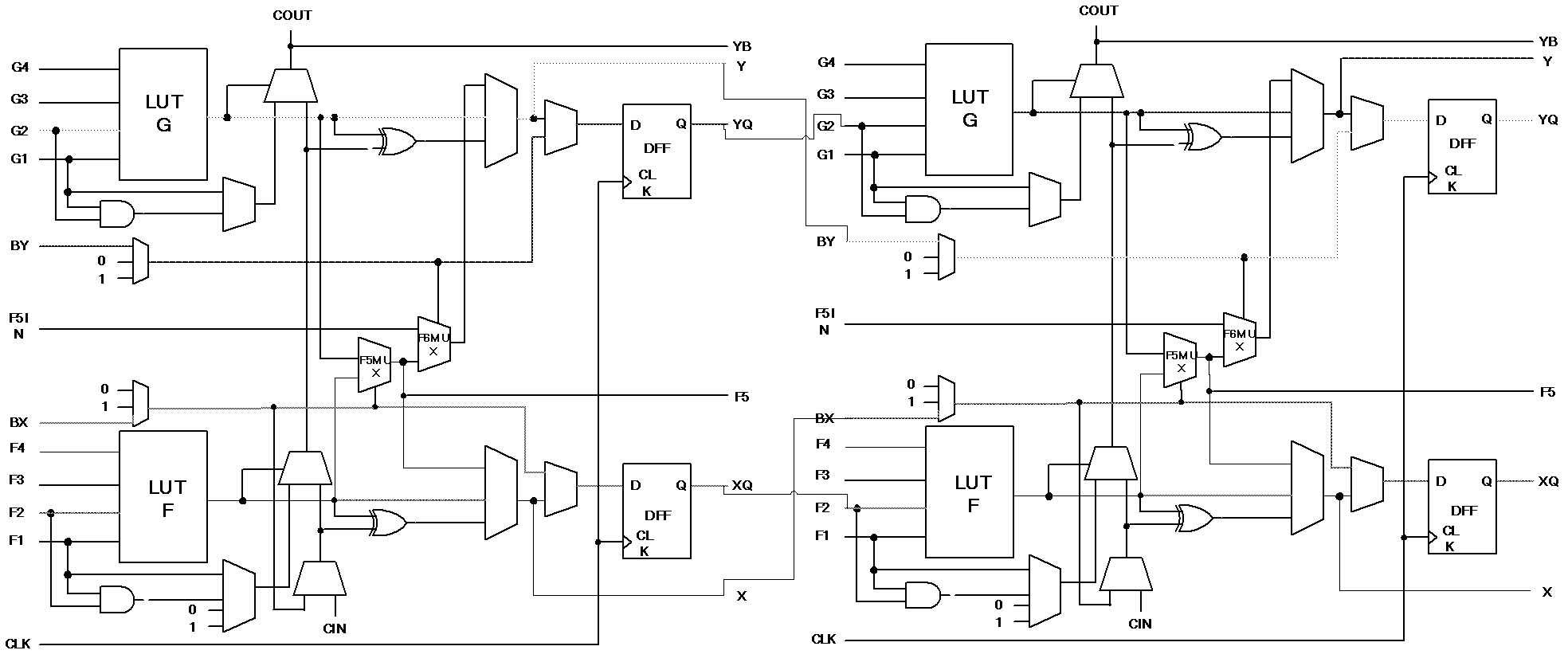

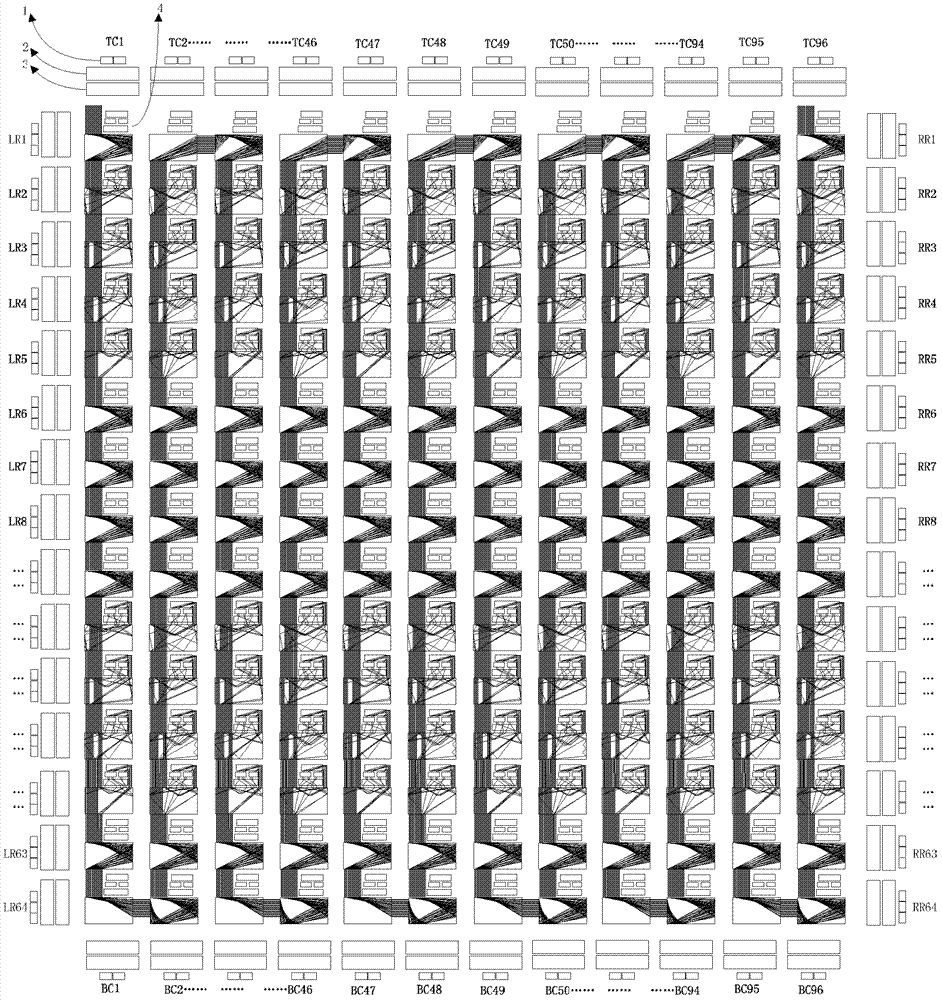

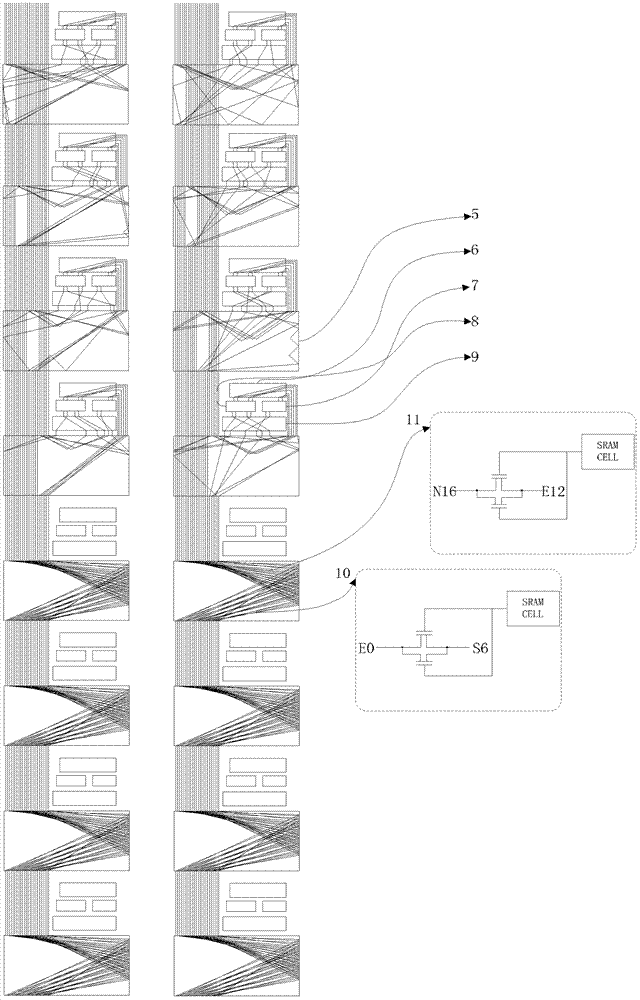

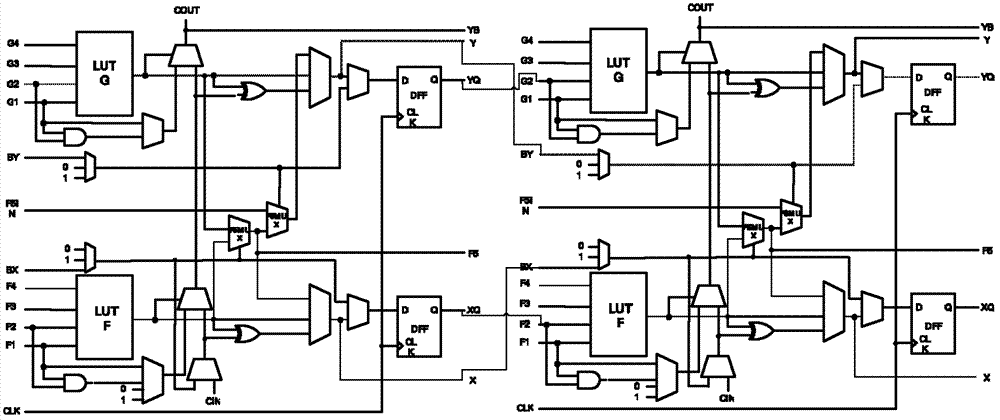

Method for testing field programmable gate array (FPGA) single-long line slant switches

ActiveCN102253329AEasy to operateThe testing process is simpleCircuit interrupters testingShift registerTest flow

The invention relates to a method for testing Virtex architecture-based field programmable gate array (FPGA) single-long line slant switches. The Virtex architecture-based FPGA single-long line slant switches are tested only by four-time configuration. The method has the advantages that: the single-long line slant switches of a FPGA circuit are tested in a shifting register chain mode, so that bridging failure between signals of any two single-long lines in the 24 single-long lines which are used as one group can be tested; the single-long line slant switches of all configurable logic blocks can be tested only by using four sections of configuration codes; a test process is simplified by the initial configuration of Blockram, so the method is convenient to operate by users; the failure positioning is accurate and is subjected to the four-time configuration, and can be corrected to the single-long line slant switches of the four CLBs under the condition that the position deviation of the CLBs in the latter two-time configuration is 4; and a basic structure which takes a row as a snakelike channel is changed into a basic structure which takes a line as the snakelike channel under the condition that the requirement of the failure positioning is extreme accurate, so the failure positioning can be corrected to the specific single-long line slant switches which are determined uniquely and correspond to the CLBs by eight-time configuration.

Owner:WUXI ESIONTECH CO LTD

Apparatus for creating test pattern and calculating fault coverage or the like and method for creating test pattern and calculating fault coverage or the like

InactiveUS7966138B2Electronic circuit testingSpecial data processing applicationsElectrical resistance and conductanceFault coverage

The method for creating a test pattern and calculating a fault coverage or the like of the present invention is characterized by creating bridging fault voltage information indicating a voltage of a bridging assumed on the wire derived from an output terminal of a cell, calculating a logical threshold of an input terminal of the cell, extracting bridging fault information on an adjacent wire pair, calculating a detection limit resistance value using the logical threshold, adding the detection limit resistance value to bridging fault voltage information, creating extended bridging fault voltage information, creating a bridging fault list including a bridging fault type based on the extended bridging fault voltage information, creating a test pattern based on the bridging fault list, judging whether or not a bridging fault can be detected through this test pattern, creating fault detection information and calculating a weighted fault coverage based on the fault detection information and bridging fault generation information.

Owner:KK TOSHIBA

A kind of fpga single long line and the test method of the direct connection switch

ActiveCN102288870AEasy to operateThe testing process is simpleFault locationCircuit interrupters testingShift registerTest flow

The invention relates to a testing method for FPGA (field programmable gate array) single long wires and directly connected switches based on a Virtex structure, which comprises four configuration steps. The invention has the advantages that: the shift register chain mode is adopted to test 24 single long wires of an FPGA circuit, and bridging faults between signals of any two of the 24 wires in one group can be tested; the single long wires and directly connected switches of all CLBs (configurable logic blocks) can be tested only with four configuration codes; the testing process is simplified and the user operation is facilitated through initial configuration of the Blockram; the faults can be accurately positioned, four configuration steps are included, and when the deviation of the CLB positions in the last two configuration step is 4, the faults can be accurately positioned for the directly connected switches or single long wires of four CLBs; and when the fault positioning requirements are extremely accurate, the deviation of the CLB positions can be defined as 1, two configuration steps in total are adopted, and the fault can be accurately positioned for the directly connected switch or single long wire corresponding to one specific and unique CLB.

Owner:WUXI ESIONTECH CO LTD

Apparatus for creating test pattern and calculating fault coverage or the like and method for creating test pattern and calculating fault coverage or the like

InactiveUS20080262761A1Electronic circuit testingSpecial data processing applicationsFault coverageBridging fault

The method for creating a test pattern and calculating a fault coverage or the like of the present invention is characterized by creating bridging fault voltage information indicating a voltage of a bridging assumed on the wire derived from an output terminal of a cell, calculating a logical threshold of an input terminal of the cell, extracting bridging fault information on an adjacent wire pair, calculating a detection limit resistance value using the logical threshold, adding the detection limit resistance value to bridging fault voltage information, creating extended bridging fault voltage information, creating a bridging fault list including a bridging fault type based on the extended bridging fault voltage information, creating a test pattern based on the bridging fault list, judging whether or not a bridging fault can be detected through this test pattern, creating fault detection information and calculating a weighted fault coverage based on the fault detection information and bridging fault generation information.

Owner:KK TOSHIBA

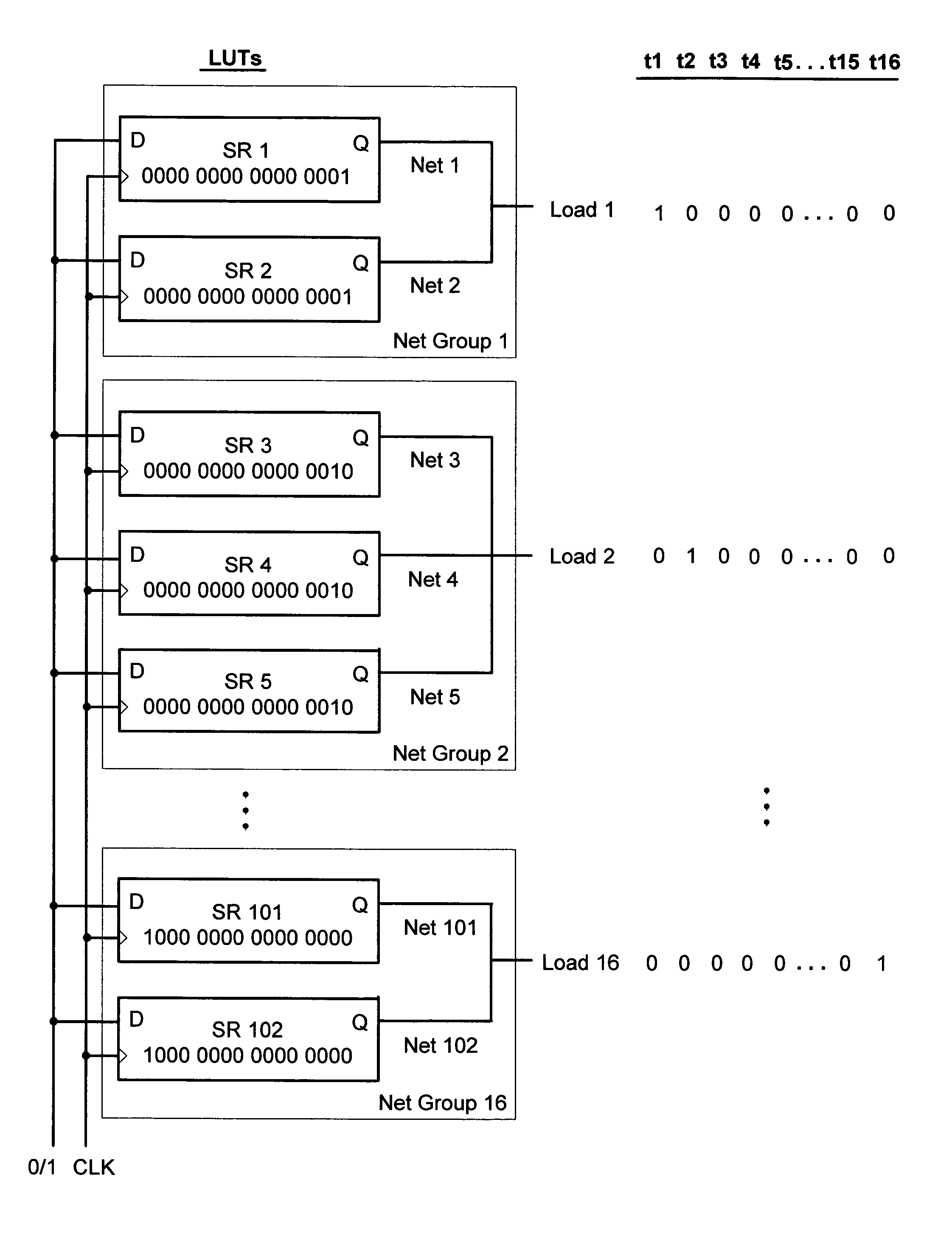

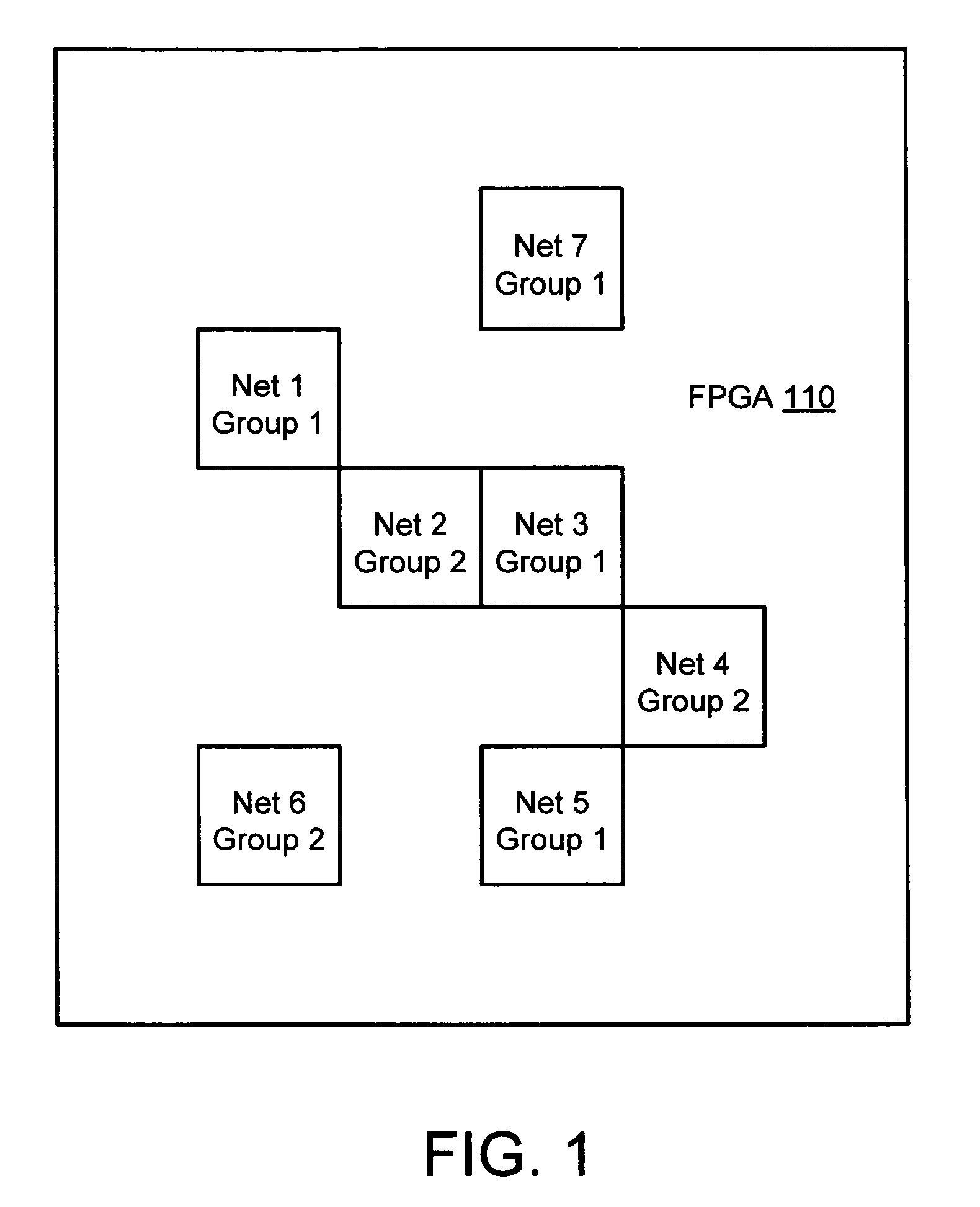

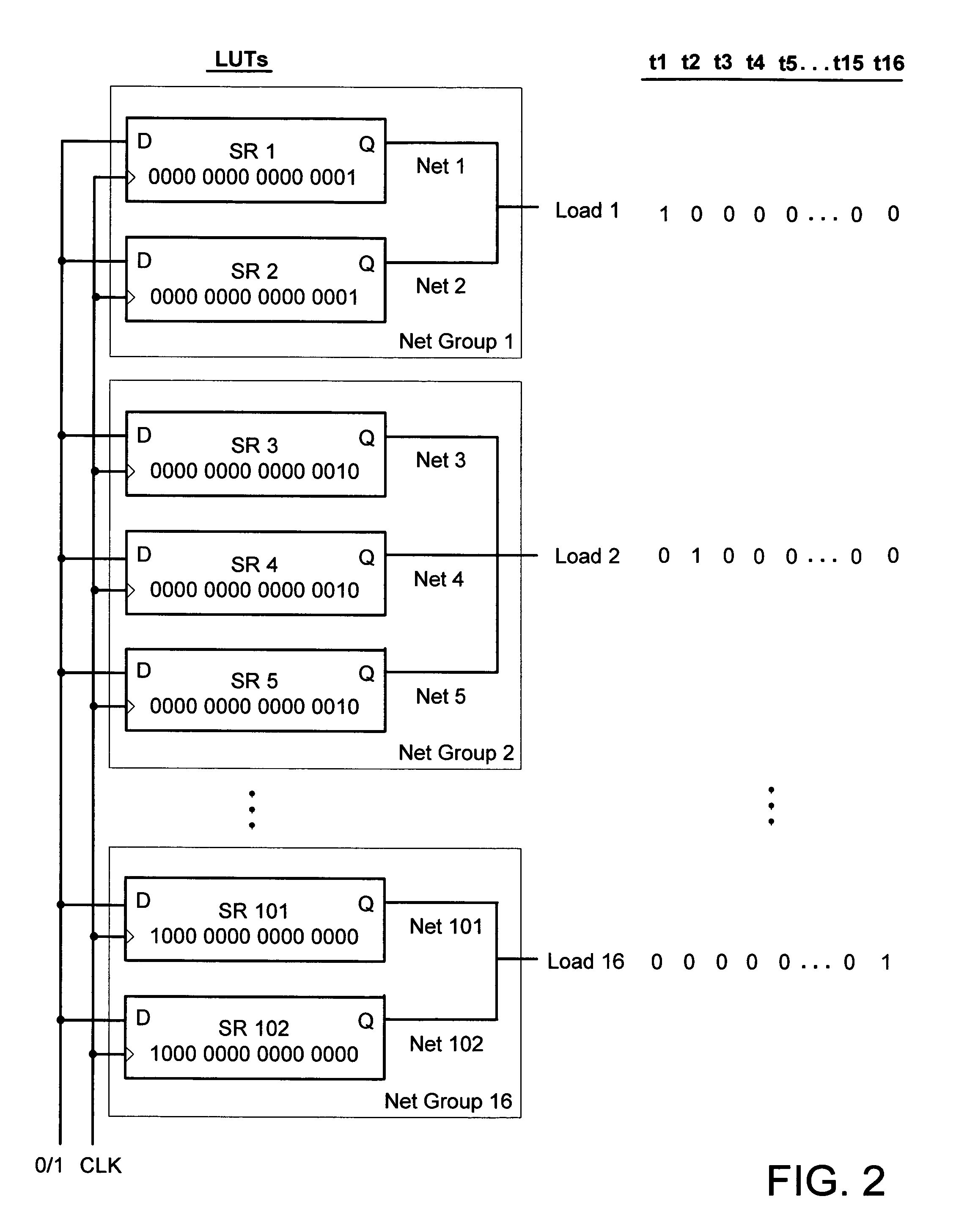

Testing for bridge faults in the interconnect of programmable integrated circuits

InactiveUS7614022B1Detecting faulty computer hardwareElectrical testingShift registerIntegrated circuit interconnect

Apparatus and methods of testing for bridge faults in nets of the interconnect of a programmable integrated circuit. Each net is sourced by a function generator (e.g., a look up table) configured as a clocked shift register. For each net group, shift registers connecting nets in the group are initialized identically to one value and are initialized to a different unique value from shift registers connecting nets of other net groups. Each shift register stores one bit with a value one and zeros in all other bits. When the shift register is clocked, it provides a single one on one clock cycle and provides zeros in all other clock cycles. At the end of n clock cycles, where n is the length of the shift register, if the load on any net has a value that is different from the value provided by the net's corresponding shift register, a short is detected.

Owner:XILINX INC

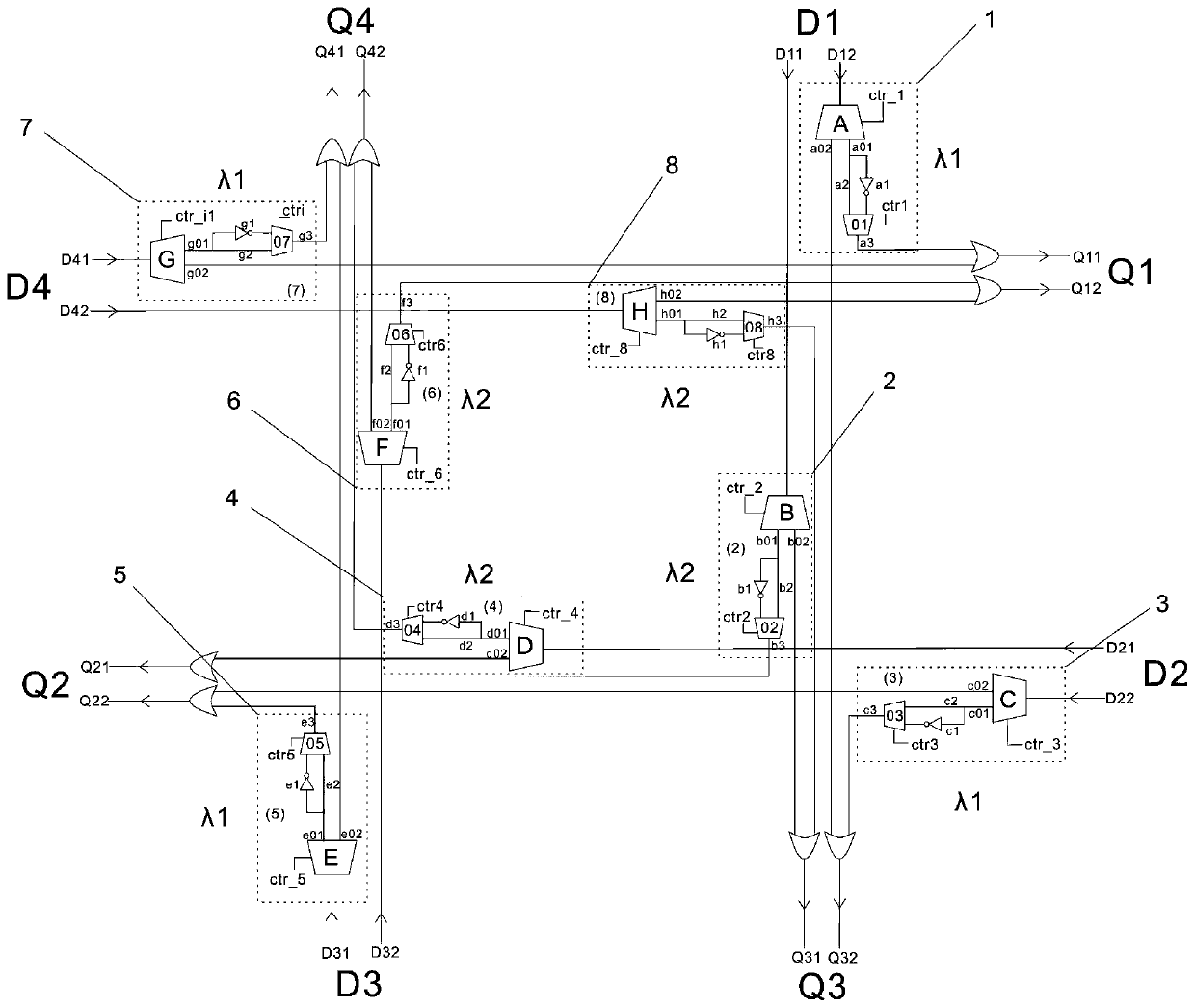

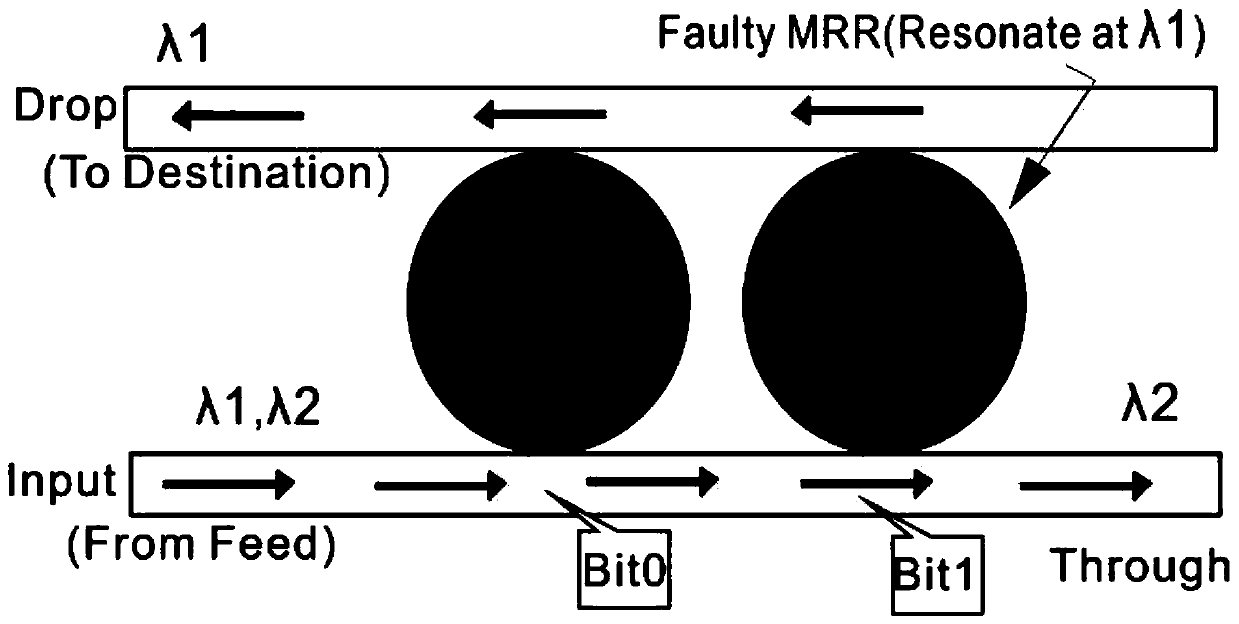

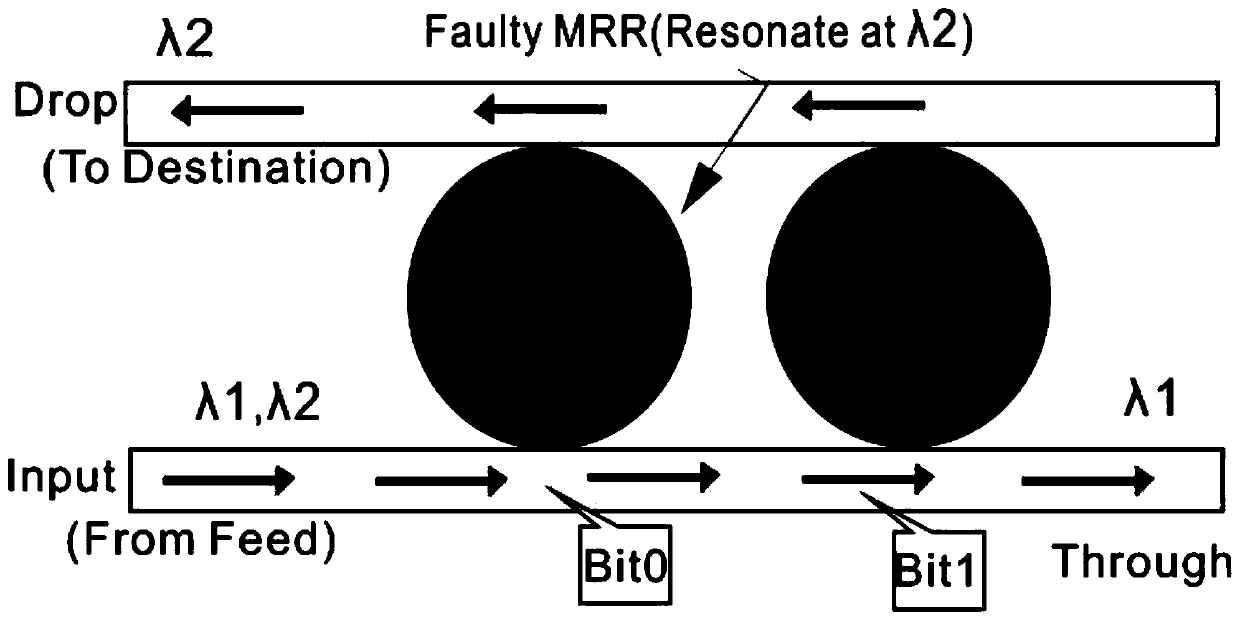

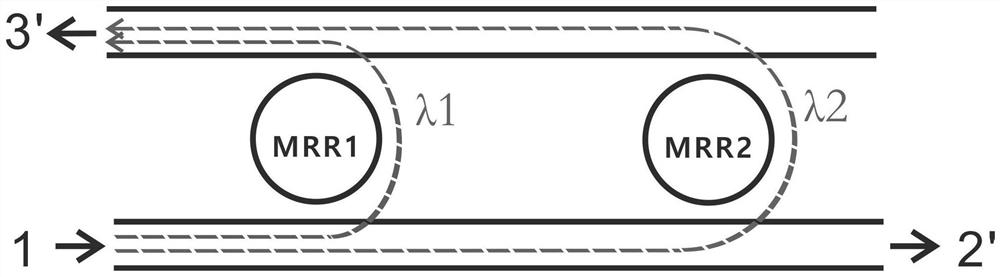

Bridging fault simulation device of optical router and control method

PendingCN111565339AImprove reliabilityEffective simulationMultiplex system selection arrangementsComputer networkMultiplexer

The invention discloses a bridging fault simulation device of an optical router and a control method. An analog multiplexer A is connected with two switchable first connecting branch components; the first connecting branch component is connected to the input of the either-or multiplexer 01, and the output of the either-or multiplexer 01 is output from the output port Q11 and the output port Q32 through an OR gate connected with the first connecting branch component; an analog multiplexer B is connected with the two switchable second connecting branch components; the second connecting branch component is connected to the input of the either-or multiplexer 02; and the output is output from the output port Q21 and the output port Q31 through an OR gate connected with the second connection branch component, so a single bridging fault of the MRR caused by heat sensitivity can be effectively simulated, and an important role is played in improving the reliability of the network-on-chip.

Owner:GUILIN UNIV OF ELECTRONIC TECH

Method for monitoring bridge fault on basis of video image

The invention discloses a method for monitoring a bridge fault on the basis of a video image and belongs to the technical field of a bridge monitoring method. The method is characterized by comprising the following steps of: (1) obtaining a video data of a preset position on a bridge; (2) comparing the video data; (3) obtaining a bridge fault condition; and (4) evaluating the use condition of the bridge and early warning. The invention aims to provide a high-detection-efficiency, high-accuracy and low-cost method for monitoring the bridge fault on the basis of the video image. The method is used for monitoring the bridge fault in real time.

Owner:广东省公路管理局

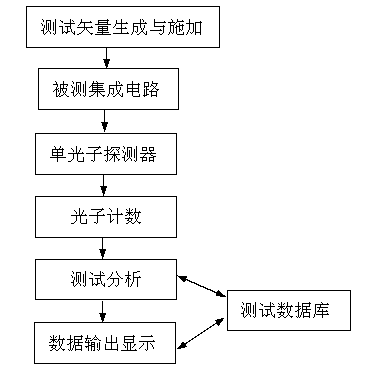

Single photon detection method and system for faults of integrated circuit

InactiveCN102435936BEasy to detectAchieve positioningDigital circuit testingPhoton detectionIntegrated circuit layout

The invention provides a single photon detection method and system for faults of an integrated circuit. According to the detection method, a set test vector is applied to a tested circuit, so that signal transition at the faults occurs, so that weak light is generated; and the weak light for the faults is detected by adopting a single photon detector. The detection system comprises a tested integrated circuit, an photon counting circuit module, a signal generator and a microcomputer, wherein the microcomputer is used for controlling the work of the whole system; and the microcomputer is also used for receiving detection data transmitted by the photon counting circuit module and comparing and analyzing the detection data with data in a database so as to realize detection and positioning of the faults in the circuit. According to the single photon detection method and system provided by the invention, various faults such as fixed faults, bridging faults, signal integrity faults and the like in the integrated circuit can be directly detected and positioned, and thereby the quality and the reliability of circuit chip products are improved.

Owner:SOUTH CHINA NORMAL UNIVERSITY

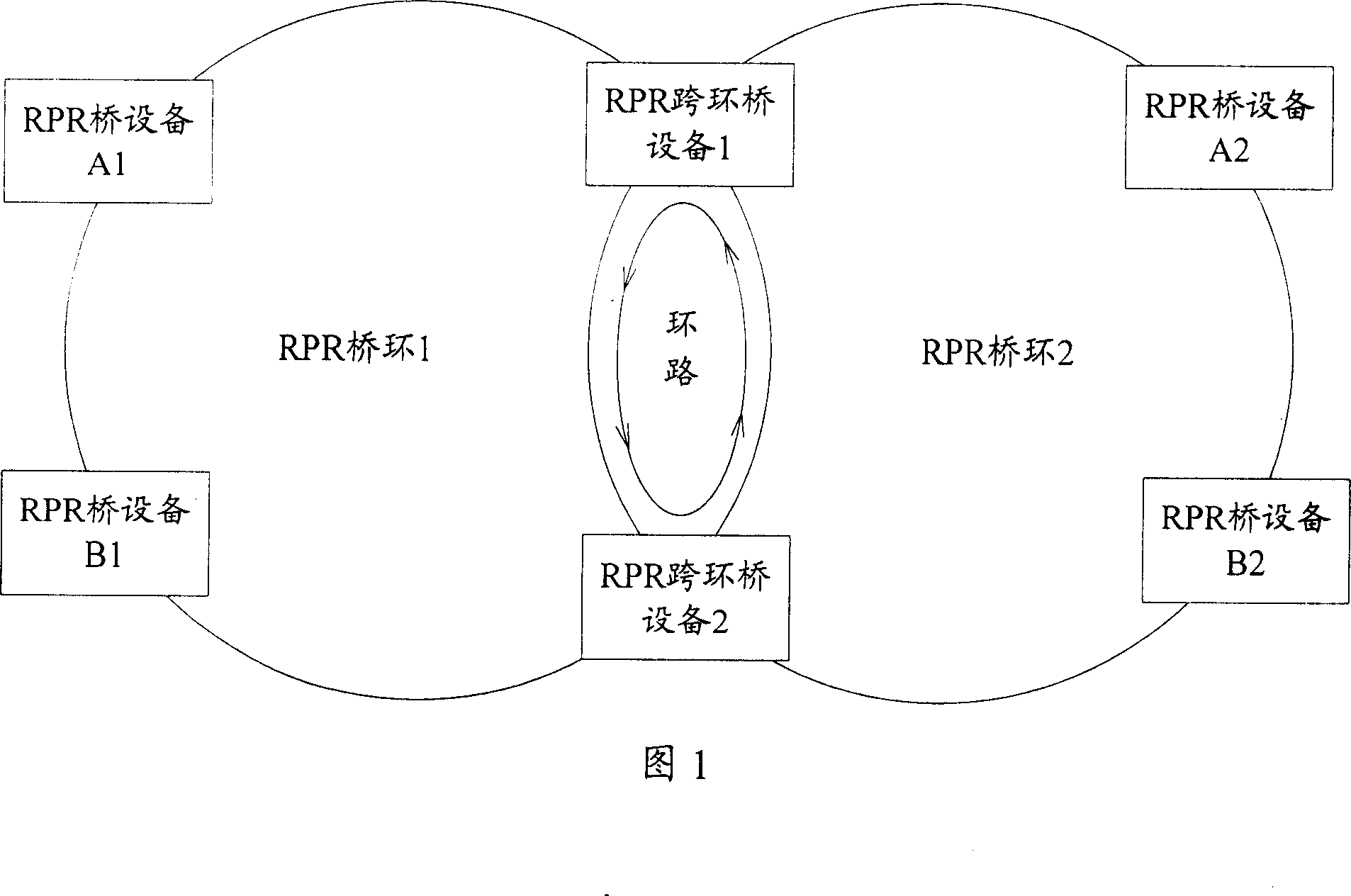

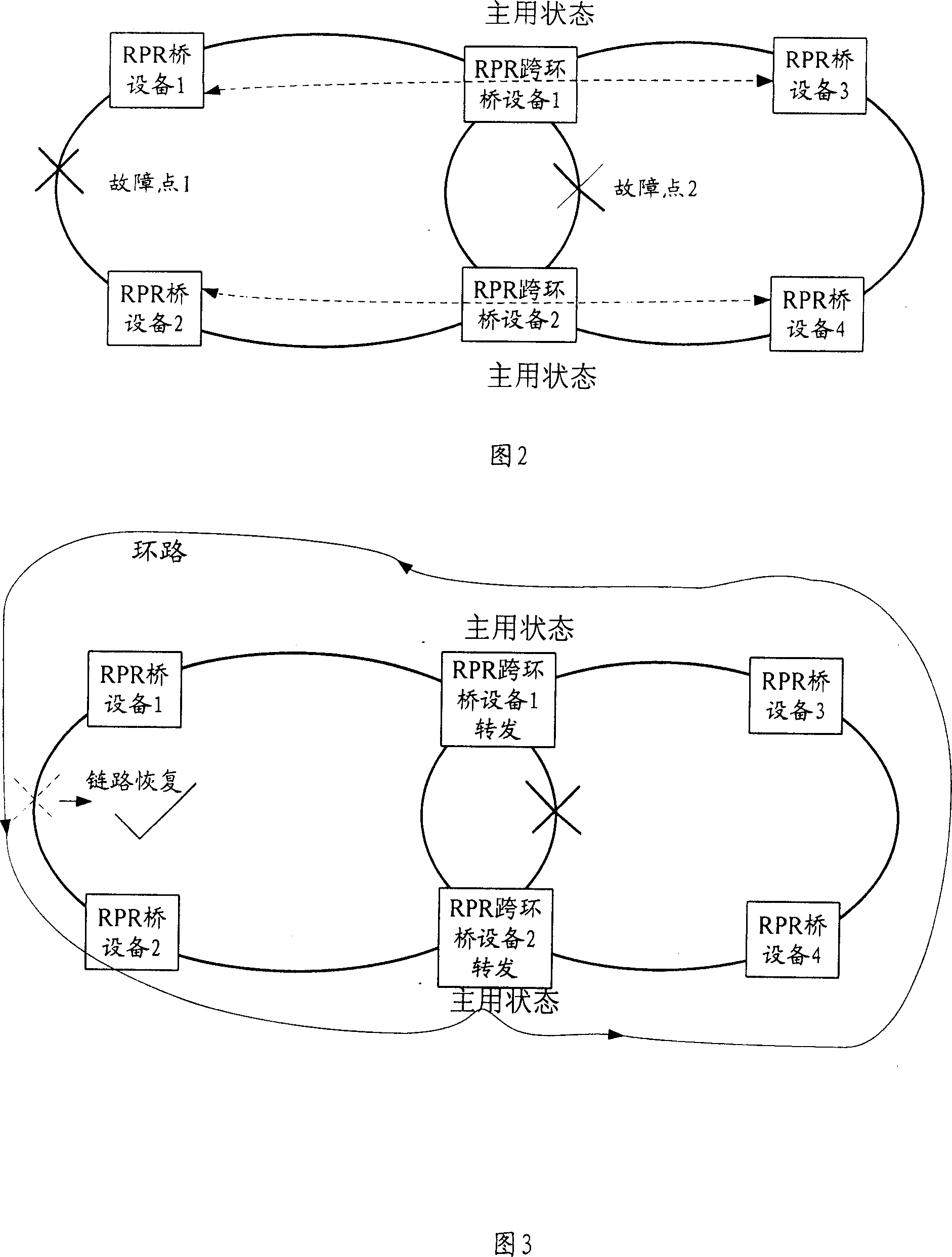

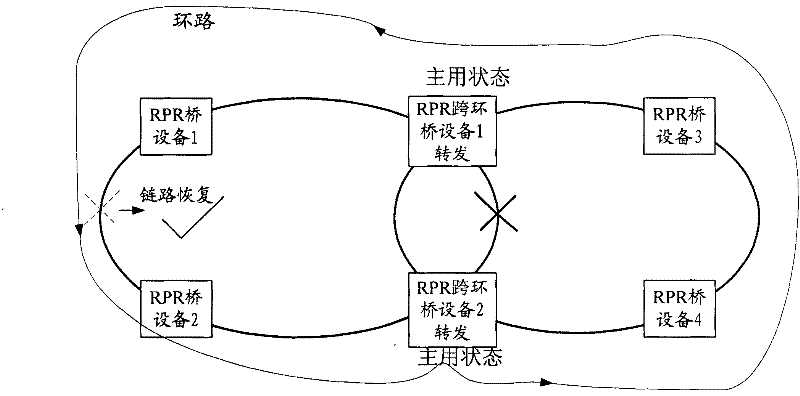

Loop prevention method after RPR bridge fault recovery

InactiveCN101136830AEnsure correct forwardingNo effect on convergenceLoop networksBridging faultComputer science

The method includes steps: (1) when learning that fault of the fault point in RPR bridge ring is recovered to normal, the method sets up maximal transmission unit value of the fault recovery node (FRN) to a prearranged value, and sends notification message in use for informing the fault point that the fault is recovered to transannular bridge device (TBD) in RPR bridge ring; (2) each RPR TBD in RPR bridge ring receives the notification message sent from FRN, as well as tests operating mode of each RPR TBD, and makes only one RPR TBD keep in main use state. Through cooperation between FRN and TBD, the invention ensures that transannular operation is forwarded correctly so as to solve loop issue occurs possibly after the fault point is recovered.

Owner:HUAWEI TECH CO LTD

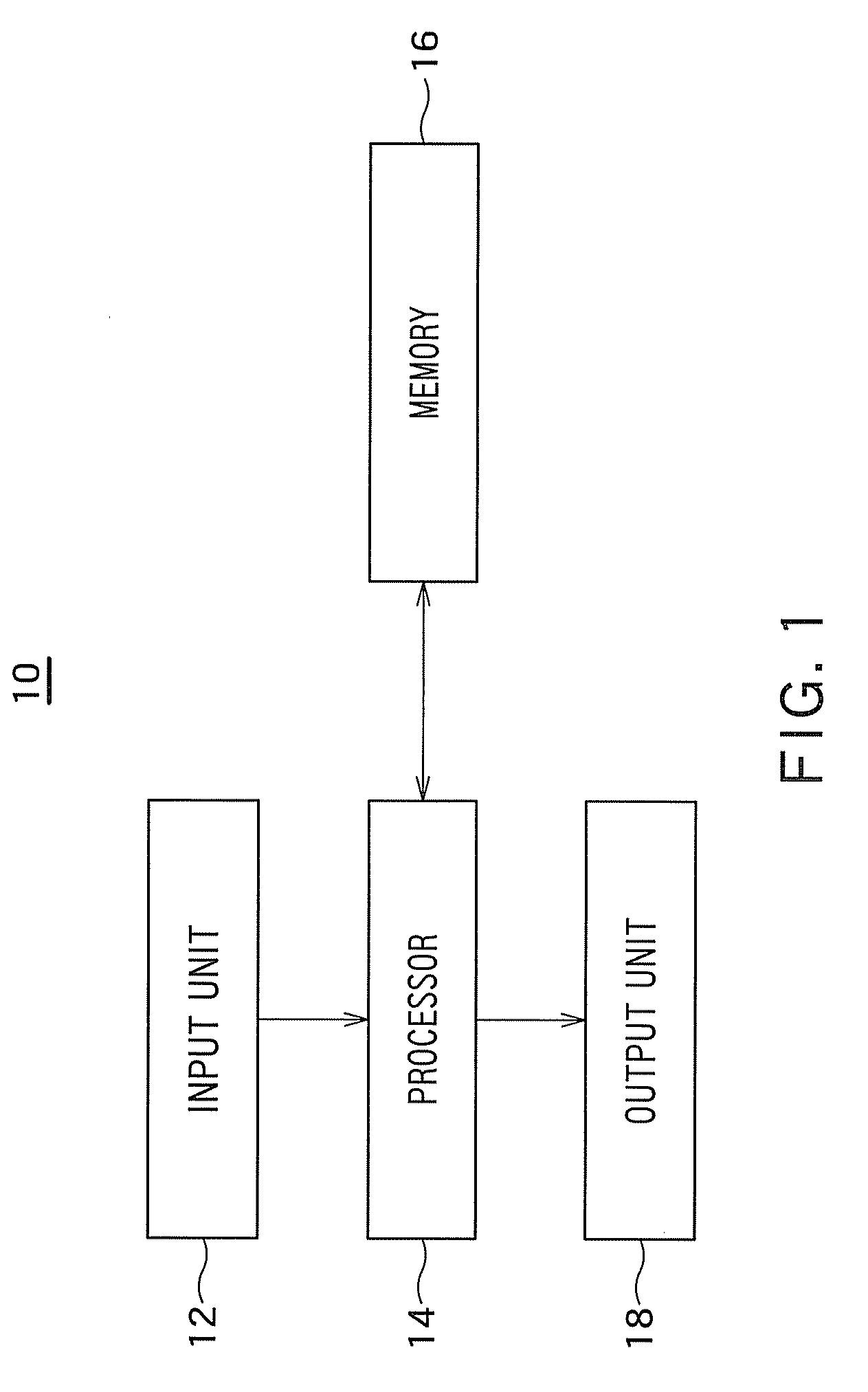

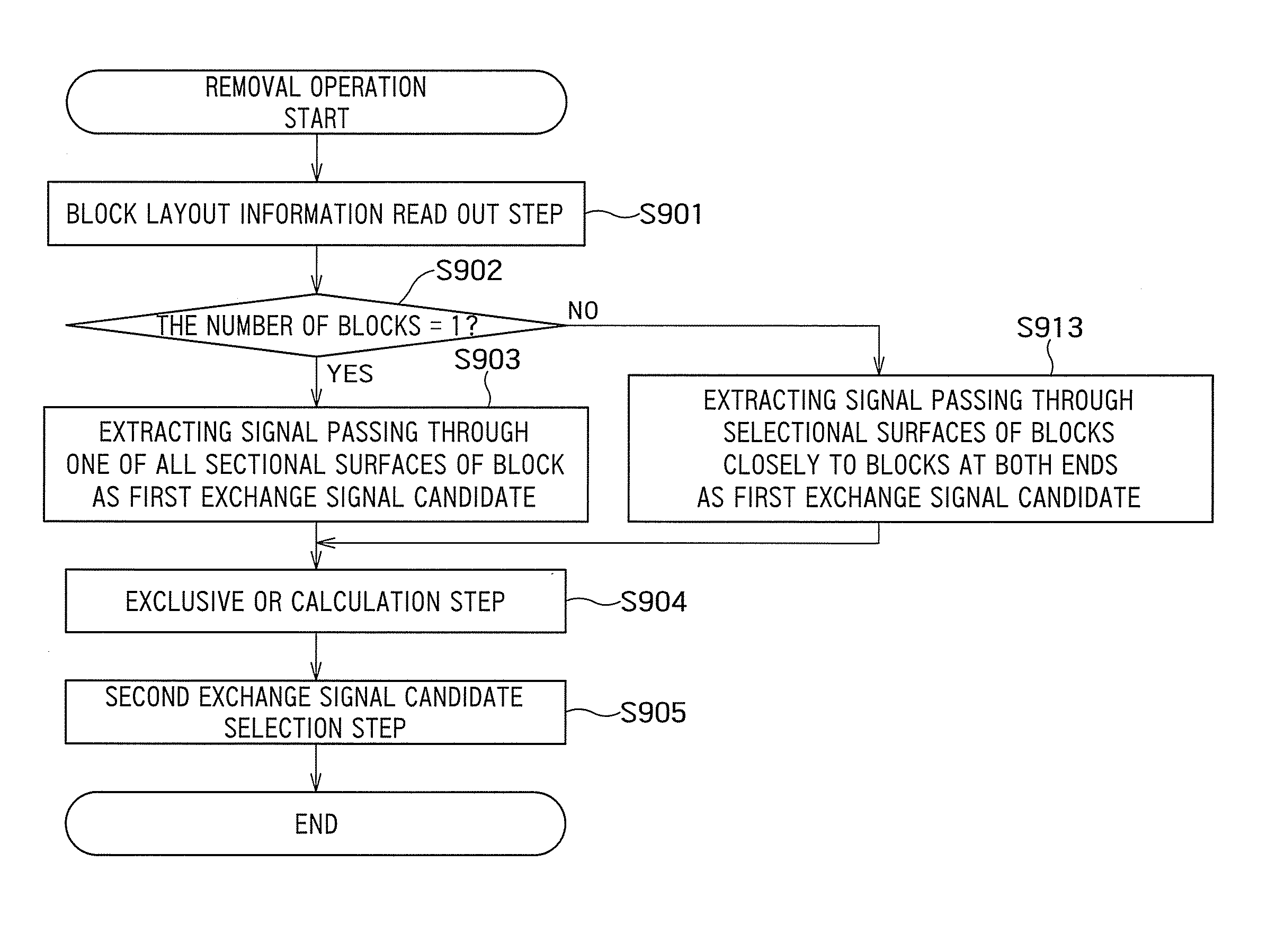

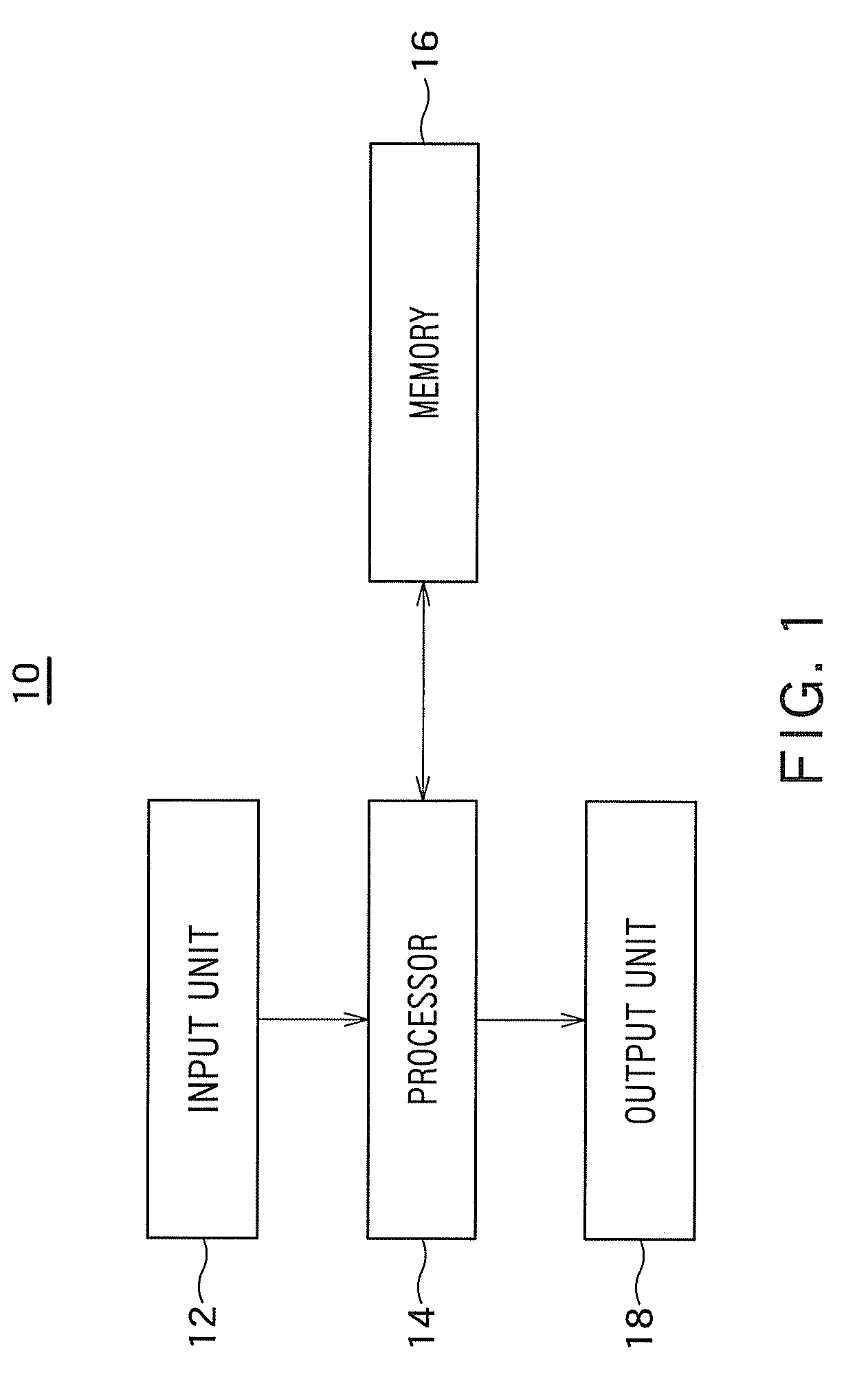

Bridge fault removal apparatus, bridge fault removal method, and computer readable medium comprising computer program code for removing bridge fault

A bridge fault removal apparatus includes a bridge fault extraction unit configured to extract a bridge fault from layout information of a semiconductor integrated circuit, a test pattern generator configured to generate the test pattern aiming at the bridge fault extracted by the bridge fault extraction unit, a logical value information calculator configured to calculate logical value information of all the signals in the semiconductor integrated circuit by applying the test pattern generated by the test pattern generator to logical connection information of the semiconductor integrated circuit, and a bridge fault remover configured to select an exchange signal candidate for an undetected bridge fault signal corresponding to the test pattern based on the logical value information calculated by the logical value information calculator.

Owner:KK TOSHIBA

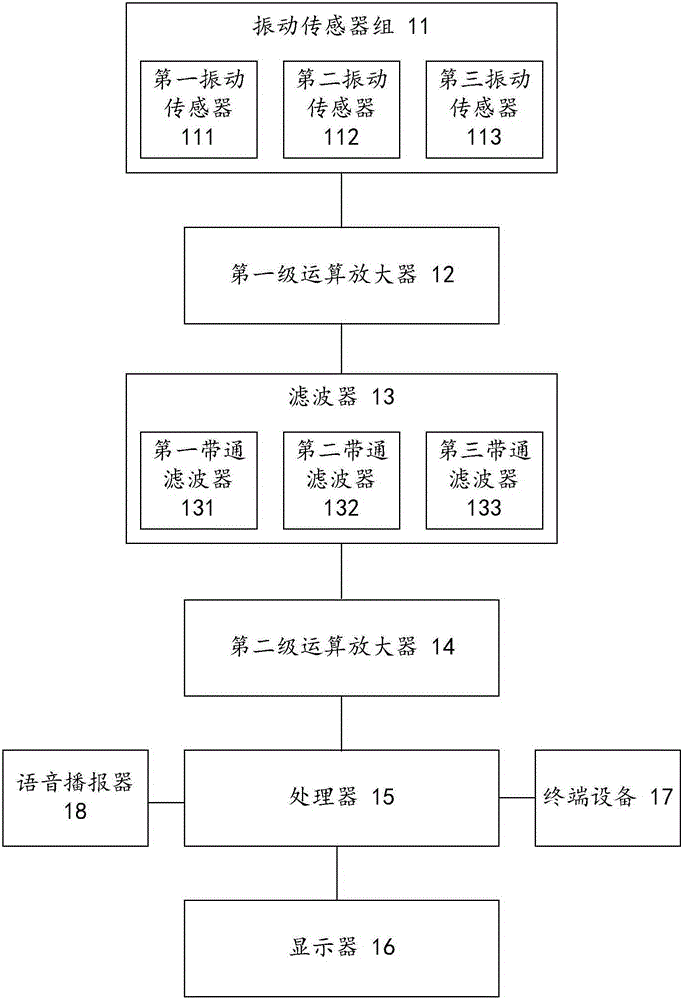

Bridge fault detection device

InactiveCN105181127AAvoid safety hazardsImprove detection accuracySubsonic/sonic/ultrasonic wave measurementAudio power amplifierBridging fault

The invention provides a bridge fault detection device. The bridge fault detection device comprises a vibration sensor group, a first-stage operational amplifier, a filter, a second-stage operational amplifier and a processor which are sequentially connected, wherein the vibration sensor group is used for converting acquired bridge vibration information into a current signal and transmitting the current signal to the first-stage operational amplifier; the first-stage operational amplifier is used for amplifying the current signal for the first time, generating a first voltage signal and transmitting the first voltage signal to the filter; the filter is used for carrying out filtering treatment on the first voltage signal and transmitting the filtered first voltage signal to the second-stage operational amplifier; the second-stage operational amplifier is used for amplifying the filtered first voltage signal for the second time, generating a second voltage signal and transmitting the second voltage signal to the processor; and the processor is used for carrying out preset analysis on the received second voltage signal for obtaining analysis results. Therefore, a manual detection manner is replaced, all the faults of a bridge can be more comprehensively detected, detection accuracy can be improved, and potential safety hazard of personnel during detection can be avoided.

Owner:浙江安侣智能科技有限公司

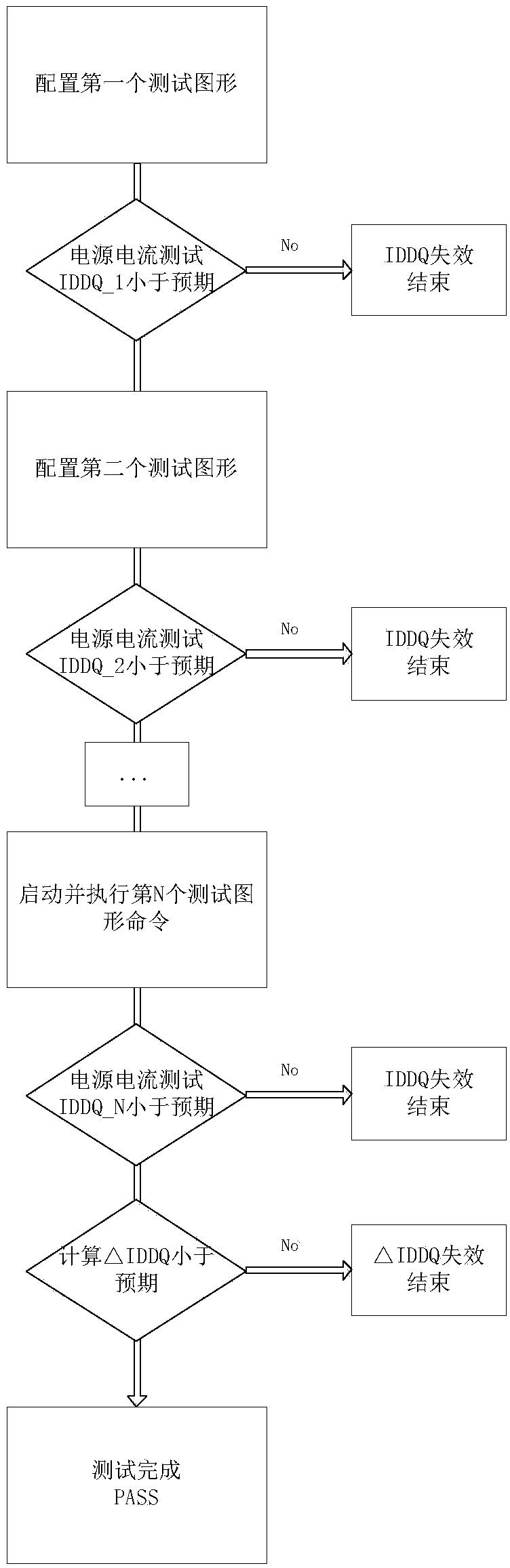

Method for judging IDDQ test by using current difference value

The invention discloses a method for judging the IDDQ test result by using the current difference value delta IDDQ (MAX(IDDQ_1, IDDQ_N)-MIN(IDDQ_1, IDDQ_N)) and using the result for improving the IDDQfault and the bridging fault test coverage rate. By using the method, the existing method of judging the IDDQ only by using two test points can be improved, and the test points are widened to any onetest point. Through the additional addition of the test points, the test coverage rate of the IDDQ test can be improved. Meanwhile, a current difference value is used as the basis for judging the IDDQ test; the defect of heavy background current under the deep sub-micron process conditions through the single judging of the current intensity during the IDDQ test can be reduced. The stable mass production during the chip mass production under the background of process deviation existence can be further ensured.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

Testing method for FPGA (field programmable gate array) single long wire and directly connected switch

ActiveCN102288870BEasy to operateThe testing process is simpleFault locationCircuit interrupters testingShift registerTest flow

The invention relates to a testing method for FPGA (field programmable gate array) single long wires and directly connected switches based on a Virtex structure, which comprises four configuration steps. The invention has the advantages that: the shift register chain mode is adopted to test 24 single long wires of an FPGA circuit, and bridging faults between signals of any two of the 24 wires in one group can be tested; the single long wires and directly connected switches of all CLBs (configurable logic blocks) can be tested only with four configuration codes; the testing process is simplified and the user operation is facilitated through initial configuration of the Blockram; the faults can be accurately positioned, four configuration steps are included, and when the deviation of the CLB positions in the last two configuration step is 4, the faults can be accurately positioned for the directly connected switches or single long wires of four CLBs; and when the fault positioning requirements are extremely accurate, the deviation of the CLB positions can be defined as 1, two configuration steps in total are adopted, and the fault can be accurately positioned for the directly connected switch or single long wire corresponding to one specific and unique CLB.

Owner:WUXI ESIONTECH CO LTD

Loop prevention method after RPR bridge fault recovery

InactiveCN101136830BEnsure correct forwardingNo effect on convergenceLoop networksBridging faultOperating system

The method includes steps: (1) when learning that fault of the fault point in RPR bridge ring is recovered to normal, the method sets up maximal transmission unit value of the fault recovery node (FRN) to a prearranged value, and sends notification message in use for informing the fault point that the fault is recovered to transannular bridge device (TBD) in RPR bridge ring; (2) each RPR TBD in RPR bridge ring receives the notification message sent from FRN, as well as tests operating mode of each RPR TBD, and makes only one RPR TBD keep in main use state. Through cooperation between FRN and TBD, the invention ensures that transannular operation is forwarded correctly so as to solve loop issue occurs possibly after the fault point is recovered.

Owner:HUAWEI TECH CO LTD

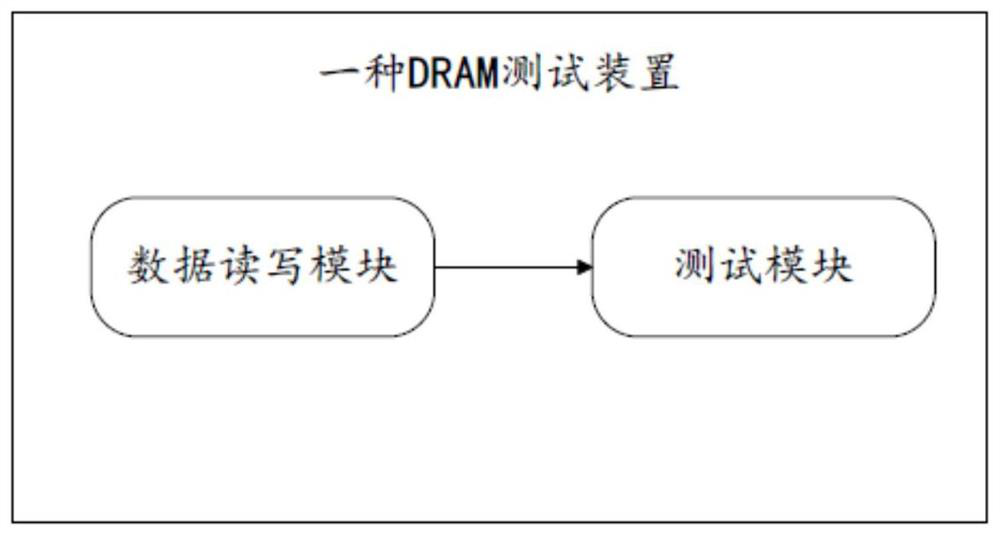

DRAM test method and device, readable storage medium and electronic equipment

PendingCN112599178AImprove reliabilityImprove fault coverageStatic storageFault coverageBridging fault

According to the invention, the DRAM to be tested is subjected to two rounds of testing, all the storage units written with the preset testing data are subjected to row alternate access, the comparison result is obtained in the row alternate access process, and the final testing result is obtained through the comparison result of the two rounds of testing; the invention can cover a previous test blind area and detect chip defects which are difficult to find in the prior art, so that multiple storage unit faults such as bridging faults and coupling faults are stimulated, the fault coverage rateis improved, the reliability of a test result is enhanced, and the benign of a product is improved.

Owner:BIWIN STORAGE TECH CO LTD

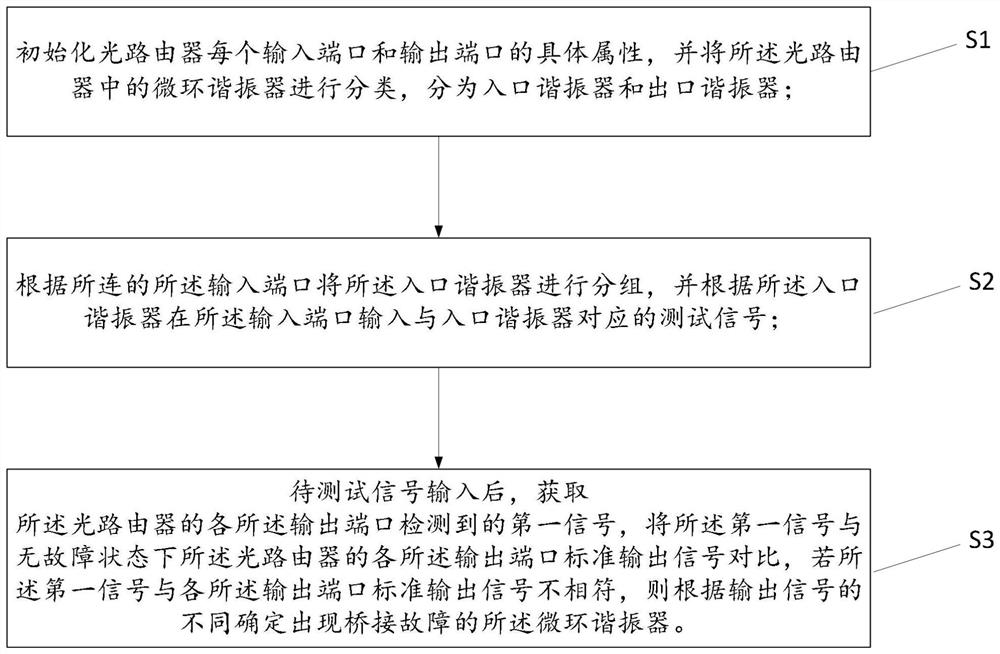

Optical router bridging fault positioning method based on single fault model

PendingCN113115136AImprove efficiencyHigh-accuracy fault scanning and locationMultiplex system selection arrangementsOptical routerBridging fault

The invention discloses an optical router bridging fault positioning method based on a single fault model, and the method comprises the following steps: initializing the specific attributes of each input port and each output port of an optical router, classifying micro-ring resonators in the optical router, and dividing the micro-ring resonators into inlet resonators and outlet resonators; grouping the inlet resonators according to the connected input ports, and inputting test signals corresponding to the inlet resonators at the input ports according to the inlet resonators; after a to-be-tested signal is input, acquiring a first signal detected by each output port of the optical router, comparing the first signal with a standard output signal of each output port of the optical router in a fault-free state, and if the first signal does not conform to the standard output signal of each output port, determining the micro-ring resonator with the bridging fault according to the difference of the output signals.

Owner:GUILIN UNIV OF ELECTRONIC TECH

Bridge fault removal apparatus, bridge fault removal method, and computer readable medium comprising computer program code for removing bridge fault

InactiveUS8886487B2Resistance/reactance/impedenceElectronic circuit testingBridging faultSemiconductor

A bridge fault removal apparatus includes a bridge fault extraction unit configured to extract a bridge fault from layout information of a semiconductor integrated circuit, a test pattern generator configured to generate the test pattern aiming at the bridge fault extracted by the bridge fault extraction unit, a logical value information calculator configured to calculate logical value information of all the signals in the semiconductor integrated circuit by applying the test pattern generated by the test pattern generator to logical connection information of the semiconductor integrated circuit, and a bridge fault remover configured to select an exchange signal candidate for an undetected bridge fault signal corresponding to the test pattern based on the logical value information calculated by the logical value information calculator.

Owner:KK TOSHIBA

Method for testing field programmable gate array (FPGA) single-long line slant switches

ActiveCN102253329BEasy to operateThe testing process is simpleCircuit interrupters testingShift registerGate array

Owner:WUXI ESIONTECH CO LTD

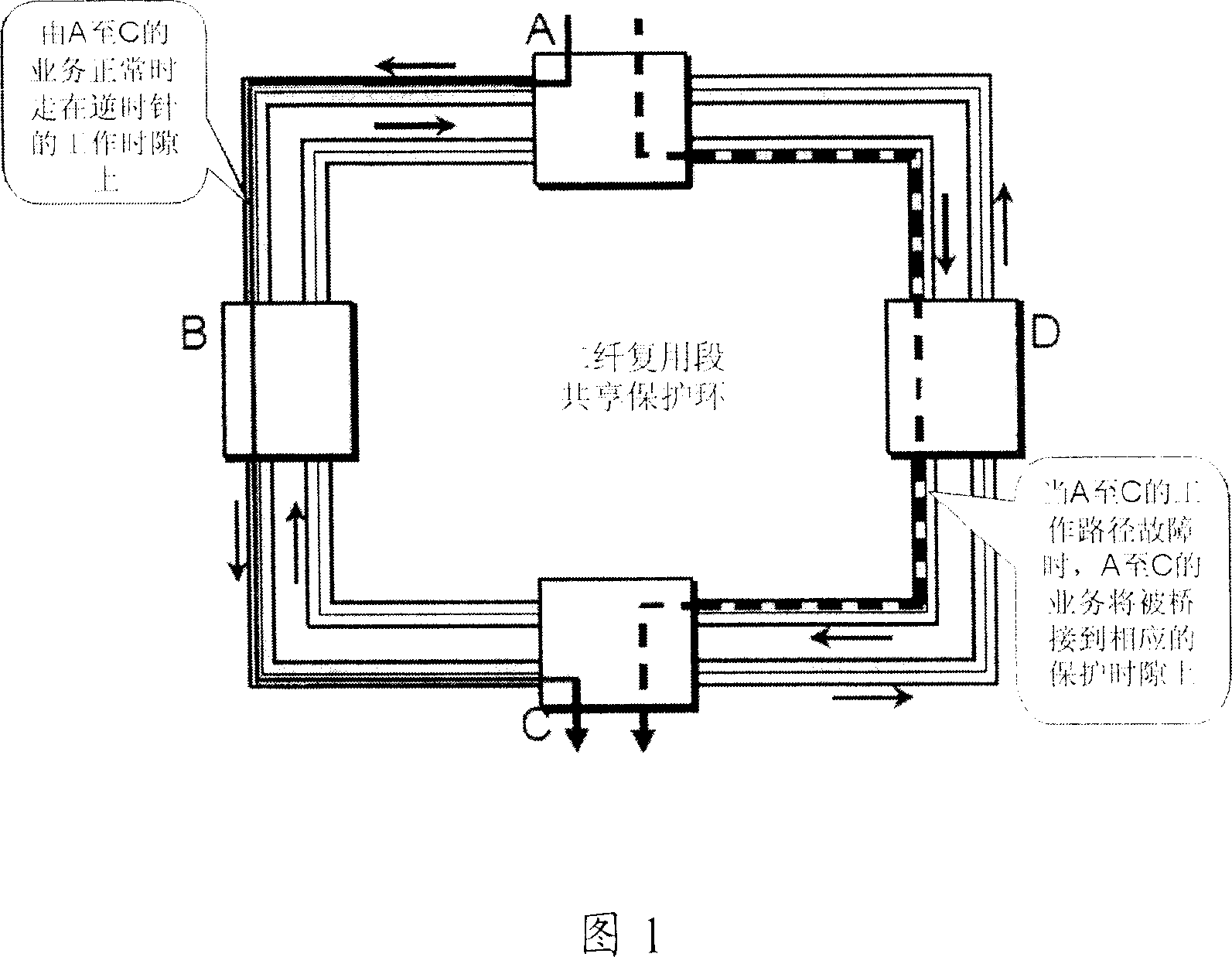

Multiplex section shared loop protecting method

Present invention relates to multiplexing segment sharing ring circuit protection method, which contains pre - linking protection channel among sites to protection channel loop, when circuit between two sites in loop occurs fault, executing follow steps, A, when detecting circuit fault in any end of site, sending multiplexing segment sharing fault indication message to opposite site of fault circuit, B, fault circuit two ends site detecting the circuit fault alerting signal or receiving multiplexing segment far end fault indication information, then respectively bridging fault circuital transmitting / reception channel to corresponding protection channel to complete the switch from working channel to protection channel. Said invention can raise the switching speed and reliability between work channel and protection channel.

Owner:HUAWEI TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com