Semiconductor device

A semiconductor and device technology, which is applied in the field of semiconductor devices, can solve the problems of unstable size and shape of elastomers, unsteady semiconductor chip bonding process, and difficult elastomers, and achieve excellent noise resistance, stable size and shape, and high The effect of yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

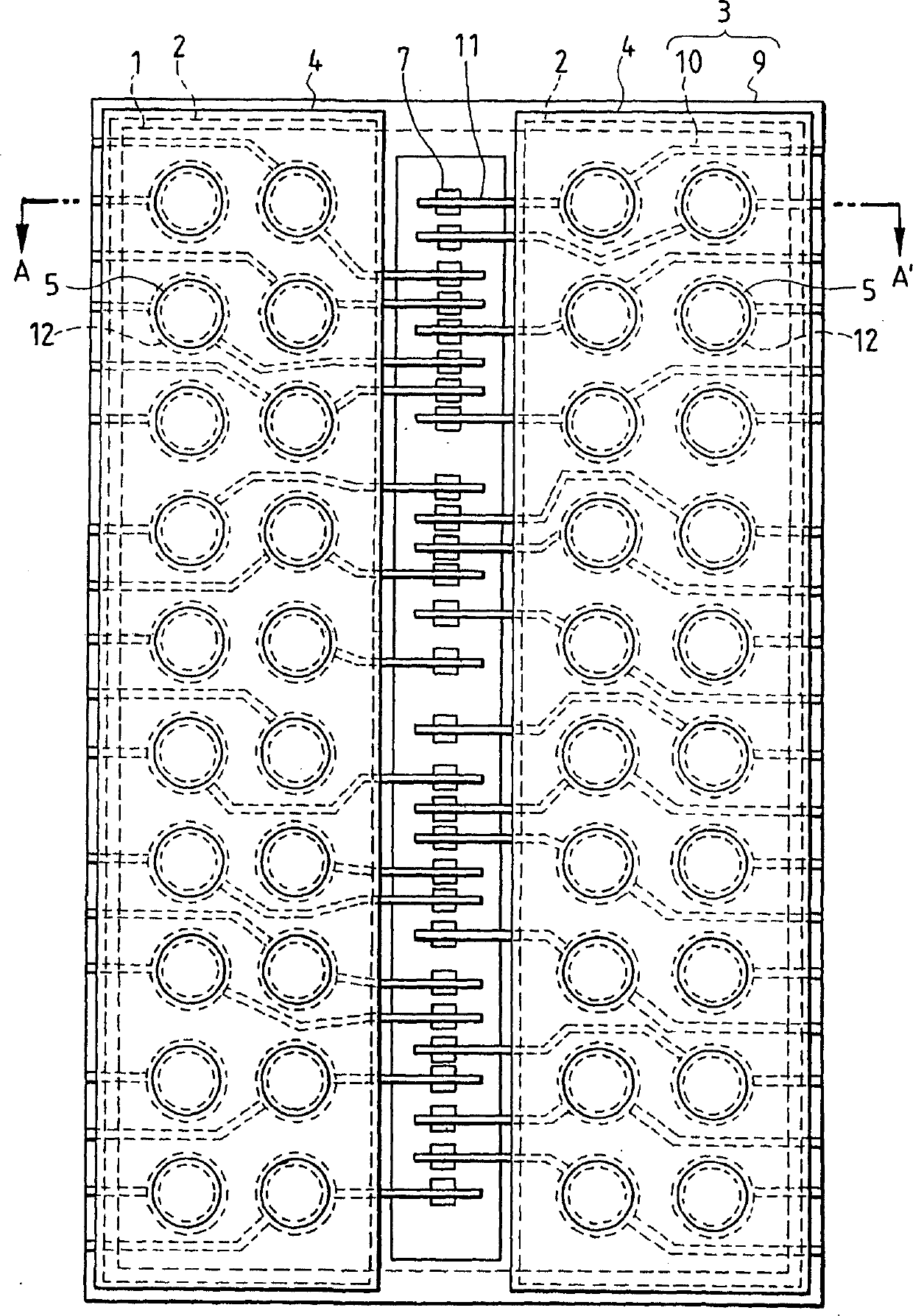

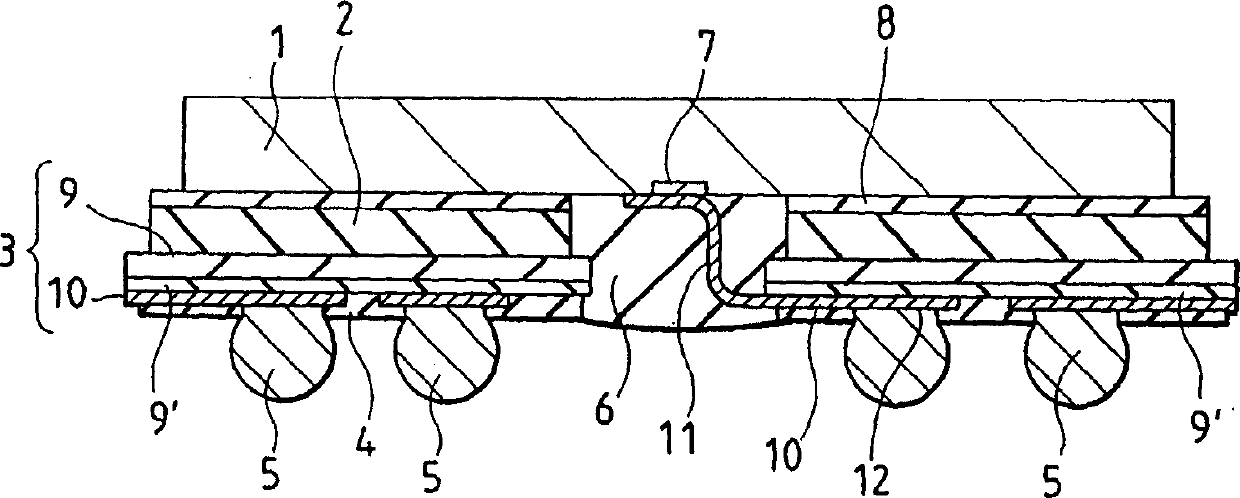

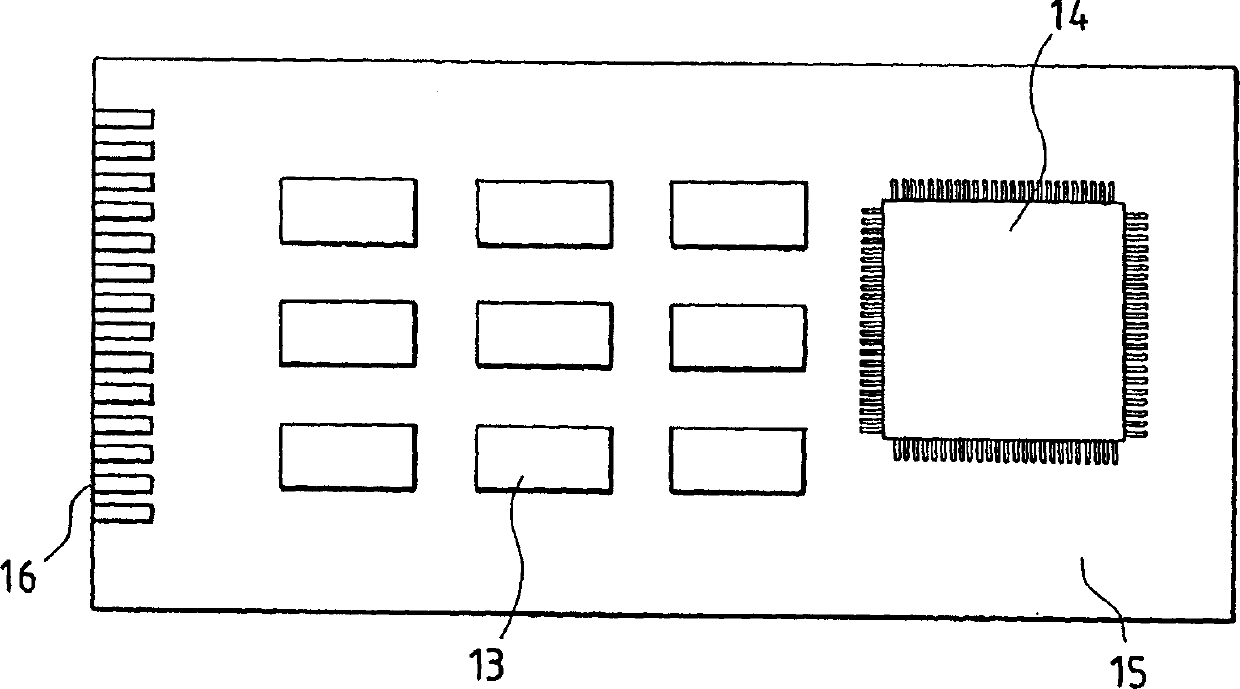

[0156] The plan view of Fig. 1 shows the semiconductor integrated circuit device of Embodiment 1 of the present invention; Fig. 2 is the cross-sectional view at AA' section line place of Fig. 1; The plan view and cross-sectional view of Fig. 3 and Fig. 4 show semiconductor The assembly state of the integrated circuit device assembled on the assembly substrate; what Fig. 5 shows is the flow chart of the assembly process of the semiconductor integrated circuit device; Fig. 6-Fig. 58, Fig. 76-Fig. It is an explanatory diagram for explaining the comparison between the characteristics of the circuit device and the semiconductor integrated circuit device of the comparative example studied by the present inventors. The description of these figures will be described item by item in each technical item described later.

[0157] First, the configuration of the semiconductor integrated circuit device of the first embodiment will be described with reference to FIGS. 1 and 2. FIG.

[0158...

Embodiment 2

[0292] The semiconductor integrated circuit device of this embodiment 2 is the same as the above-mentioned embodiment 1, and it is made into a semiconductor package of a ball grid array type. The difference between the semiconductor integrated circuit device and the above-mentioned embodiment 1 is whether the surface wiring structure is a premise technology. , but is based on the premise of the rear wiring structure and is used to improve it. For example, as shown in Figure 59 and Figure 60, the elastomer 2 that has been bonded to the main surface of the semiconductor chip 1 and will be In the structure between the flexible wiring board 3 (wiring board) on the main surface of the elastic body 2 , a solder resist layer 56 (insulating film) has been formed on the back surface of the flexible wiring board 3 .

[0293] That is, the flexible wiring substrate 3 becomes composed of the substrate base material 9 to be the base material of the flexible wiring substrate 3 and the wiring ...

Embodiment 3

[0302] 63 is a plan view of a semiconductor integrated circuit device as Embodiment 3 of the present invention viewed from the back of the semiconductor chip; FIG. 62 is a plan view; FIG. 63 is a sectional view; FIG. 64 is an enlarged sectional view of part A of FIG. 63; FIG. 65 It is a plan view for explaining the wiring structure of the wiring board.

[0303] The semiconductor integrated circuit device of this embodiment 3 does not use the semiconductor package with the so-called fan-in central pad structure of the above-mentioned embodiments 1 and 2, but instead uses a peripheral pad structure as shown in Figures 61-65. In the semiconductor chip 1a, the solder bumps 5a connected to the bonding pads of the semiconductor chip 1a are arranged on the area inside from the outer circumference of the semiconductor chip 1a to form a so-called fan-in peripheral pad. Package construction. Also, even in this embodiment 3. It also becomes each technical item that has already adopted ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com