Manufacturing method of SiC-based super-junction IGBT (Insulated Gate Bipolar Transistor) with low off-state loss

A fabrication method and off-state technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as charge-imbalanced Si-based superjunction devices, reduce ion implantation processes, improve on-state characteristics and good performance. efficiency, and the effect of optimizing the cell structure of the device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

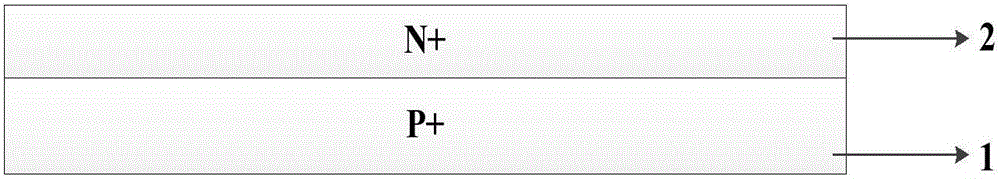

[0030] Before making the SiC-base superjunction IGBT with low off-state loss of the present invention, earlier RCA cleans the p+ type substrate 1 of SiC (referring to figure 2 ). Specifically:

[0031] (a) Ultrasonic cleaning with acetone and ethanol in sequence, followed by rinsing with deionized water.

[0032] (b) Boiling the SiC substrate 1 after organic ultrasonication in concentrated sulfuric acid and hydrogen peroxide solution for at least 10 minutes.

[0033] (c) Boil the substrate 1 boiled in concentrated sulfuric acid with No. 1 solution and No. 2 solution for more than 10 minutes respectively, rinse it with deionized water, and dry it with nitrogen gas for use. The No. 1 liquid is a mixture of ammonia, hydrogen peroxide and deionized water, and the No. 2 liquid is a mixture of hydrochloric acid, hydrogen peroxide and deionized water.

[0034] (d) Soak the rinsed substrate in hydrofluoric acid for at least 1 min to remove the surface oxide layer.

[0035] The do...

no. 2 example

[0070] The cleaning of the SiC p+ type substrate 1 before fabricating the SiC-based super-junction IGBT with low off-state loss of the present invention is the same as that of the first embodiment, and will not be repeated here.

[0071] The doping concentration of the p+ type substrate 1 needs to meet a specific value to meet a certain injection efficiency, which is roughly 1×10 18 cm -3 ~3×10 18 cm -3 , SiC p+-type substrate 1 can undergo a series of thinning, grinding, polishing, cleaning and other processes on the sample through mechanical processing and chemical reaction methods, so that the surface of the sample can reach the required thickness and flatness.

[0072] S1: Refer to figure 2 , epitaxially grow n+ type buffer layer 2 on SiC p+ type substrate 1 by chemical vapor deposition or other methods of epitaxially growing materials. The source of epitaxial growth is silane or trichlorosilane, ethylene, etc. or propane, etc., the thickness of the n+ type buffer lay...

no. 3 example

[0077] The cleaning of the SiC p+ type substrate 1 before fabricating the SiC-based super-junction IGBT with low off-state loss of the present invention is the same as that of the first embodiment, and will not be repeated here.

[0078] The doping concentration of the p+ type substrate 1 needs to meet a specific value to meet a certain injection efficiency, which is roughly 6.5×10 17 cm -3 ~8.5×10 17 cm -3 , SiC p+-type substrate 1 can undergo a series of thinning, grinding, polishing, cleaning and other processes on the sample through mechanical processing and chemical reaction methods, so that the surface of the sample can reach the required thickness and flatness.

[0079] S1: Refer to figure 2 , epitaxially grow n+ type buffer layer 2 on SiC p+ type substrate 1 by chemical vapor deposition or other methods of epitaxially growing materials. The source of epitaxial growth is silane or trichlorosilane, ethylene, etc. or propane, etc., the thickness of the n+ type buffer...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com