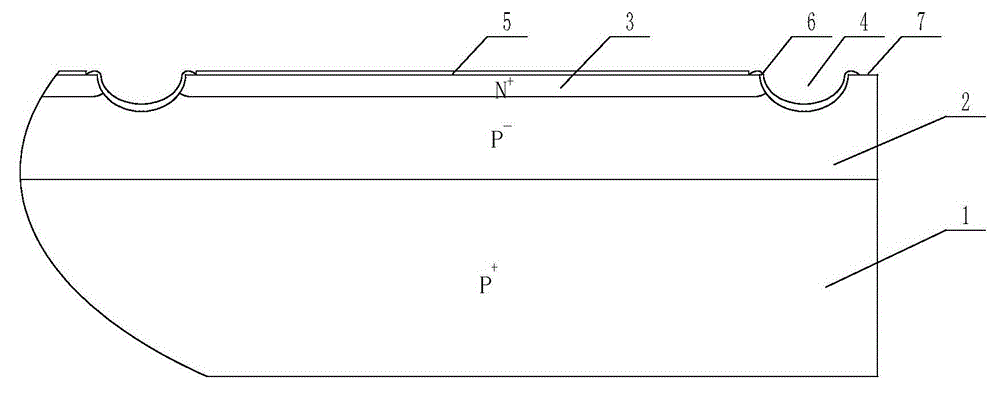

Transient voltage suppression diode array chip according to mesa trench isolation method and production technology thereof

A technology of transient voltage suppression and diode array, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problems of vulnerable devices to be protected, large voltage resilience, diode breakdown, etc., to achieve protection from damage, reduce leakage current, and protect the device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The chip of the transient voltage suppression diode array with mesa trench isolation method according to the present invention and its production process will be described in further detail below through specific embodiments.

[0037] Such as Figure 5 As shown, a production process of a mesa trench isolation method transient voltage suppression diode array chip includes the following steps:

[0038] 1) Cleaning before oxidation: through electronic cleaning agent SC 2 , Deionized water ultrasonic cleaning and other processes, chemically treat the surface of the silicon wafer to obtain a clean original P-type silicon wafer with a resistivity of 0.005~0.006Ω.cm;

[0039] 2) Oxidation: the cleaned silicon wafer is grown on both sides in an oxidation furnace at 1100~1200℃ as a mask, the thickness of the oxide film is 1.5μm~2μm;

[0040] 3) Removal of single-sided oxide film: Coat a layer of photoresist on one side of the oxidized silicon wafer, and use ammonium fluoride etching solu...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Resistivity | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com