Double-end assembly line type copy bit line circuit

A kind of duplicating bit line and pipeline type technology, applied in the direction of information storage, static memory, digital memory information, etc., can solve the problems of SRAM chip performance degradation, affecting chip speed, increasing bit line precharge time, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

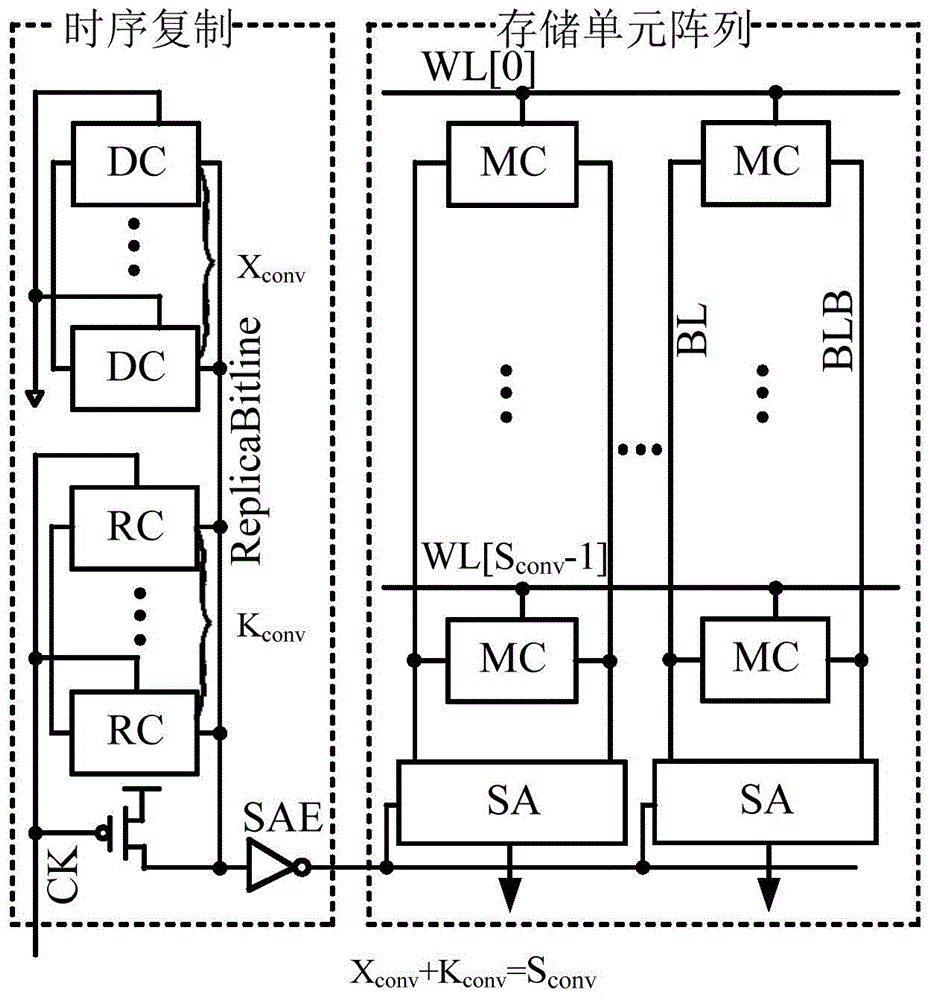

[0059] Image 6 It is a schematic structural diagram of a double-ended pipeline replication bit line circuit provided by Embodiment 1 of the present invention. like Image 6 As shown, the circuit mainly includes:

[0060] The first inverter INV1, the second inverter INV2, the third inverter INV3, the first NAND gate NAND1, the first replica bit line RBL, the second replica bit line RBLB, the first pre-filled PMOS transistor PR1, The second pre-charged PMOS transistor PR2, the first D flip-flop DFF 1 to the Nth D flip-flop DFF N , the first control circuit CTL 1 to the Nth control circuit CTL N , the first charging PMOS transistor P 1 To charge the Nth PMOS transistor P N , N / 2 sets of replication units RC and a set of X redundancy units DC in total of K in each group; wherein, N is an even number, indicating the number of times of flow;

[0061] The PR signal is connected to the gates of the first pre-charged PMOS transistor PR1 and the second pre-charged PMOS transist...

Embodiment 2

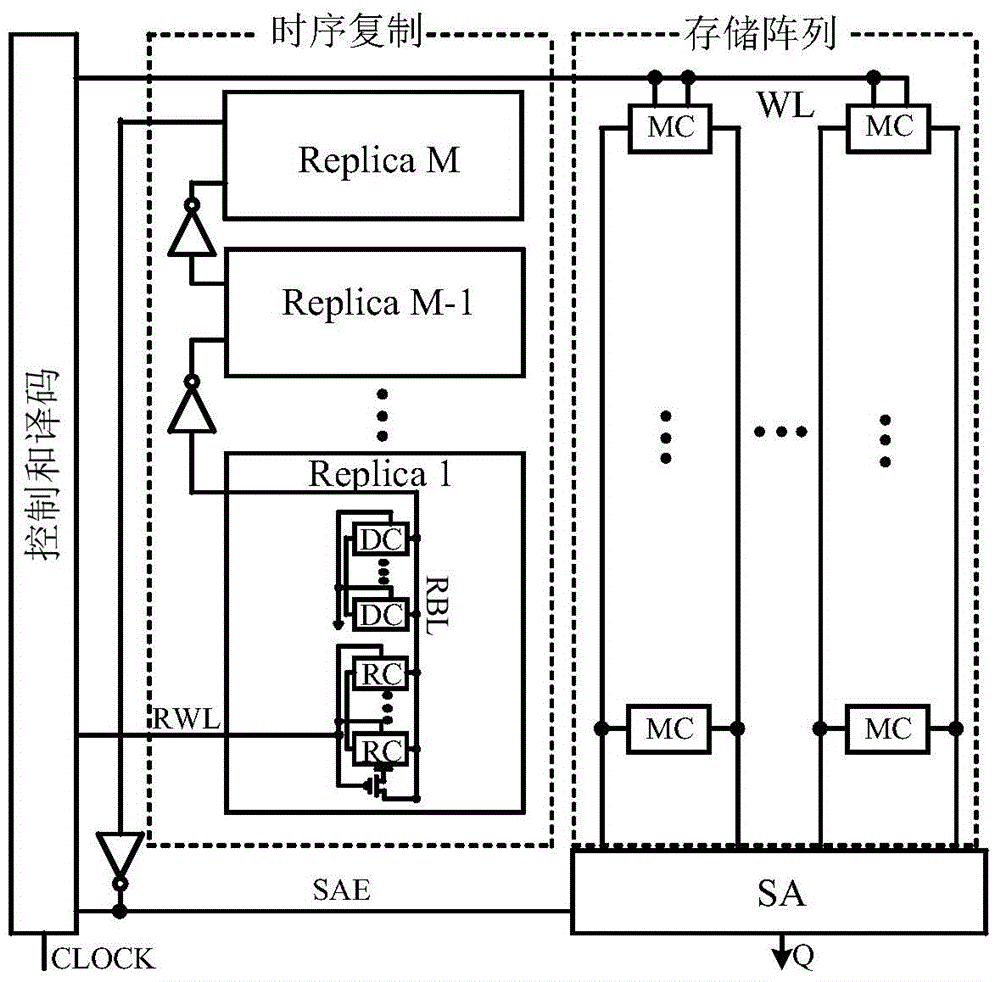

[0083] Figure 7 A schematic structural diagram of yet another double-ended pipeline replication bit line circuit provided by Embodiment 2 of the present invention. like Figure 7 As shown, it mainly includes:

[0084] The first inverter INV1, the second inverter INV2, the third inverter INV3, the first NAND gate NAND1, the first replica bit line RBL, the second replica bit line RBLB, the first pre-filled PMOS transistor PR1, The second pre-charged PMOS transistor PR2, the first D flip-flop DFF 1 to the Nth D flip-flop DFF N , the first control circuit CTL 1 to the Nth control circuit CTL N , the first charging PMOS transistor P 1 To charge the Nth PMOS transistor P N , each group of K total (N+1) / 2 groups of replication units RC and a group of X redundancy units DC; wherein, N is an odd number, indicating the number of times of flow;

[0085] The PR signal is connected to the gates of the first pre-charged PMOS transistor PR1 and the second pre-charged PMOS transistor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com