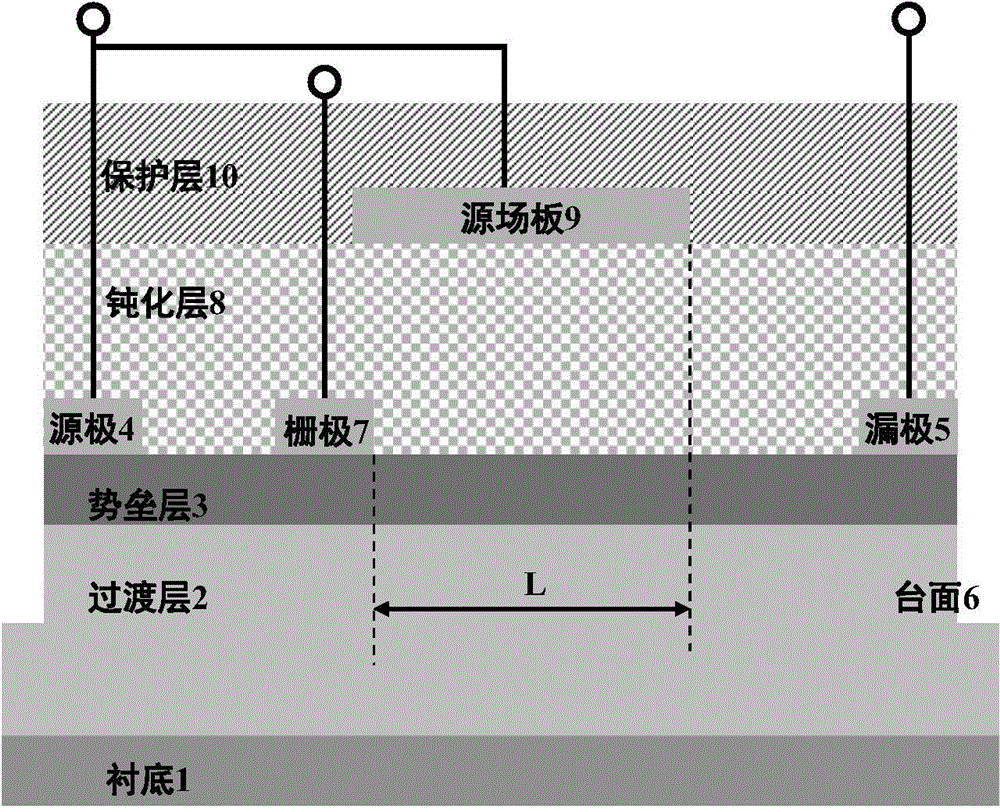

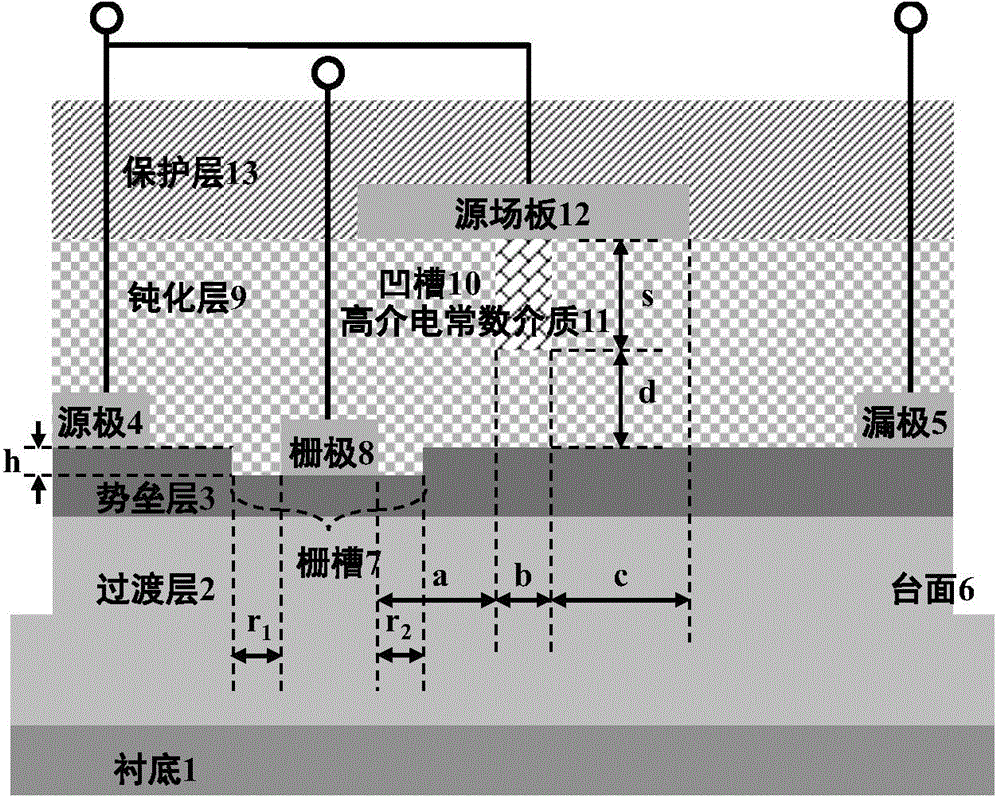

Heterojunction field effect transistor of composite source field plate based on medium modulation

A heterojunction field effect, source field plate technology, applied in transistors, semiconductor devices, electrical components, etc., can solve the problems of reducing the yield of the device, tedious process debugging, increasing the difficulty of the device, etc., to improve reliability and reduce electric field. , the effect of reducing the gate leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

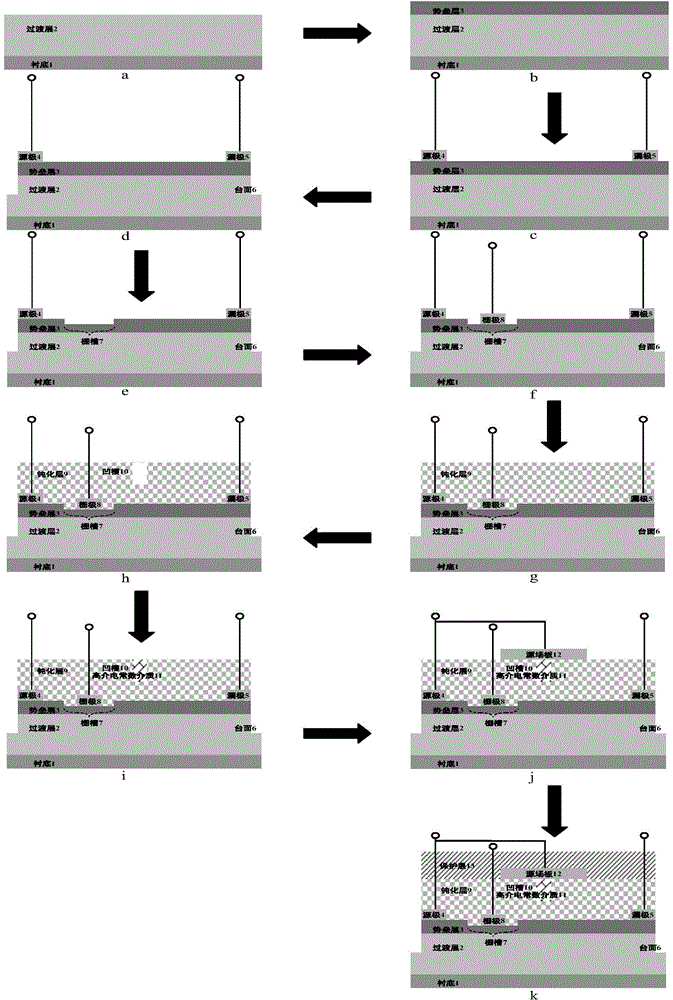

[0041] Embodiment one: making substrate is sapphire, and passivation layer is Al 2 o 3 , the protective layer is SiO 2 , the high dielectric constant medium 11 is HfO 2 , The source field plate is a composite source field plate heterojunction field effect transistor based on dielectric modulation with Ti / Mo / Au metal combination.

[0042] Step 1. On the sapphire substrate 1, make the transition layer 2 by epitaxial GaN material from bottom to top, such as image 3 a.

[0043] An undoped transition layer 2 with a thickness of 1 μm is epitaxially formed on the sapphire substrate 1 by metal organic chemical vapor deposition technology, and the transition layer is composed of GaN materials with thicknesses of 30 nm and 0.97 μm from bottom to top. The process conditions used for the epitaxial lower layer GaN material are: temperature 530°C, pressure 45 Torr, hydrogen gas flow rate 4400 sccm, ammonia gas flow rate 4400 sccm, gallium source flow rate 22 μmol / min; the process condi...

Embodiment 2

[0064] Embodiment 2: The substrate is made of silicon carbide, and the passivation layer is SiO 2 , the protective layer is SiN, and the high dielectric constant dielectric 11 is Al 2 o 3 , The source field plate is a composite source field plate heterojunction field effect transistor based on dielectric modulation with Ti / Ni / Au metal combination.

[0065] Step 1. Epitaxially AlN and GaN materials on the silicon carbide substrate 1 to form the transition layer 2, such as image 3 a.

[0066] 1.1) Using metal-organic chemical vapor deposition technology to epitaxially undoped AlN material with a thickness of 50nm on the silicon carbide substrate 1; the process conditions for the epitaxy are: temperature is 1000°C, pressure is 45Torr, hydrogen flow rate is 4600sccm, The flow rate of ammonia gas is 4600 sccm, and the flow rate of aluminum source is 5 μmol / min;

[0067] 1.2) Using metal-organic chemical vapor deposition technology to epitaxially GaN material with a thickness o...

Embodiment 3

[0101] Embodiment three: the substrate is made of silicon, the passivation layer is SiN, and the protective layer is SiO 2 , the high dielectric constant medium 11 is HfO 2 , The source field plate is a composite source field plate heterojunction field effect transistor based on dielectric modulation with Ti / Pt / Au metal combination.

[0102] Step A. Epitaxial AlN and GaN materials on the silicon substrate 1 from bottom to top to make the transition layer 2, such as image 3 a.

[0103] A1) Using metal-organic chemical vapor deposition technology at a temperature of 800° C., a pressure of 40 Torr, a flow rate of hydrogen gas of 4000 sccm, a flow rate of ammonia gas of 4000 sccm, and a flow rate of aluminum source of 25 μmol / min, the epitaxy on the silicon substrate 1 AlN material with a thickness of 200nm;

[0104] A2) Using metal-organic chemical vapor deposition technology at a temperature of 980°C, a pressure of 45 Torr, a flow rate of hydrogen gas of 4000 sccm, a flow ra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com