Packaging method for metal oxide semiconductor thin-film transistor

A technology for oxide semiconductors and thin film transistors, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as destruction of semiconductors and device performance degradation, to improve stability, prevent gas molecules from interacting, and save costs. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

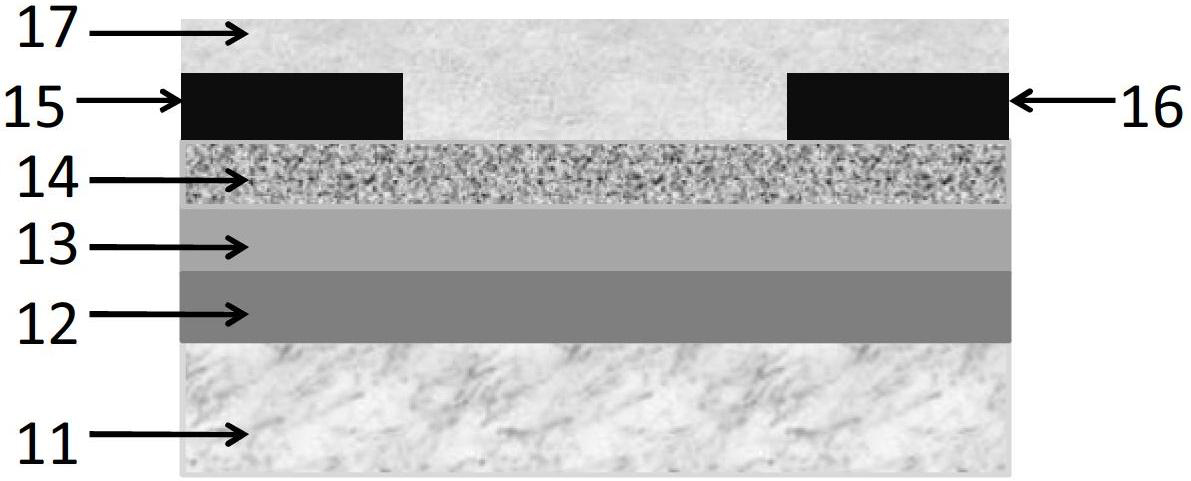

[0036] A P-type heavily doped silicon wafer is used as the insulating substrate 11, and a gate electrode 12 is prepared on the upper surface of the insulating substrate 11 by thermal evaporation using a mask with a certain pattern, and the material of the gate electrode 12 is metal; Use SiOx to prepare gate insulating layer 13 on both with thermal growth method; ZnO is prepared as metal oxide active layer 14 on gate insulating layer 13 with spin-coating process; The source electrode 15 and the drain electrode 16 are prepared on the metal oxide active layer 14; finally, polydimethylsiloxane is prepared by drop coating on the metal oxide active layer 14, the source electrode 15 and the drain electrode 16 The device protection layer 17 is annealed after film formation, and the annealing temperature does not exceed 150° C., thereby completing the packaging of the transistor.

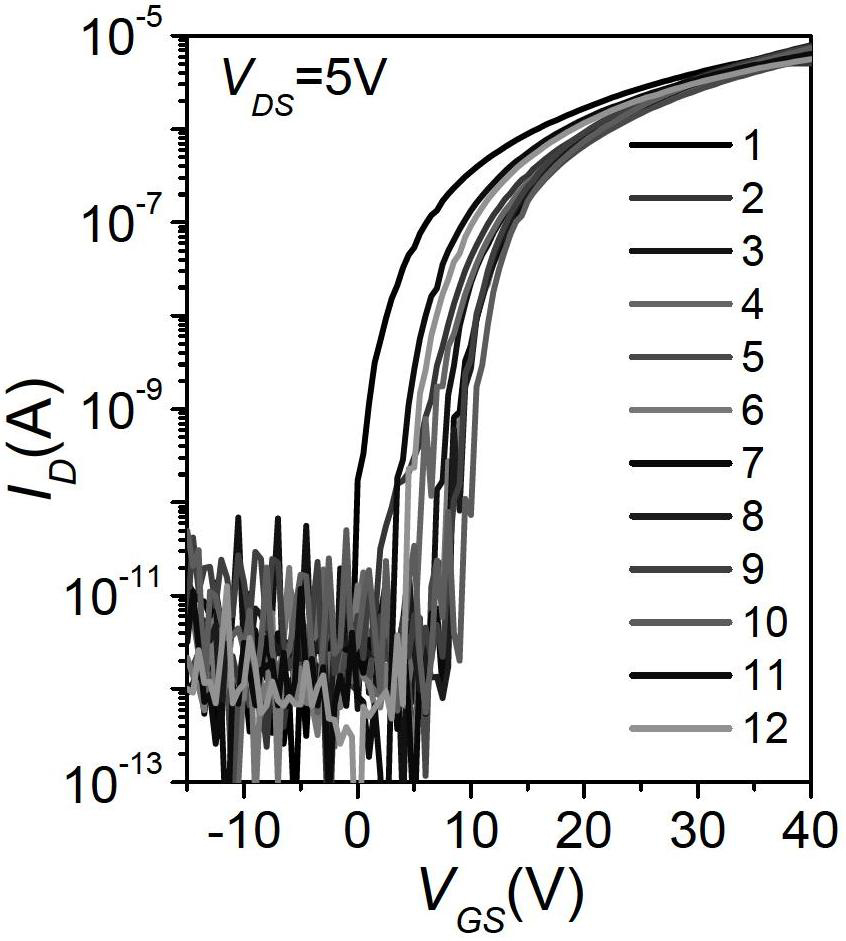

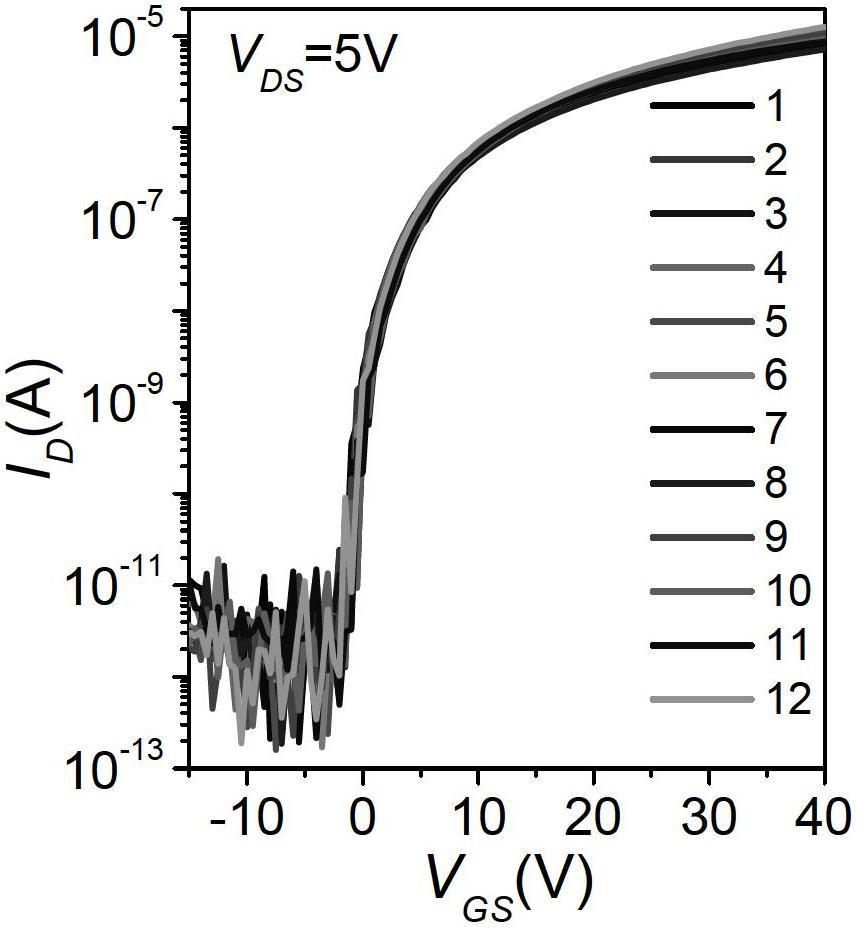

[0037] figure 2 and image 3 The performance uniformity of unpackaged metal oxide semiconductor thin f...

Embodiment 2

[0039]Adopt glass as insulating substrate 11, prepare gate electrode 12 on the upper surface of insulating substrate 11 by inkjet printing, the material of this gate electrode 12 is indium tin oxide; Gate insulating layer 13; Indium Gallium Zinc Oxide is prepared on the gate insulating layer 13 as a metal oxide active layer 14 by an inkjet printing process; metal Au is used to prepare the metal oxide active layer 14 by sputtering source electrode 15 and drain electrode 16; finally, polyvinylpyrrolidone is used to prepare the device protective layer 17 on the metal oxide active layer 14, source electrode 15 and drain electrode 16 by spin coating, annealing after film formation, and annealing The temperature does not exceed 150° C., thereby completing the packaging of the transistor.

Embodiment 3

[0041] Adopt plastic film as insulating substrate 11, prepare gate electrode 12 on the upper surface of insulating substrate 11 by photolithography, the material of this gate electrode 12 is poly 3,4-ethylenedioxythiophene / polystyrenesulfonic acid Salt; use metal oxide to prepare gate insulating layer 13 on both of them by spin coating; prepare indium gallium oxide as metal oxide active layer 14 on gate insulating layer 13 by sputtering process; use metal Ag Prepare the source electrode 15 and the drain electrode 16 on the metal oxide active layer 14 by photolithography; finally use polyvinyl alcohol to pass the pulling method on the metal oxide active layer 14, the source electrode 15 and the drain electrode 16 Method The device protective layer 17 is prepared, and annealing is performed after film formation, and the annealing temperature does not exceed 150° C., thereby completing the encapsulation of the transistor.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com