Preparation technique of SiGe Bi-CMOS appliance

A preparation process and device technology, applied in the field of process integration of germanium-silicon Bi-CMOS devices, can solve problems such as large-area exposure, device characteristic changes, development, etc., to reduce process defects, simplify process flow, improve yield and reliability. sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

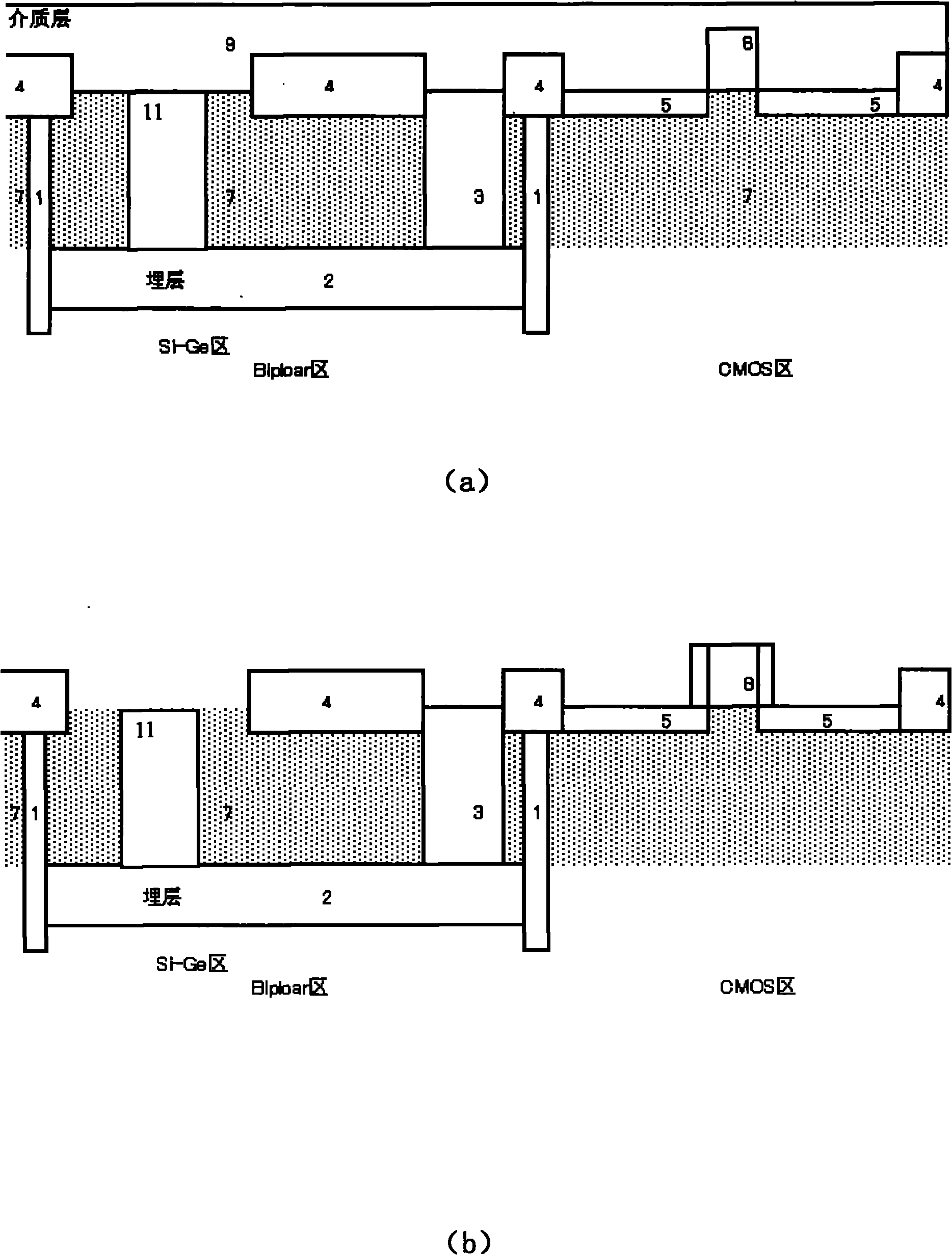

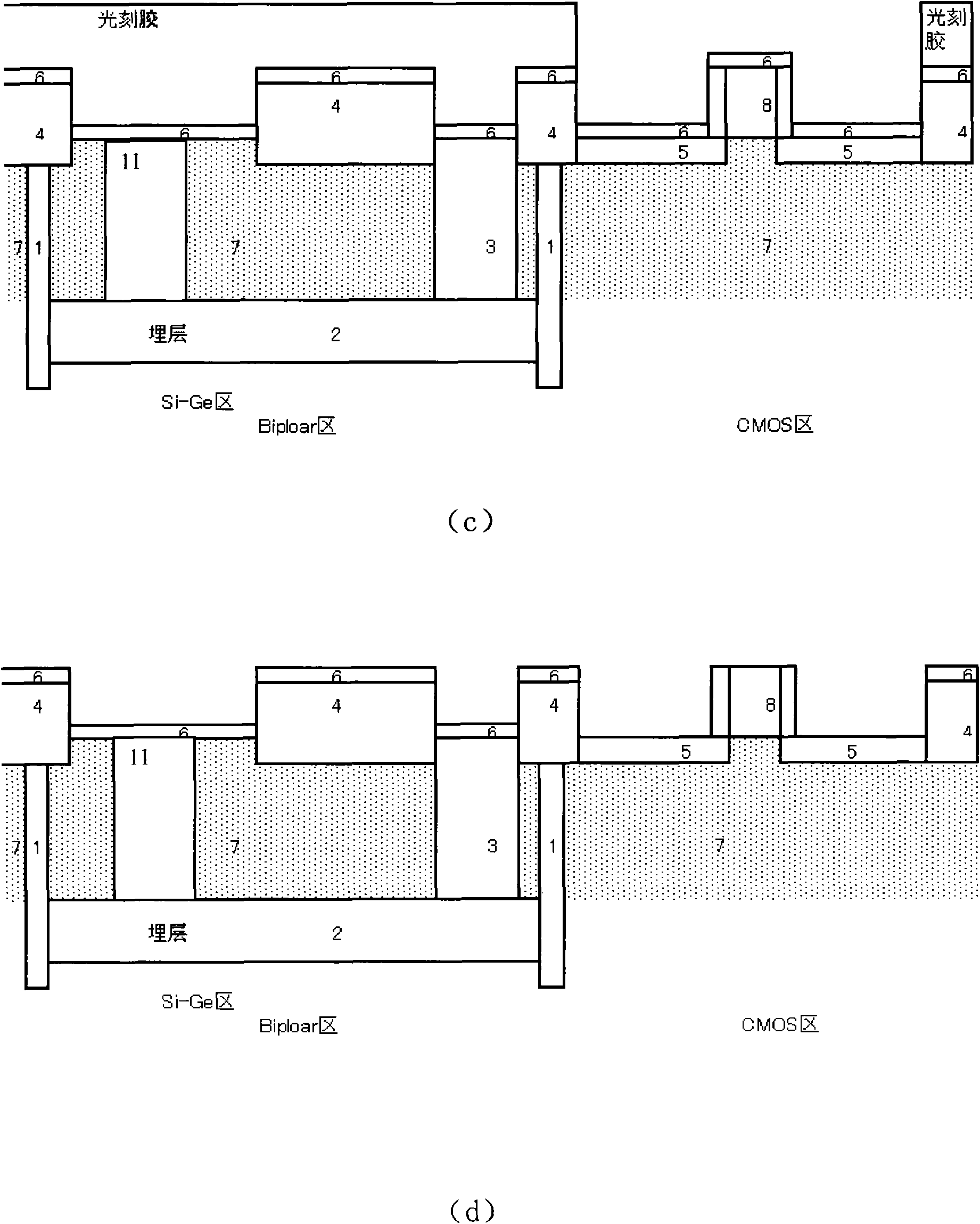

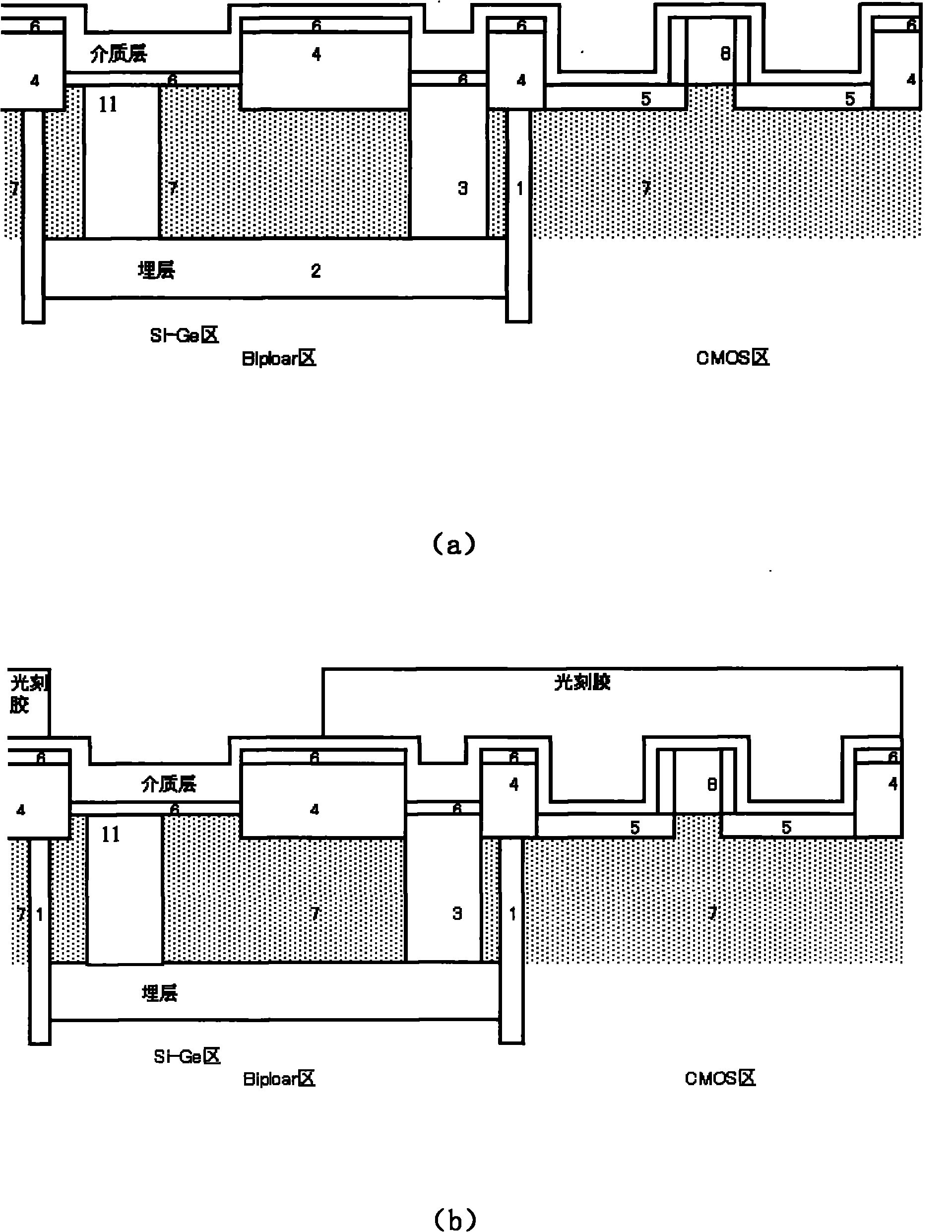

[0028] Such as Figure 4 As shown, the silicon germanium Bi-CMOS device preparation process of the present invention comprises the following steps when forming the sidewall and the metal silicide barrier layer of the silicon germanium Bi-CMOS device:

[0029] Firstly, the substrate and the doped region of a conventional SiGe device are formed on a silicon substrate, including the buried layer 2 in the SiGe bipolar region, and the deep trench isolation 1 separates the epitaxial layer 7, including the collector electrode 11 of the device, The collector lead-out region 3 , the shallow trench isolation 4 , and the gate 8 of the CMOS device, or in some cases, LDD and source-drain implantation can be completed first to form the source-drain region 5 .

[0030] Such as image 3 As shown in (a), a dielectric film layer is deposited over the entire silicon germanium device and CMOS device, and the dielectric film can be an oxide (such as SiO 2 ) or nitrides (such as SiN), there are a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com