Boiling enhanced heat exchange structure of chips and fabrication method thereof

A technology that enhances heat transfer and manufacturing methods. It is applied in semiconductor/solid-state device manufacturing, electrical components, and electrical solid-state devices. It can solve problems such as high superheat, not obvious improvement effect, and thermal shock of chips, so as to overcome critical heat flow. The effect that the density improvement effect is not obvious

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

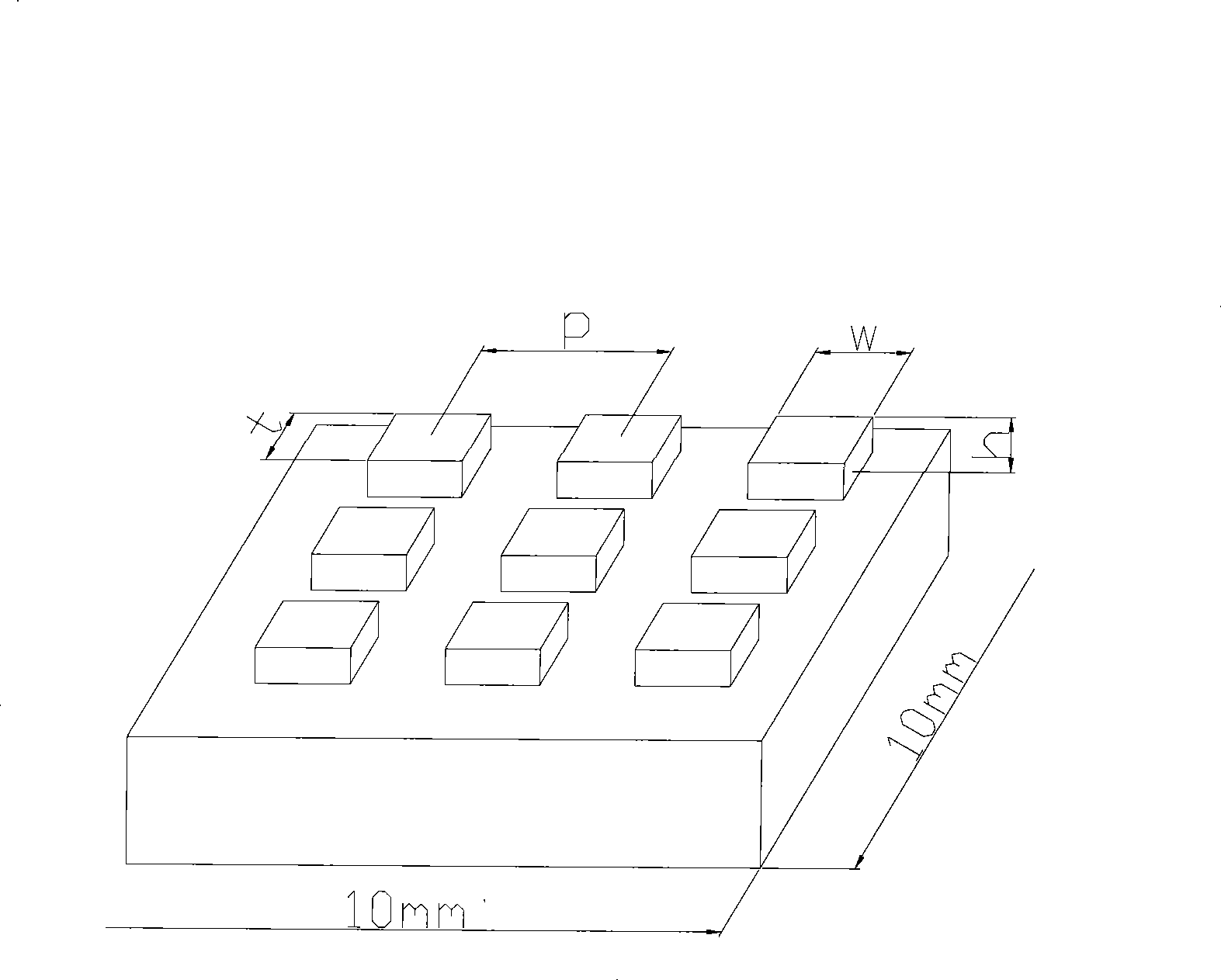

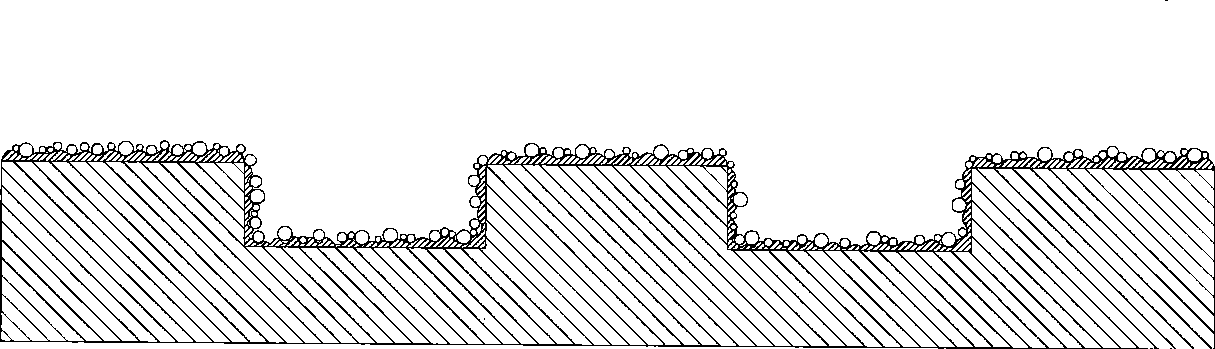

[0032] The manufacturing method of the boiling enhanced heat transfer structure of the chip of the present invention, the boss is a square columnar structure, the size is 50 μm×50 μm×60 μm (w×t×h), and the center pitch p is 100 μm. The specific manufacturing steps are as follows:

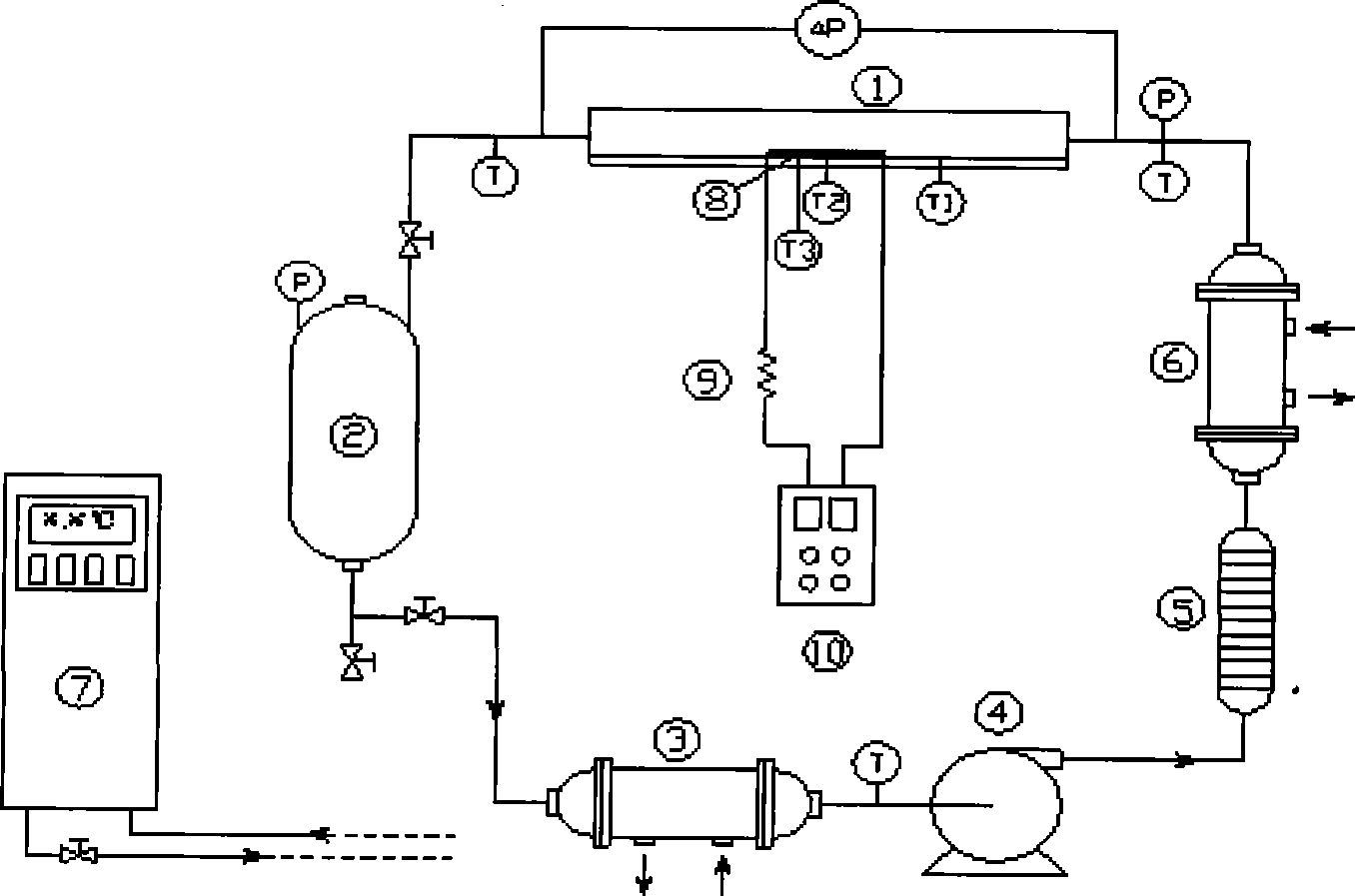

[0033] Step 1: Using a dry etching process, process bosses with columnar structures with the same size and uniform spacing on the surface of the chip. Specifically, a silicon wafer with a size of 10mm×10mm is cut from phosphorus-doped N-type semiconductor single crystal silicon with a thickness of 0.5mm and a diameter of 150mm as chips. Apply photoresist on the surface of the chip to form a photoresist film; make a mask whose size is consistent with the boss structure; then, use exposure technology to photoetch the photoresist film to form a pattern corresponding to the size of the boss photoresist pattern; finally, using dry etch gas Cl 2 Etching is performed until the boss height is 60 μm. Corro...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Height | aaaaa | aaaaa |

| Diameter | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com