Silicon chip etching method

A silicon wafer and etching technology, which is used in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problem of rough surface of the sidewall of the etching groove, difficult to guarantee the characteristic structure of etching, and ineffectiveness of the sidewall of the etching groove. Ground protection and other issues, to achieve the effect of smooth sidewalls, smooth edges, and obvious structural features

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

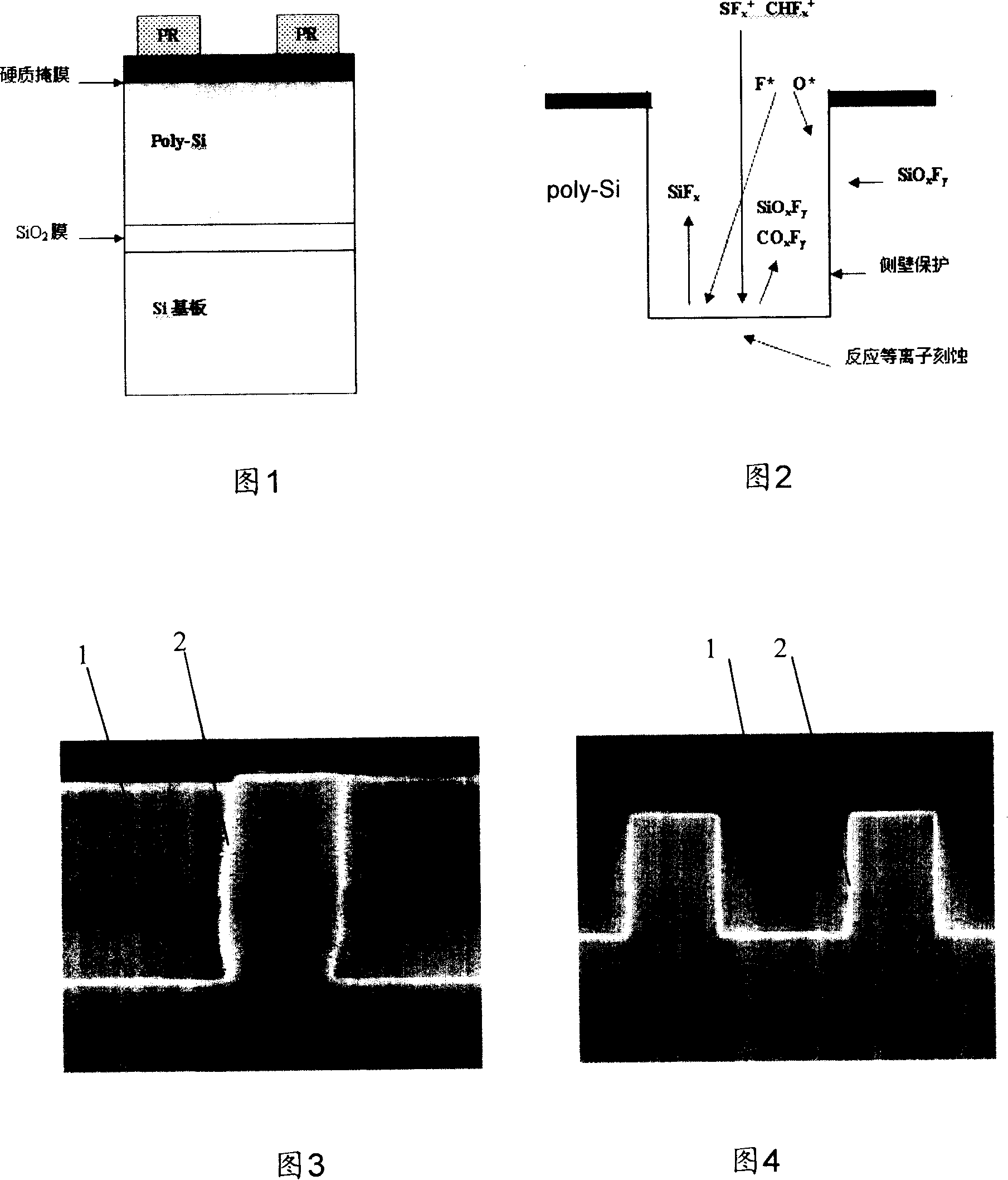

[0029] The present invention is mainly used to etch a silicon wafer, and its preferred embodiment includes three steps of initial etching, main etching, and over etching, wherein the purpose of the initial etching step is to remove the hard mask above the silicon wafer layer. film layer or other dielectric layers, the main etching step realizes the etching of the silicon wafer, and the purpose of the over etching step is to further etch the silicon wafer layer to achieve a thorough etching of the silicon wafer layer.

[0030] Taking etching polysilicon as an example below, the implementation process of the present invention is specifically described:

[0031] Polysilicon is an important area in the multilayer structure of integrated circuits, and its patterned etching quality will have a direct impact on the subsequent process flow.

[0032] As shown in Figure 1, MOSFET (metal-oxide semiconductor field effect transistor) is a representative insulated gate field effect transist...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com