Single electron memory having carbon nano tube structure and process for making it

A carbon nanotube and memory technology, applied in the field of single-electron memory, can solve problems such as limited integration, low device integration, and affecting device stability, and achieve the effects of reducing preparation steps and avoiding doping processes

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

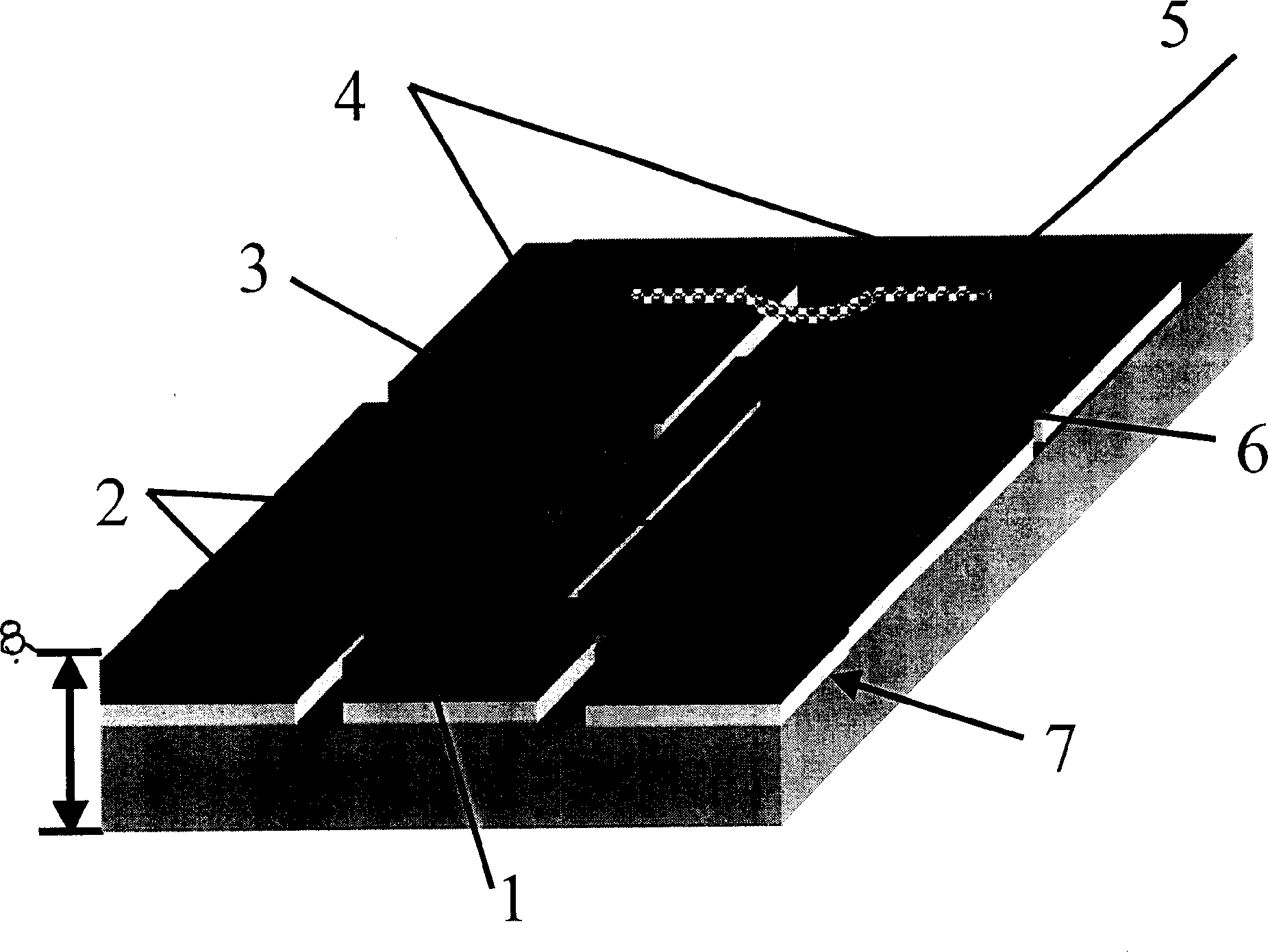

[0047] according to figure 1 A single-electron memory having a carbon nanotube structure of the present invention was fabricated.

[0048] Select silicon on insulator (SOI) material as the substrate, and use dry oxygen oxidation technology to oxidize and thin the single crystal silicon layer. The parameters are as follows: material crystal orientation , P type, resistivity 3Ωcm; silicon layer thickness is 40 nm, and the silicon dioxide layer is 50 nm thick. The single crystal silicon layer is heavily doped with arsenic to become an n-type semiconductor layer with a doping concentration of 6×10 13-2 .

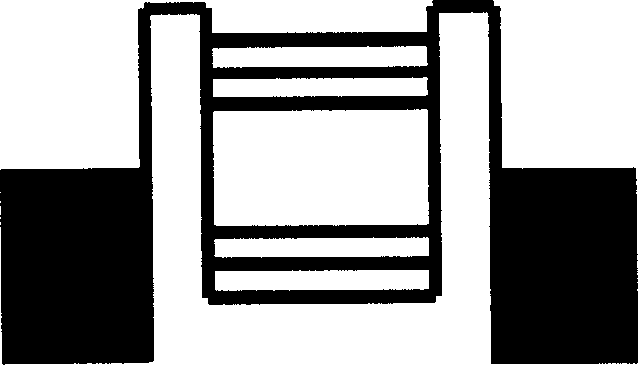

[0049] The nanowire structure and the carbon nanotube crystal structure are prepared in the silicon layer on the insulator by electron beam lithography method and dry etching technology. The length of the nanowire 3 is 100 nanometers, the width is 30 nanometers, and the height is 90 nanometers; the control gate 2 of each nanowire is 60 nanometers wide, 60 nanometers long, and...

Embodiment 2

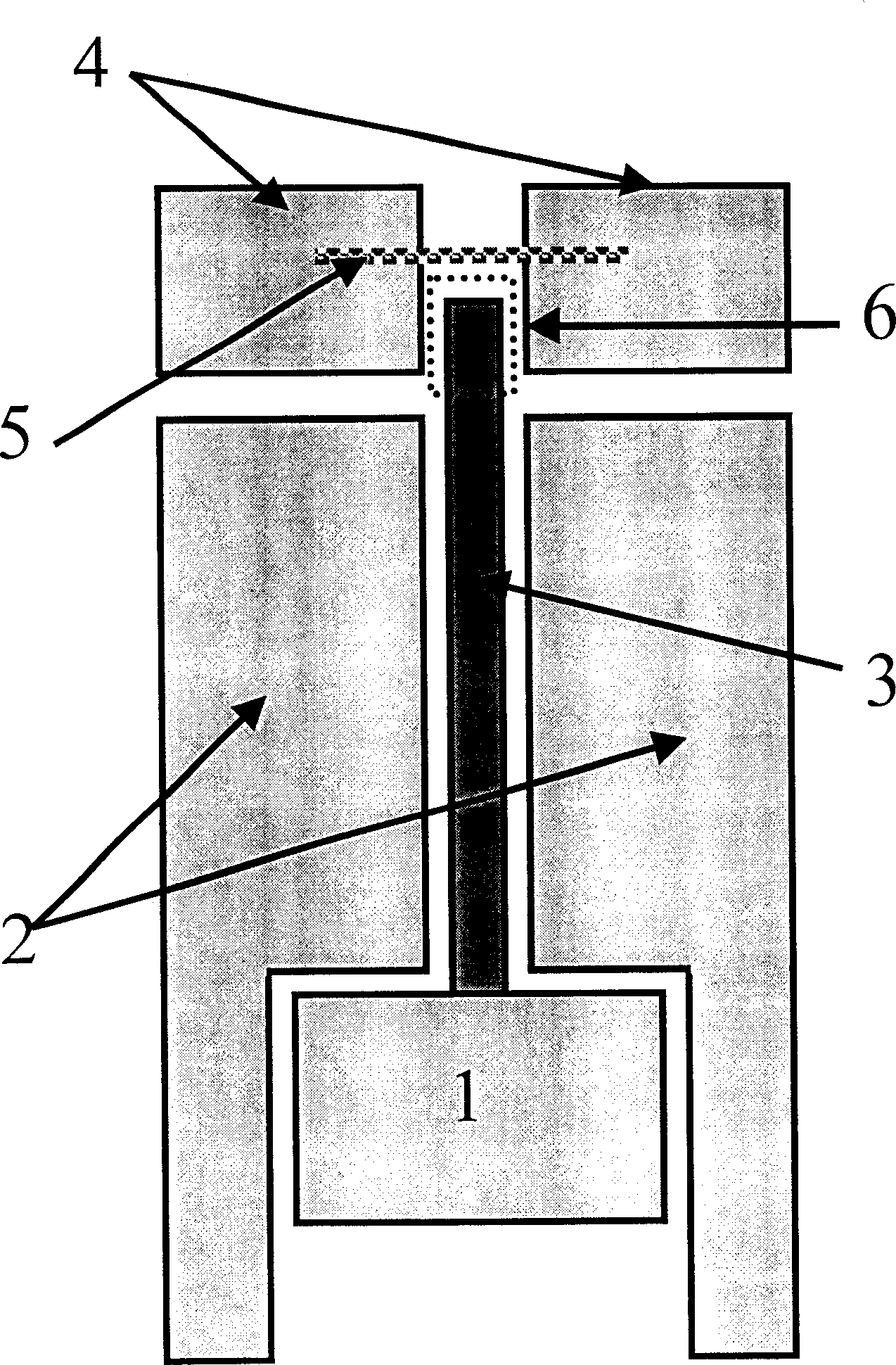

[0056] according to Figure 8 A single-electron memory having a carbon nanotube structure of the present invention was fabricated.

[0057]The preparation method of the nanowires is the same as that in Example 1, and the single-walled carbon nanotubes 5 are prepared and positioned using the in-situ growth technology of carbon nanotubes. Utilize the probe technology of atomic force microscope to place catalyst zone 9 on the inner side of gold electrode 4, grow carbon nanotube 5 in situ, and make the two ends of carbon nanotube have good electric contact with the electrode of carbon nanotube transistor; If growing Good contact is not achieved in the process, and the focused ion beam FIB technology can be used to achieve good contact between the carbon nanotube 5 and the electrode 4 of the carbon nanotube transistor. Finally, the device is packaged and wired.

Embodiment 3

[0059] On the single-electron memory device prepared in Example 1 or 2, carbon nanotubes are used as leads on each electrode.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Length | aaaaa | aaaaa |

| Height | aaaaa | aaaaa |

| Resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com