Method for manufacturing silicon high-speed semiconductor switch device

A technology of switching devices and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as increased leakage current, poor reverse blocking characteristics, and decreased breakdown voltage, so as to improve switching speed , excellent electrical performance, and the effect of improving the softness factor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

[0041] Example 1 Fast recovery pin diode manufacturing method:

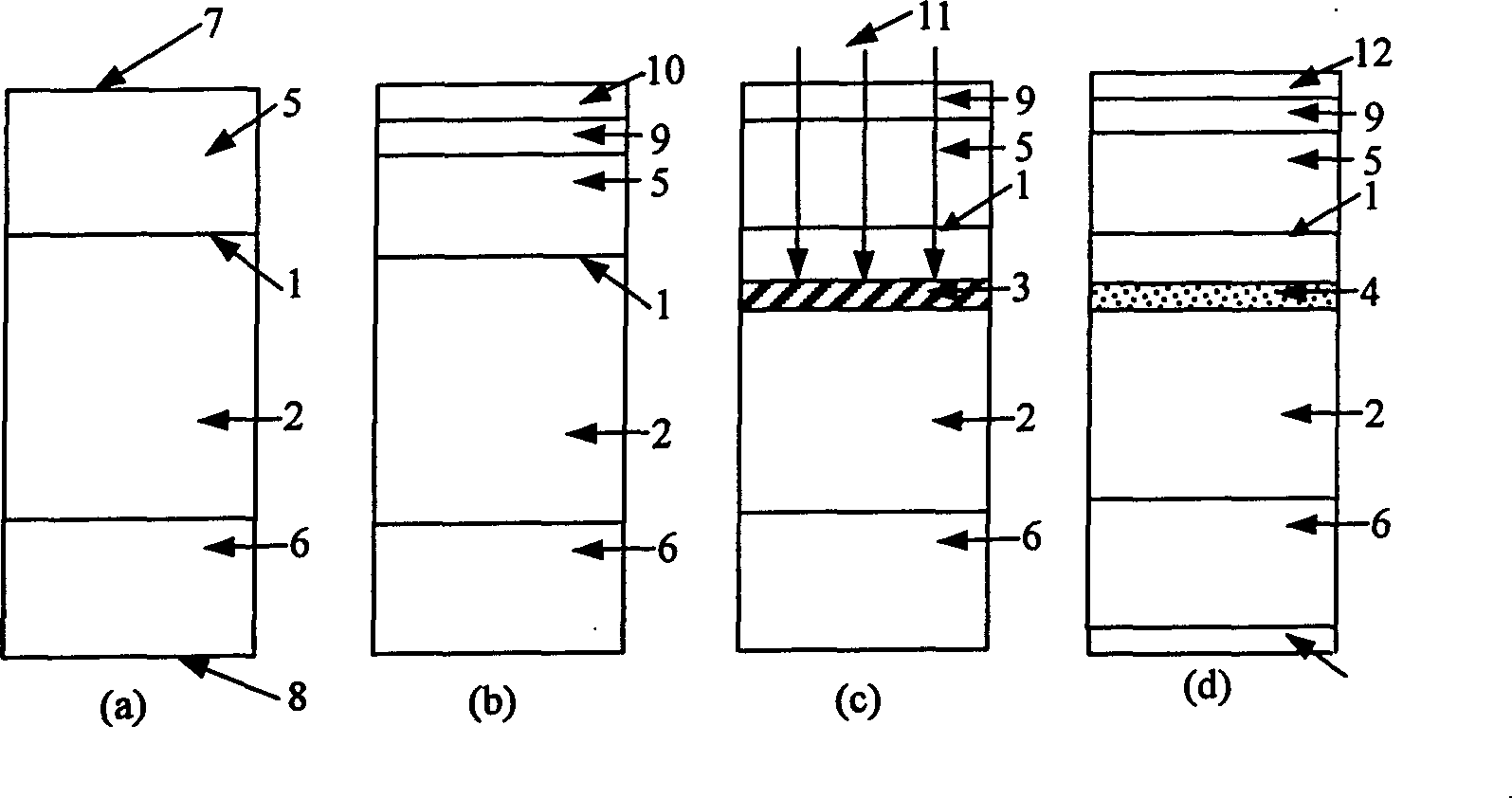

[0042] The step that the present invention manufactures pin fast recovery diode is, refer to attached figure 2 : (1) each p-type doping and n-type doping regions of the pin diode are produced by conventional methods, including a pn junction 1, a high-resistivity n-type base region 2, a low-resistivity p-type anode region 5, and a low-resistance n-type Cathode region 6, upper surface 7 and lower surface 8, see attached figure 2 (a). For epitaxial fast recovery diodes, the conventional method here is to epitaxially high-resistance n-type layer on a low-resistance n-type silicon substrate, and then diffuse p-type impurities from the surface into the high-resistance n-type layer; for double-diffused fast recovery diodes here The conventional method is to diffuse high-concentration n-type impurities and p-type impurities on both sides of the high-resistance n-type substrate; (2) remove the silicon dioxide on the s...

example 2

[0043] Example 2 Manufacturing method of high-speed insulated gate bipolar transistor (IGBT):

[0044] The step that the present invention manufactures high-speed IGBT is, referring to the attached image 3 : (1) The basic structures such as each p-type region and n-type region of the IGBT are manufactured by conventional methods, see the attached image 3 (a), it includes the p-type drain region 15 of low resistivity, the n-type base region 2 of high resistivity, the n-type buffer layer 14 of medium resistivity, pn junction 1, the p-type well region 16 of medium resistivity, low n-type source region 17 of resistivity, polysilicon gate electrode 18, gate oxide layer 19 etc.; Deposit a layer of platinum film with a thickness of about 0.1 to 0.2 microns; (3) place the silicon wafer in a heating furnace at a temperature of about 465° C. and keep it warm for about 40 minutes, so far a platinum-silicon alloy layer 9 is formed at the interface between platinum and silicon, leaving...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com