Preparation method of nano-pillar array

A nano-pillar array, semiconductor technology, applied in nanotechnology, semiconductor/solid-state device manufacturing, electrical components and other directions, can solve the problems of low cost, difficulty and other problems, and achieve good sidewall morphology, high efficiency and high yield. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Below in conjunction with each accompanying drawing, the present invention is described in detail.

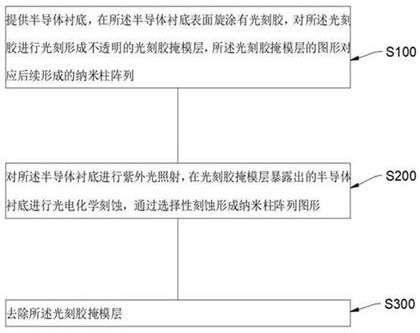

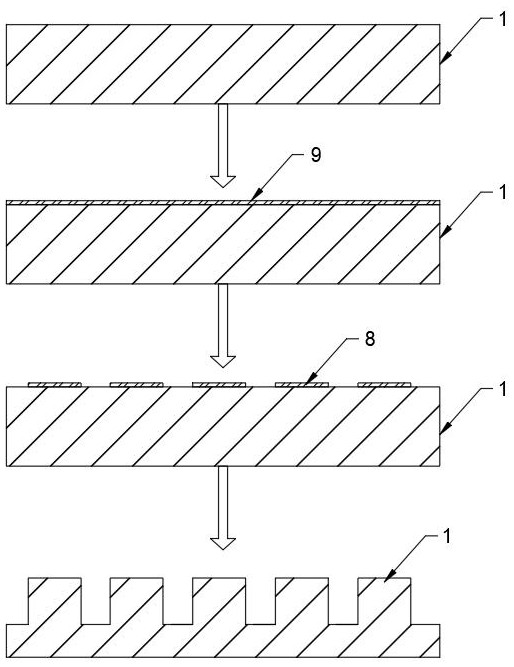

[0033] Such as figure 1 and figure 2 As shown, the embodiment of the present invention provides a method for preparing a nanopillar array, including:

[0034] In step S100, a semiconductor substrate is provided, and a photoresist is spin-coated on the surface of the semiconductor substrate, and photolithography is performed on the photoresist to form an opaque photoresist mask layer. The pattern of the photoresist mask layer corresponds to Subsequent formation of nanopillar arrays.

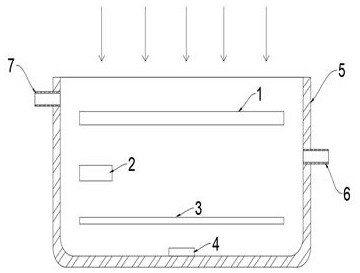

[0035] Step S200, irradiating the semiconductor substrate with ultraviolet light, performing photoelectrochemical etching on the semiconductor substrate exposed by the photoresist mask layer, and forming nano-column array patterns by selective etching.

[0036] Step S300, removing the photoresist mask layer.

[0037] Specifically, step S100 is executed to provide a semiconductor substra...

PUM

| Property | Measurement | Unit |

|---|---|---|

| wavelength | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com