Semiconductor high-density lead frame and its manufacturing process

A lead frame and manufacturing process technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of low lithography pattern accuracy, easy appearance of burrs, and inconvenient lead frame processing and manufacturing.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

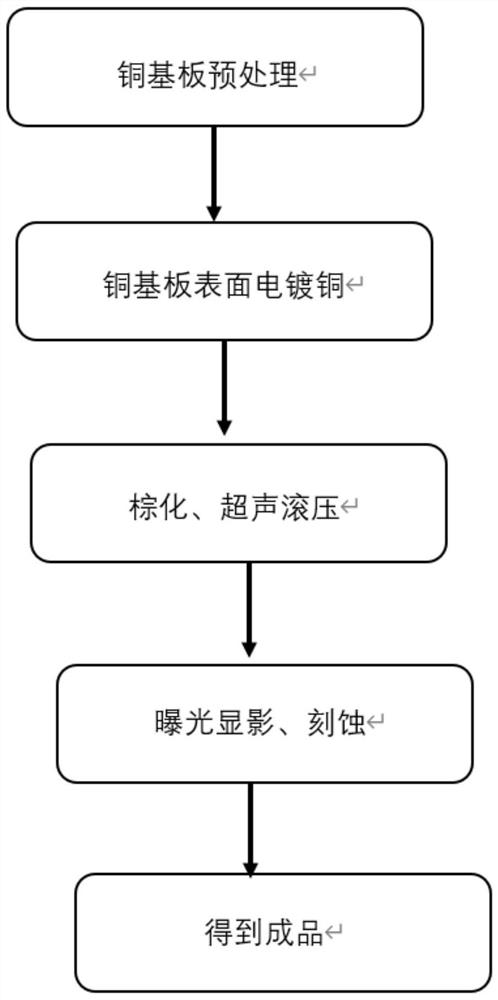

Method used

Image

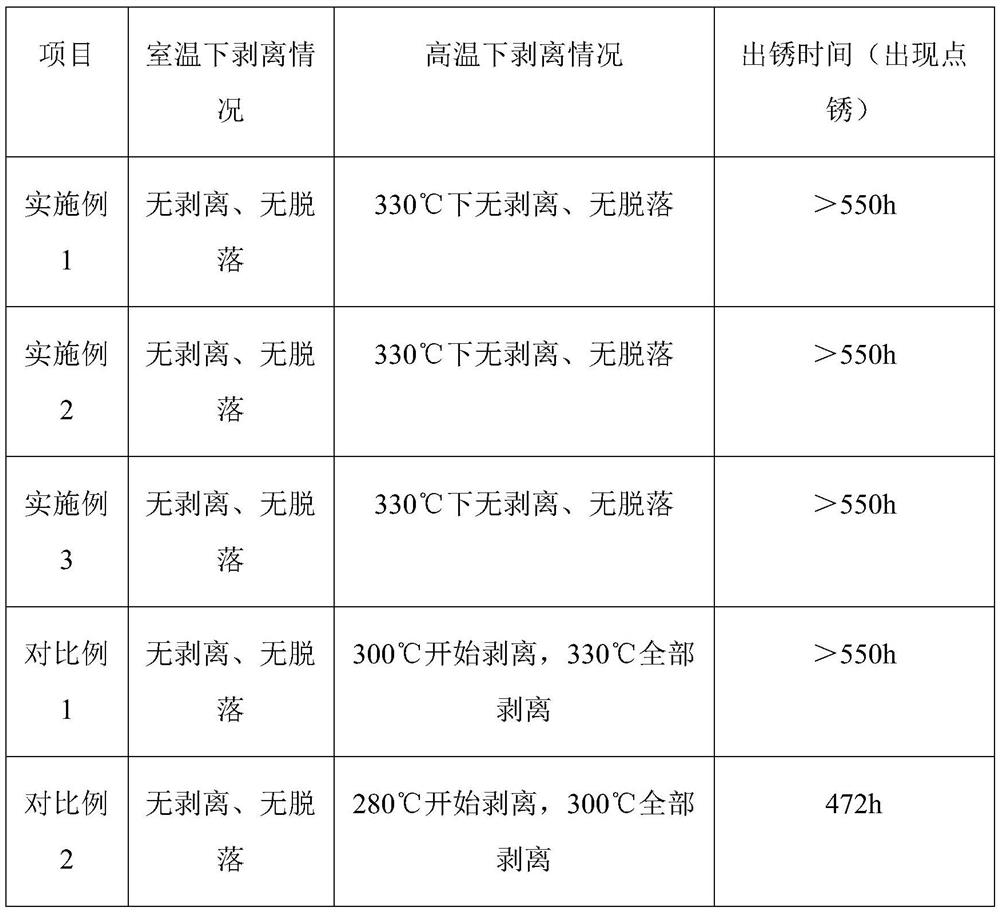

Examples

Embodiment 1

[0042] A manufacturing process for a semiconductor high-density lead frame, comprising the following steps:

[0043] (1) Take the copper substrate, wash it with deionized water for 3 minutes, then place it in the electrolyte for cathodic electrolytic degreasing, rinse it with deionized water, then soak it in nitric acid solution for 20s, remove the surface oxide film, rinse it with deionized water, and place it Activated in the activation solution for 3 minutes, rinsed with deionized water to obtain a pretreated copper substrate; the electrolyte is a mixture of trisodium phosphate, sodium hydroxide, sodium silicate and sodium carbonate, the temperature during electrolytic degreasing is 50°C, and the current The density is 10A / dm 2 , The electrolytic oil removal time is 20s.

[0044] (2) Take the pretreated copper substrate, place it in the electroplating solution, and electroplate a pure copper layer on the surface of the pretreated copper substrate, the electroplating temper...

Embodiment 2

[0051] A manufacturing process for a semiconductor high-density lead frame, comprising the following steps:

[0052] (1) Take the copper substrate, wash it with deionized water for 4 minutes, then place it in the electrolyte for cathodic electrolytic degreasing, rinse it with deionized water, and then soak it in nitric acid solution for 25s to remove the surface oxide film, rinse it with deionized water and place it Activated in the activation solution for 4 minutes, rinsed with deionized water, and obtained the pretreated copper substrate; the electrolyte was a mixture of trisodium phosphate, sodium hydroxide, sodium silicate and sodium carbonate, and the temperature during electrolytic degreasing was 52°C, and the current The density is 11A / dm 2 , The electrolytic oil removal time is 23s.

[0053] (2) Take the pretreated copper substrate, place it in the electroplating solution, and electroplate a pure copper layer on the surface of the pretreated copper substrate, the elec...

Embodiment 3

[0060] A manufacturing process for a semiconductor high-density lead frame, comprising the following steps:

[0061] (1) Take the copper substrate, wash it with deionized water for 5 minutes, then place it in the electrolyte for cathodic electrolytic degreasing, rinse it with deionized water, and then soak it in nitric acid solution for 30s to remove the surface oxide film, rinse it with deionized water and place it Activated in the activation solution for 5 minutes, rinsed with deionized water to obtain a pretreated copper substrate; the electrolyte is a mixture of trisodium phosphate, sodium hydroxide, sodium silicate, and sodium carbonate, and the temperature during electrolytic degreasing is 55°C. The density is 12A / dm 2 , The electrolytic oil removal time is 25s.

[0062] (2) Take the pretreated copper substrate, place it in the electroplating solution, and electroplate a pure copper layer on the surface of the pretreated copper substrate, the electroplating temperature ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com