Preparation method of enhanced CMOS sensor light emitting diode unit structure

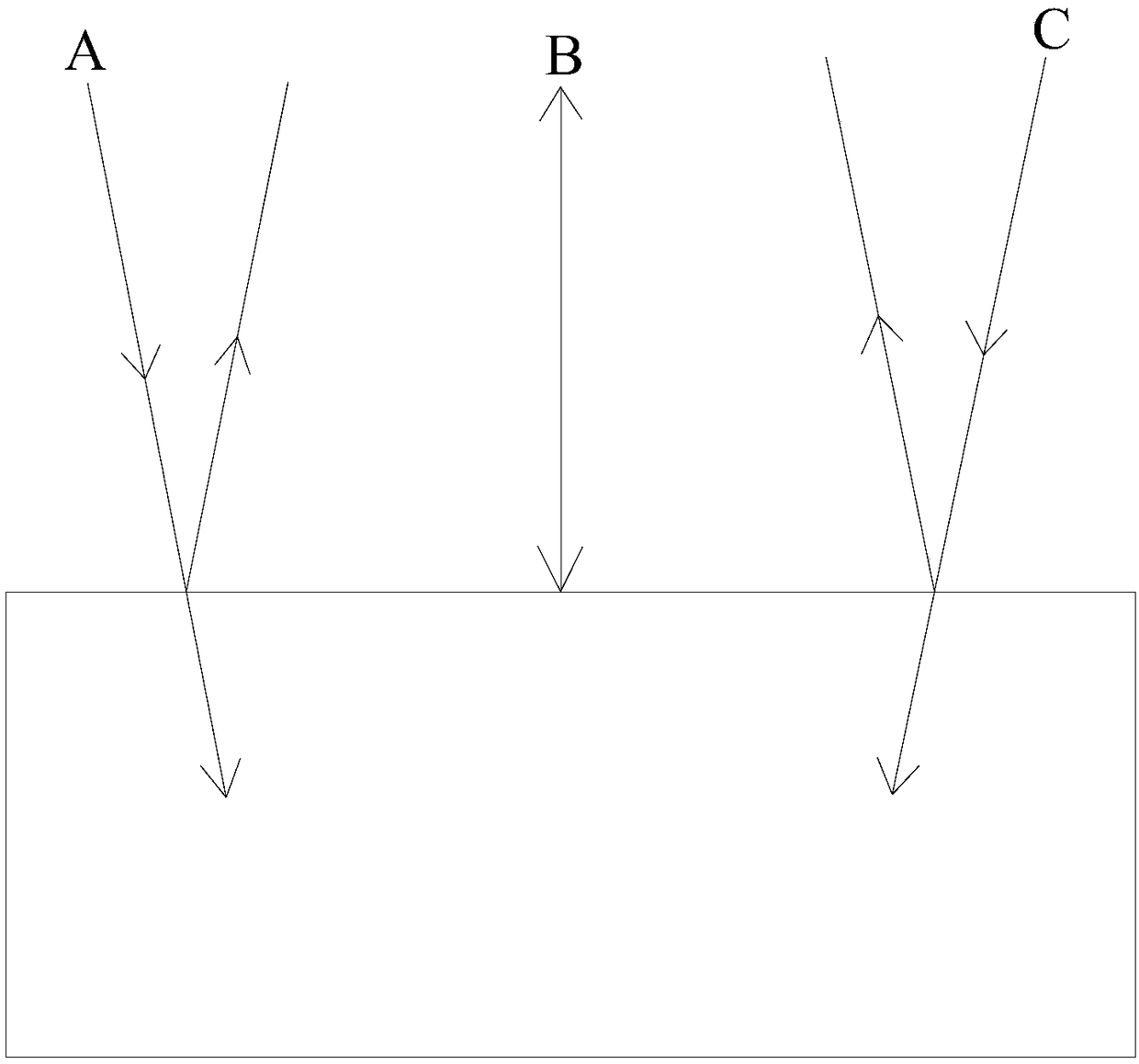

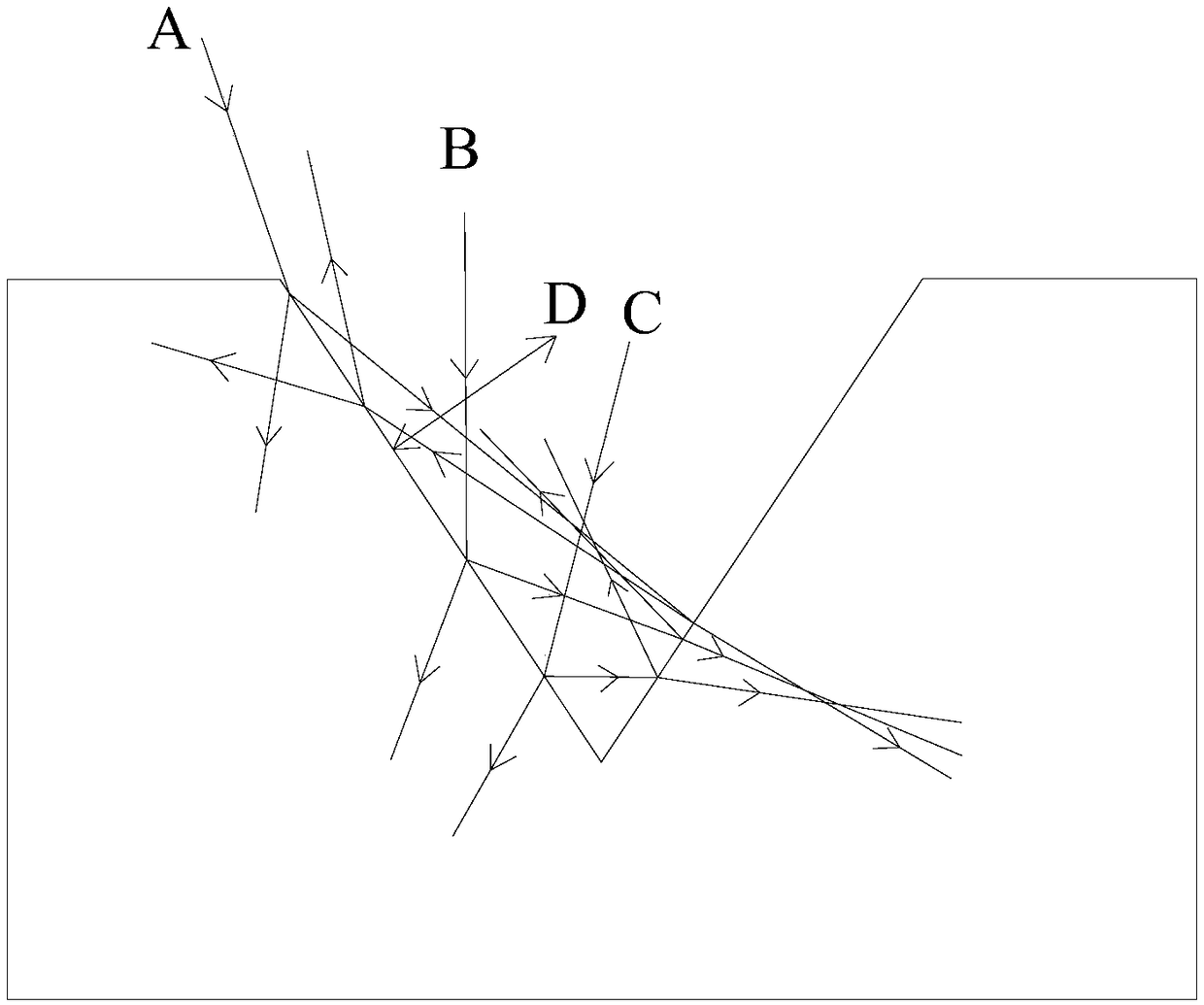

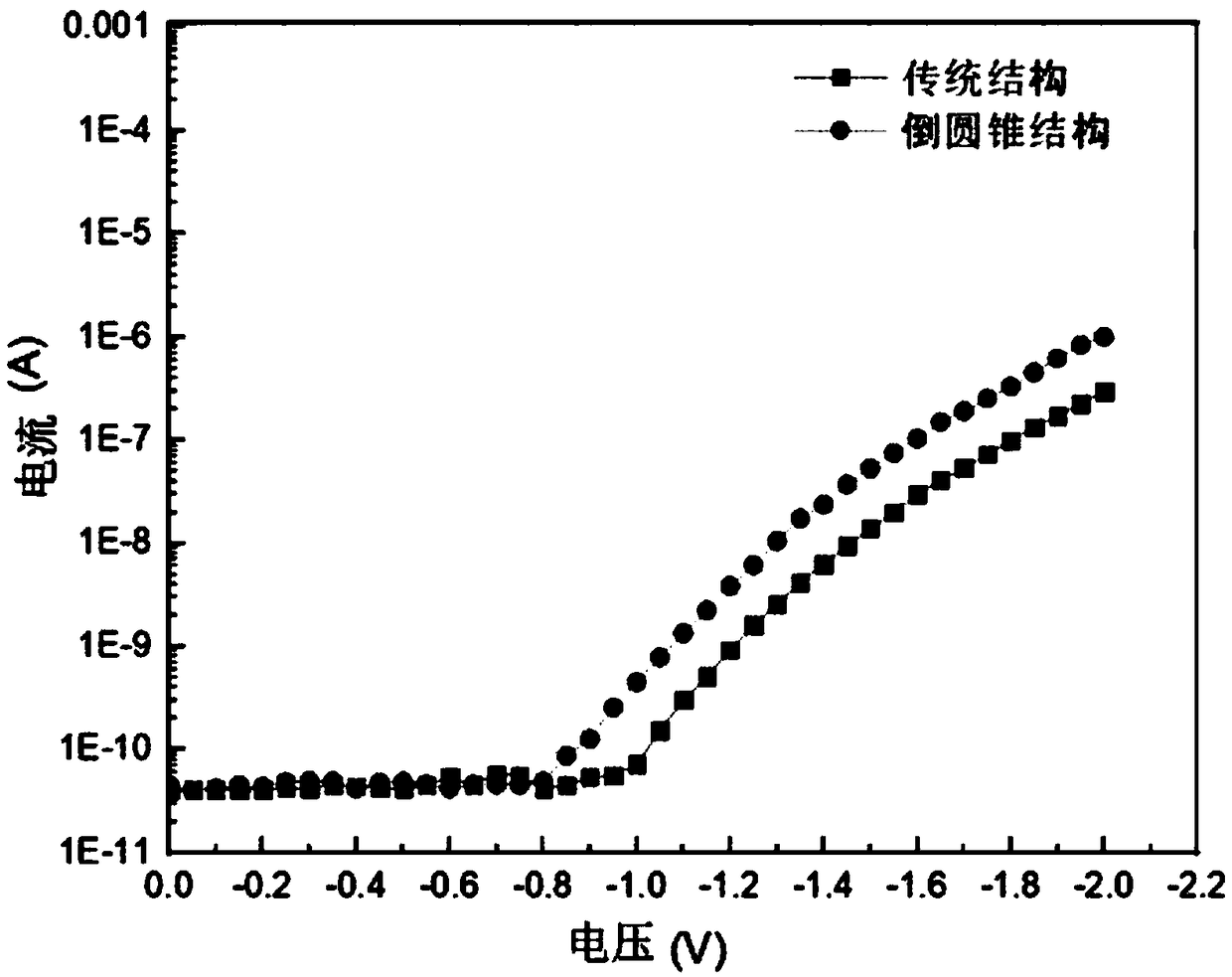

A CMOS sensor and light-emitting diode technology, applied in the direction of electrical components, semiconductor devices, circuits, etc., can solve the problem of unsuitable high-quality and uniform 2D imaging functions, the strict manufacturing of embedded chamfered Si structures, and large deviations in pixel characteristics etc. to achieve the effect of reducing edge scattering, reducing diffraction, and increasing signal-to-noise ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0066] Embodiments of the present invention will now be described with reference to the drawings, in which like reference numerals represent like elements.

[0067] Please refer to Figure 2-19 , the preparation method of the enhanced CMOS sensor light-emitting diode unit structure, the steps include:

[0068] (1) Utilize the RCA cleaning method, rely on SC-1 cleaning solution, SC-2 cleaning solution, SC-3 cleaning solution, acid and deionized water to clean the P-type wafer 1, and peel off the P-type wafer 1 upper surface oxide layer. The P-type wafer material is silicon, and the thickness of the P-type wafer material is 700um. SC-1 cleaning solution is NH 4 OH / H 2 o 2 / H 2 O, SC-2 cleaning solution is HCI / H 2 o 2 / H 2 O, SC-3 cleaning solution is H 2 SO 4 / H 2 o 2 / H 2 O, the acid is HF. In the cleaning procedure, first remove the organic contamination on the surface of the silicon wafer, because organic matter will cover part of the surface of the silicon waf...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com