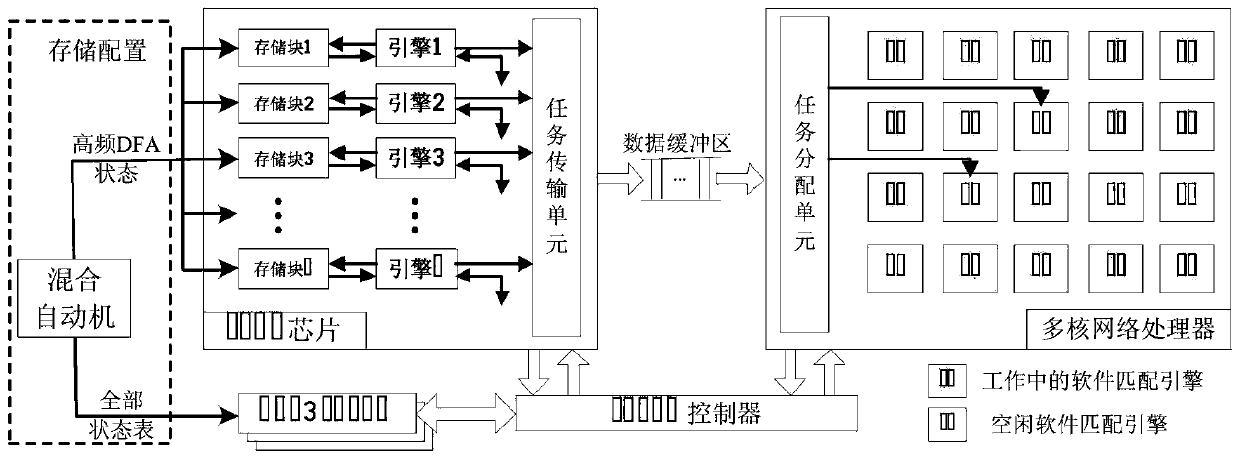

High-speed regular expression matching hybrid system and method based on FPGA+NPU

A technology of expression matching and hybrid system, which is applied in the field of deep message inspection, can solve the problems of large-scale DFA, complex rules, and the inability of the platform to provide satisfactory solutions, and achieve the effect of solving matching performance problems and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

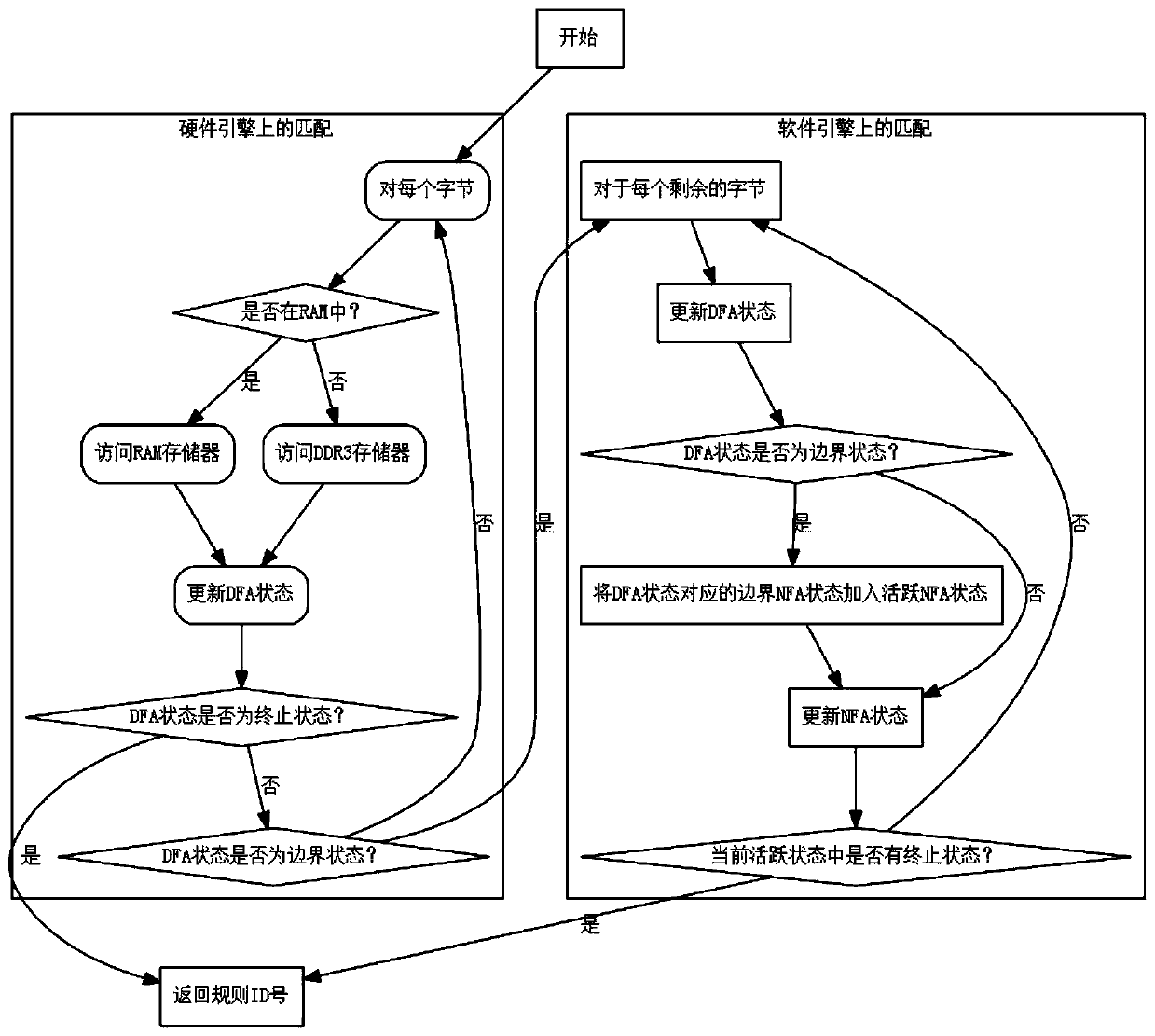

[0071] The first step is to compile the rule set and generate the automaton

[0072] 1.1 Use the regular expression compilation algorithm proposed by KEN THOMPSON in the paper "Regular Expression Search Algorithm (Regular Expression Search Algorithm)" published in the 11th volume of Computer Communications (Communications of the ACM) in June 1968 to convert the regular expression pattern set compiled into an NFA.

[0073] 1.2 Use the algorithm proposed by Micheal Becchi in the paper "A hybrid finite automaton for practical deep packet inspection" in the 2007 ACM CoNEXT conference to compile NFA into a hybrid automaton hybrid-FA . The data structure of Hybrid-FA mainly includes the corresponding relationship between DFA, NFA and boundary DFA state and NFA state. Among them, DFA is a two-dimensional array, the array row represents the DFA state identification, the array column corresponds to the input of 256 ASCII characters, and the array element represents the next state to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com