Passivating method for front side and side walls of discrete device chip

A discrete device and chip technology, which is used in the passivation of chips, front and sidewall passivation of discrete device chips, can solve the problems of high manufacturing cost and long manufacturing cycle, and achieve short manufacturing cycle, good sidewall protection and performance. Excellent and reliable results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0029] Such as Figure 1 to Figure 7 As shown, the present embodiment provides a method for passivating the front and side walls of a discrete device chip, and the passivation method includes the steps of:

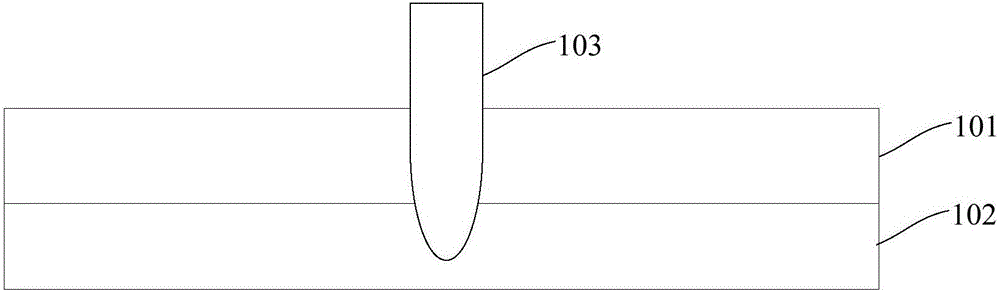

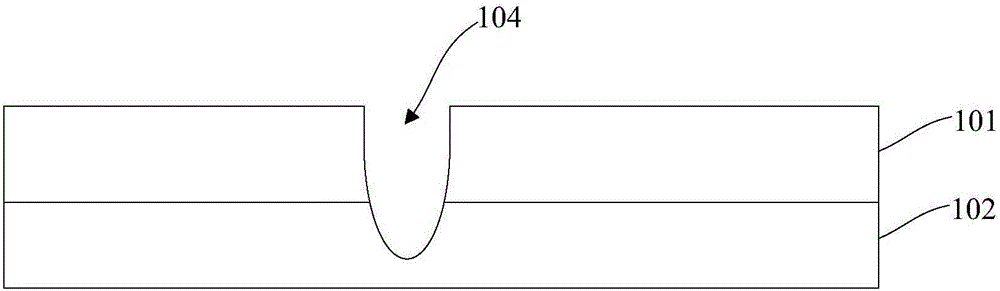

[0030] Such as Figure 1 ~ Figure 2 As shown, step 1) is first performed, providing a chip wafer 101 , and cutting the chip wafer 101 to form a plurality of dicing lines 104 .

[0031] As an example, the discrete device includes a Schottky barrier diode, that is, the chip wafer 101 is a wafer including a plurality of Schottky barrier diode chips.

[0032] As an example, before dicing, a step is further included: bonding the back of the chip wafer 101 to an adhesive layer 102 , specifically, the adhesive layer 102 can be selected as a blue film, a bandage, or the like.

[0033] As an example, a dicing knife 103 is used to mechanically cut the chip wafer 101 to form a plurality of dicing lines 104 . The dicing line 104 can completely pass through the chip wafer 101 or leav...

Embodiment 2

[0044] This embodiment provides a method for passivating the front and side walls of a discrete device chip, the basic steps of which are as in Embodiment 1, the difference from Embodiment 1 is that the screen 105 is to be passivated on the front of the chip wafer 101 There are openings 106 at the position of the layer, step 3) attaching a passivation material 107 at the position where the passivation layer is to be prepared.

[0045] Visible, discrete device chip front and sidewall passivation method of the present invention is not only applicable to the sidewall passivation layer making of chip, and is also applicable to the passivation layer making of chip front or other positions, simplifies the chip front passivation layer production. production process. The invention has a wider scope of application and has wider application prospects in the field of semiconductor manufacturing.

[0046] As mentioned above, the method for passivating the front and side walls of the disc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com