A hermetic structure for wafer-level packaging and its manufacturing method

A wafer-level packaging and manufacturing method technology, which is applied in the process, microstructure technology, microstructure device and other directions for producing decorative surface effects, can solve the problems of complex process and high cost, and achieves mature technology, reduced volume, The effect of reducing packaging costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

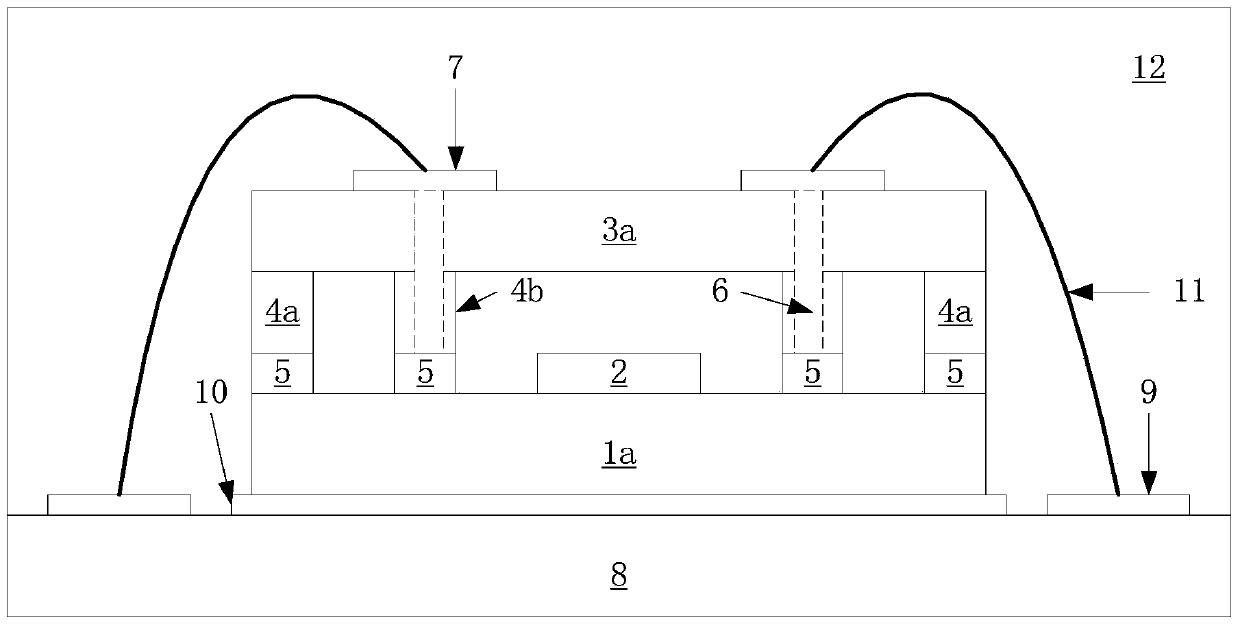

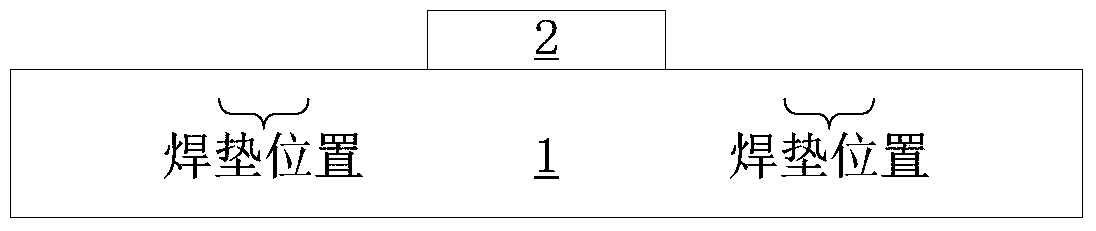

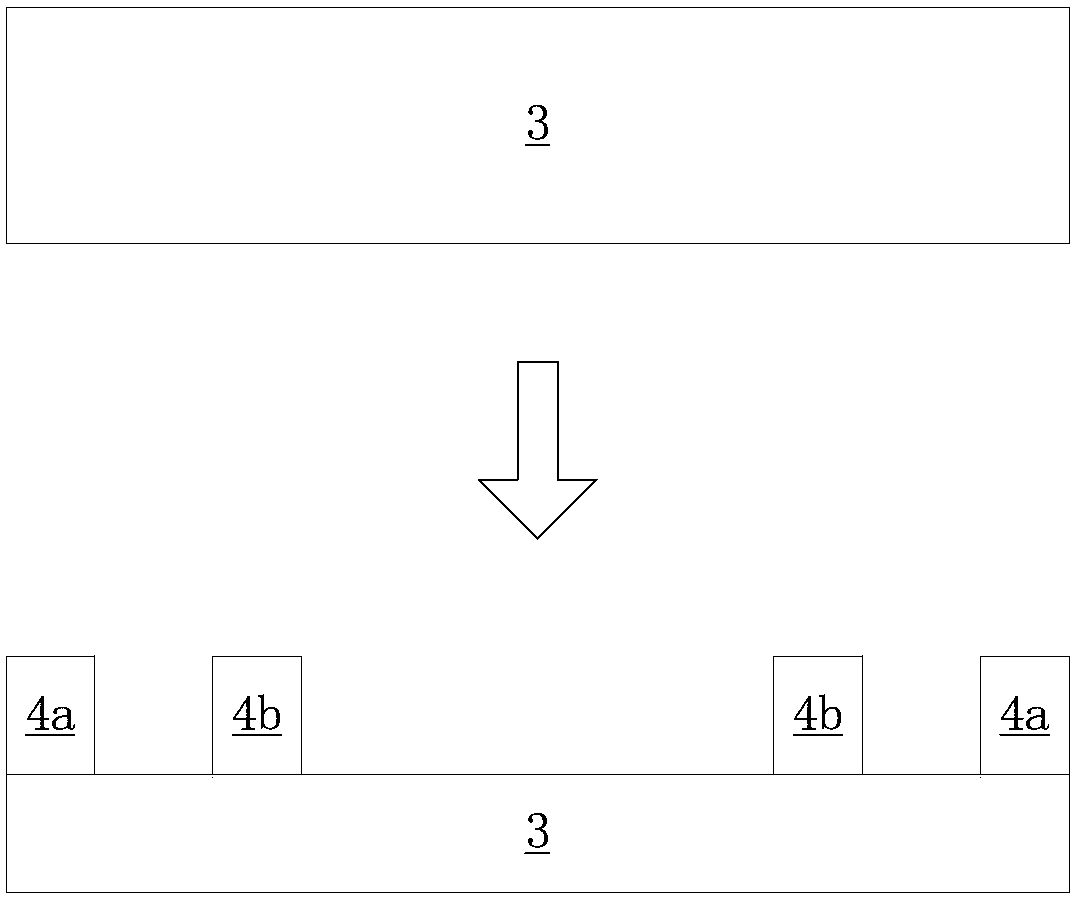

[0037] see figure 2 , which is Embodiment 1 of the airtight structure used for wafer-level packaging of semiconductor devices in this application. There are a plurality of semiconductor devices 2 on the base wafer 1, and the semiconductor devices 2 include MEMS devices and IC devices other than the MEMS devices. The periphery of each semiconductor device 2 is formed by a wall 13 to form an annular side wall, which in turn joins a roof 15 . The base chip unit 1a is obtained after the base wafer 1 is diced. The base chip unit 1a, the wall body 13 and the roof 15 constitute an airtight structure protecting each semiconductor device 2 . Wherein, the wall body 13 is made of photoresist material, and the roof 15 is made of photoresist or glass material, so it can be manufactured only by photolithography process and / or spin coating process. Preferably, the airtight structure is airtight, and the interior can be vacuum or filled with gas. The solder pads of each semiconductor dev...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com