Integrated micro-mechanical thermopile infrared detection system and method for producing the same

A thermopile detector and infrared detection technology, applied in the field of infrared detectors, can solve problems such as difficult mass production and large device size

- Summary

- Abstract

- Description

- Claims

- Application Information

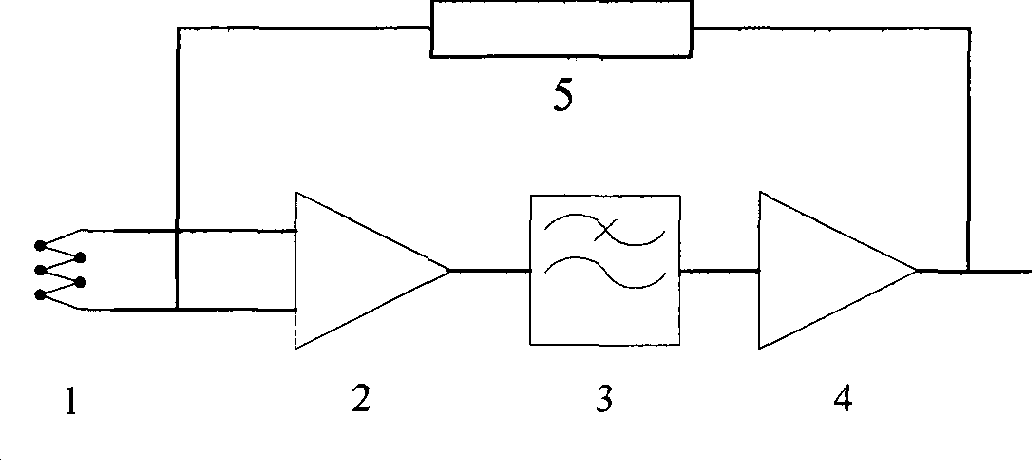

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

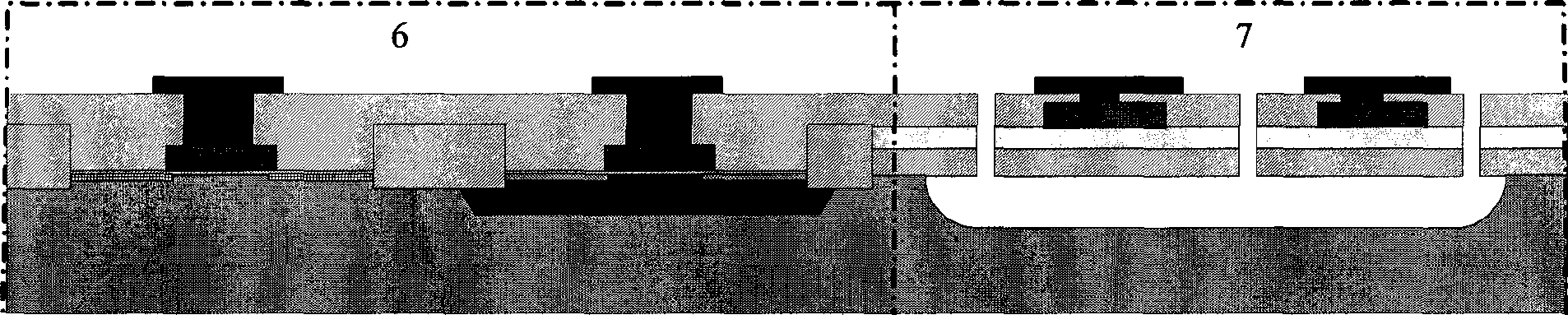

Embodiment 1

[0058] The main process steps include:

[0059] (1) Select a P+ silicon wafer (not shown in the figure) with a (100) crystal orientation as the substrate, with a resistivity of 10 Ω cm, and initially oxidize the P- epitaxial layer 14 to grow silicon oxide

[0060] (2) Lithograph the N well 16 on the P- epitaxial layer, ion implant phosphorus, and dose 2E12cm -2 , the energy is 60keV, the well region is advanced, and the junction depth is about 6.0μm.

[0061] (3) Growth of thermal silicon oxide LPCVD deposition thickness is of silicon nitride 17.

[0062] (4) Photoetching the active area of the CMOS circuit, etching silicon nitride and silicon oxide.

[0063] (5) Etch the silicon wafer and grow about The field oxide layer 18.

[0064] (6) Etching and removing silicon nitride and silicon oxide in the CMOS circuit area.

[0065] (7) The growth thickness of the active region is about The gate oxide layer 19.

[0066] (8) LPCVD deposits polysilicon 20 with a thickne...

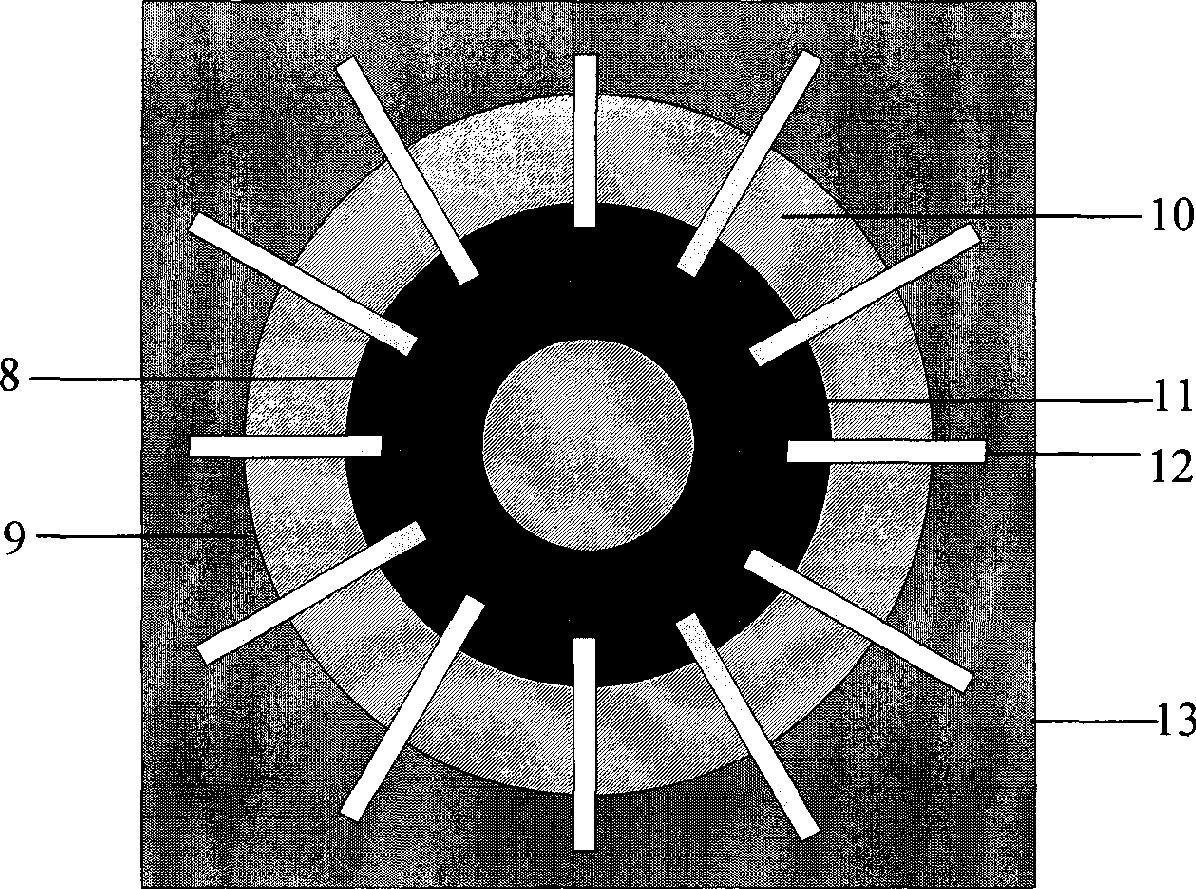

Embodiment 2

[0075] Its specific implementation steps are the same as in Example 1, the main difference is that the thermopile geometric configuration in Example 1 is modified to Figure 5 in the structure. The geometry of the thermocouple pair is not image 3 Shown are radial rather than parallel to the sides of the frame; etch openings are designed to be square rather than image 3 Circular shapes are shown, no special crystallographic orientations need to be considered.

Embodiment 3

[0077] The specific implementation steps are the same as those in Embodiment 1, the main difference being that the N-well CMOS process in Embodiment 1 is modified to a P-well or double-well CMOS process. Taking the P-well CMOS process as an example, the modified process steps are as follows: (a) Change the P+ silicon wafer in step (1) in Embodiment 1 to an N+ silicon wafer as the substrate. (b) Modify step (2) in Example 1 to "photolithographically P-well on the N- epitaxial layer, and ion-implant boron with a dose of 5E12cm -2 , the energy is 60keV, the well region advances, and the junction depth is about 6.0μm". (c) "Ion implantation of boron in step (8) in Example 1, the dose is 5E15cm -2 , the energy is 80keV" is modified to "ion implantation of phosphorus, the dose is 5E15cm -2 , the energy is 60keV". (d) Ion-implant boron 22 into the "PMOS region" in step (9) of Example 1, with a dose of 8E15cm -2 , the energy is 60keV" is changed to "Ion implantation of phosphorus in...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com