Micro-mechanical wafer chip test detecting card and its production

A chip testing, wafer-level technology, used in semiconductor/solid-state device testing/measurement, electrical measurement, measurement devices, etc., to solve problems such as limiting work performance, difficult to test signal transmission analysis, and probe array flatness effects. , to achieve the effect of simplifying the manufacturing process, high probe flatness, and simplifying the process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

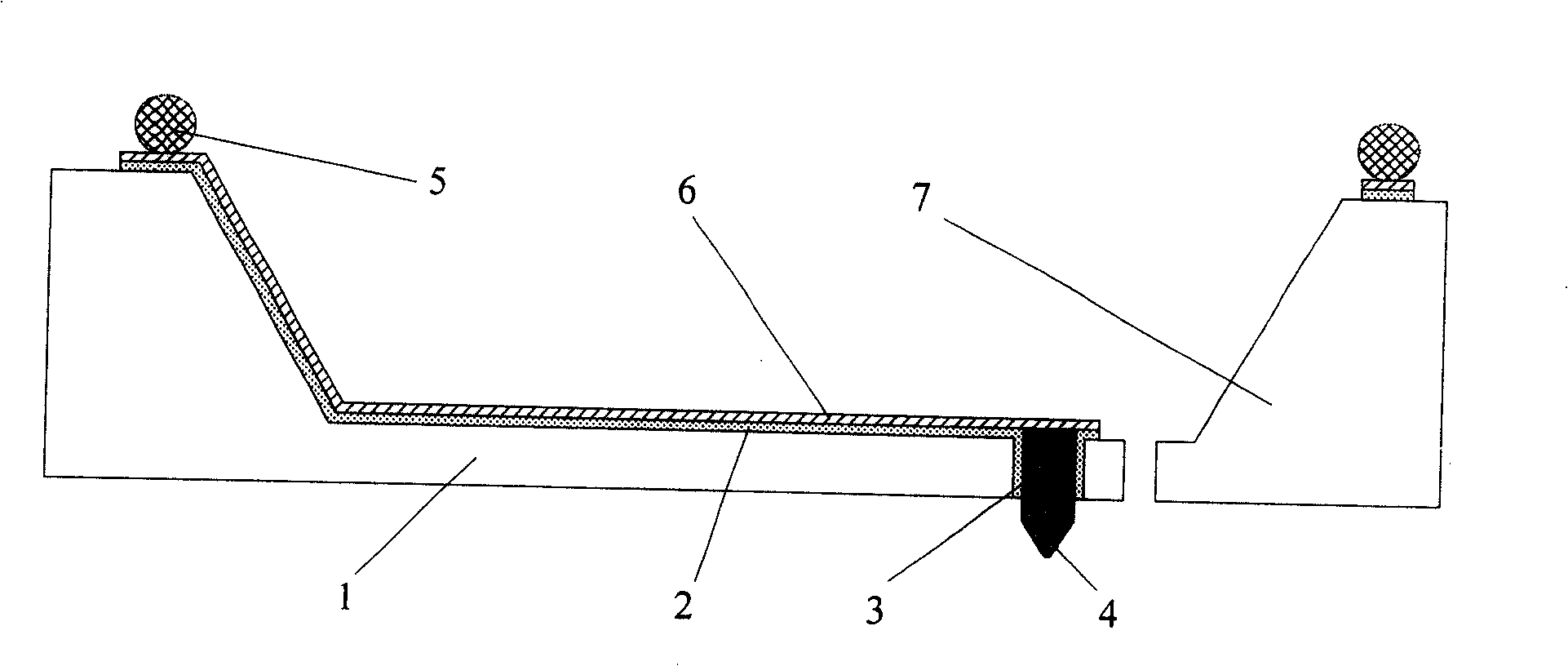

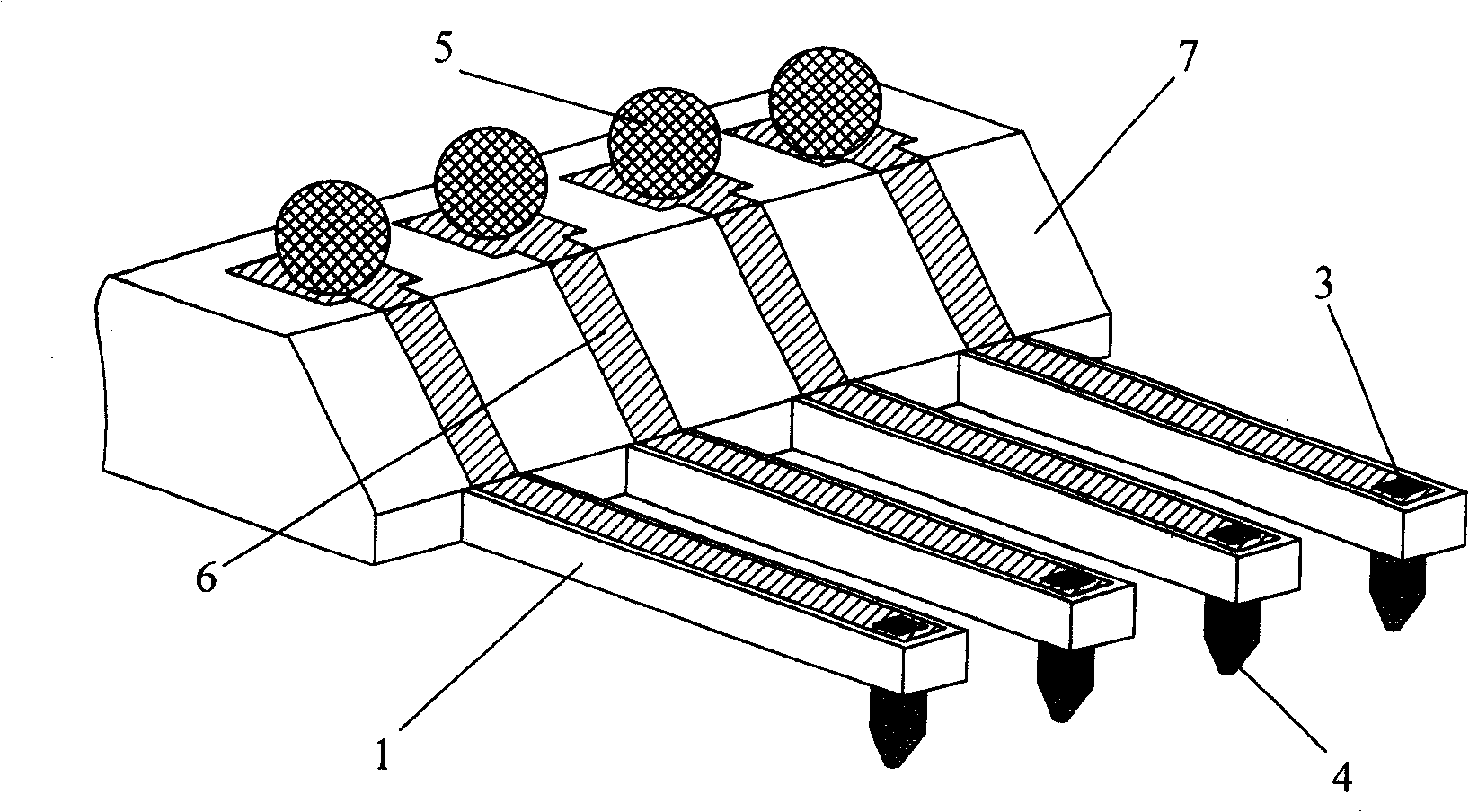

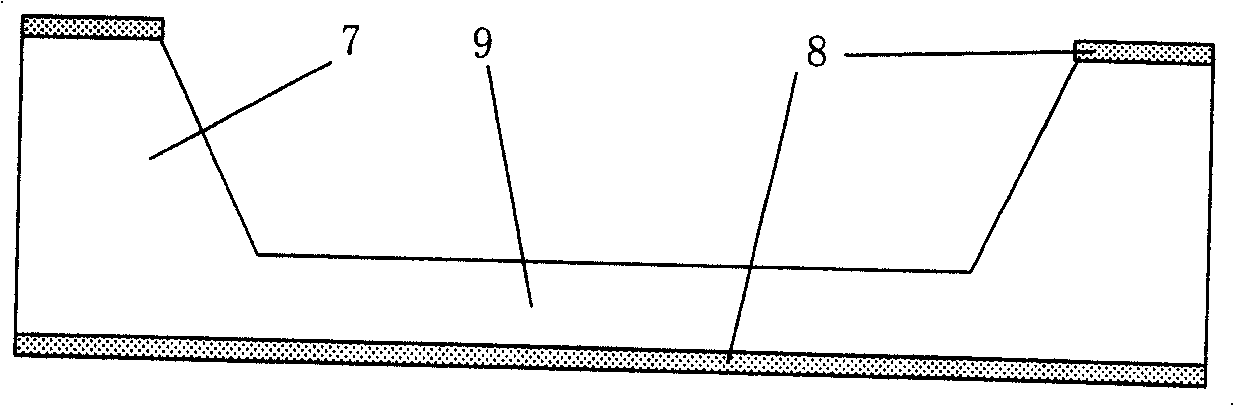

[0076] 1. Deposit or oxidize a 1.5-2.5 μm thick oxide layer 8 on the front and back sides of (100) double-sided polished silicon wafer 7 as an etching mask, and use 50 ° C and 40% KOH solution to etch the etching window. About 300 μm, the thickness of the reserved silicon film 9 is the sum of the thickness of the cantilever beam and the height of the probe ( image 3 );

[0077] 2. The oxide layer 8 on the back side of the photolithographic silicon wafer 7 is used as a mask, and the silicon film 9 is etched to form interconnection holes 10 ( Figure 4 );

[0078] 3. Remove the oxide layer 8 on the surface of the silicon wafer 7, and oxidize and generate 2.0 μm thick SiO on the surface of the silicon wafer and interconnect holes 2 Insulating layer 2, sputtering 5000 on the upper surface of the silicon wafer Titanium copper metal layer 11 ( Figure 5 );

[0079] 4. Spray glue on the front side of the silicon wafer 7 and photoetch a 10 μm thick photoresist mask 12, and use ...

Embodiment 2

[0086] 1. Same as in Example 1, deposit or oxidize a 1.5-2.5 μm thick oxide layer 8 on both sides of the (100) double-sided polished silicon wafer 7 as an etching mask, and use 50° C. and 40% KOH solution to etch the window by photolithography Etching is carried out, the etching depth is about 300 μm, and the thickness of the remaining silicon film 9 is the sum of the thickness of the cantilever beam and the height of the probe ( image 3 );

[0087] 2. Deposit or oxidize 5000 Oxide layer, utilize glue-spray photolithography to form etching window 19, carry out second time KOH etching, form inverted pyramid shape 20 ( Figure 12 );

[0088] 3. Use reactive ion etching to etch through the silicon film 9 from top to bottom to form interconnection holes 21 with a needle point shape, and then oxidize the surface of the silicon wafer 7 to form SiO with a thickness of 2 μm 2 Insulation layer 2 ( Figure 13 );

[0089] 4. Take another piece of silicon wafer as the adhesive shee...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com