Crystalline silicon solar battery piece capable of inhibiting electric leakage of cutting edge, battery assembly and preparation method of crystalline silicon solar battery piece

A solar cell and cutting edge technology, applied in the field of solar cells, can solve the problems affecting the separation and collection of carriers and the loss of electrical performance of half-cell cells, and achieve the effect of avoiding the loss of electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 2

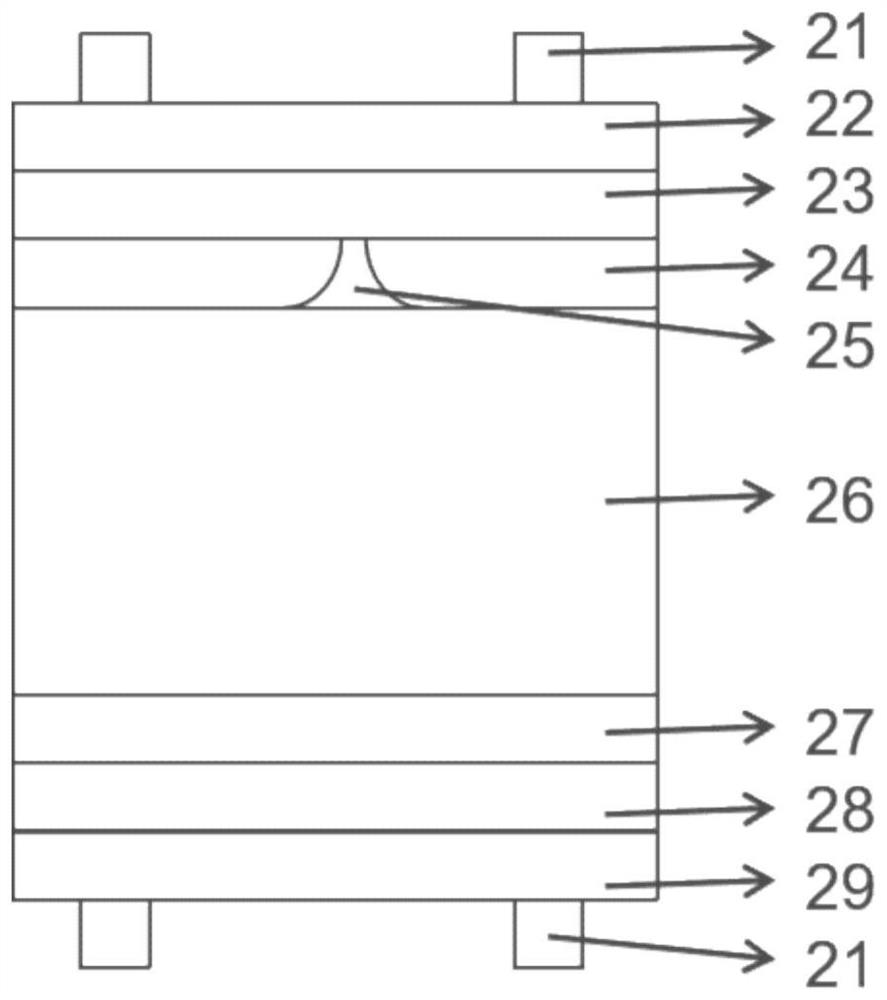

[0053] Such as figure 2 As shown, a crystalline silicon solar cell with a TOPCon structure that suppresses leakage at the cutting edge, its preparation process is as follows:

[0054] (1) Provide an n-type crystalline silicon wafer 26 for cleaning and texturing; wherein, the resistivity of the n-type crystalline silicon wafer 26 is 0.5-1.5 Ω·cm; the thickness of the n-type crystalline silicon wafer 26 is 100-160 μm.

[0055] (2) Put the obtained silicon wafer into an industrial high-temperature diffusion furnace to carry out high-temperature boron diffusion on the front to form a boron expansion layer 24, and then remove the borosilicate glass and winding plating formed during the diffusion process; wherein the boron source is boron tribromide , the boron diffusion temperature is 750-1000°C, the time is 60-180 minutes, and the square resistance value after boron diffusion is 60-120Ω / sqr.

[0056] (3) form a layer of photoresist by spin coating or spraying method on the front...

Embodiment 3

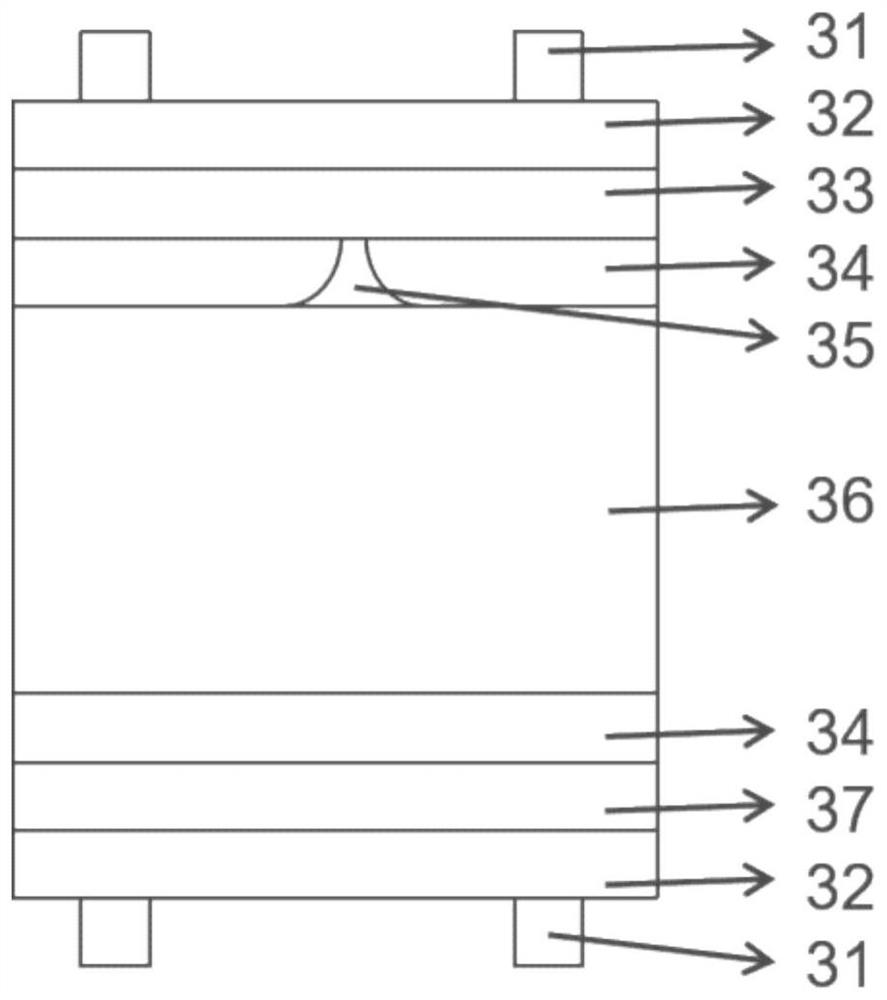

[0063] Such as image 3 As shown, a crystalline silicon solar cell with an HJT structure that suppresses leakage at the cut edge, the preparation process is as follows:

[0064] (1) Provide an n-type crystalline silicon wafer 36 for cleaning and texturing; wherein, the resistivity of the n-type crystalline silicon wafer 36 is 0.5-1.5 Ω·cm; the thickness of the n-type crystalline silicon wafer 36 is 80-140 μm.

[0065] (2) Form an intrinsic amorphous silicon layer or hydrogenated intrinsic amorphous silicon thin layer 34 on both sides of the obtained silicon wafer; wherein, the intrinsic amorphous silicon layer or hydrogenated intrinsic amorphous silicon thin layer 34 can pass through Plasma-enhanced chemical vapor deposition and other methods; the thickness of the intrinsic amorphous silicon layer or hydrogenated intrinsic amorphous silicon thin layer 34 is 1.5-4 nm.

[0066] (3) Prepare p+ type doped amorphous silicon thin layer 33 and n+ type doped amorphous silicon thin la...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com