Semiconductor layout and forming method thereof, formed semiconductor structure and method

A semiconductor and graphics technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as reducing the performance of semiconductor structures, and achieve the effect of eliminating load effects and improving performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

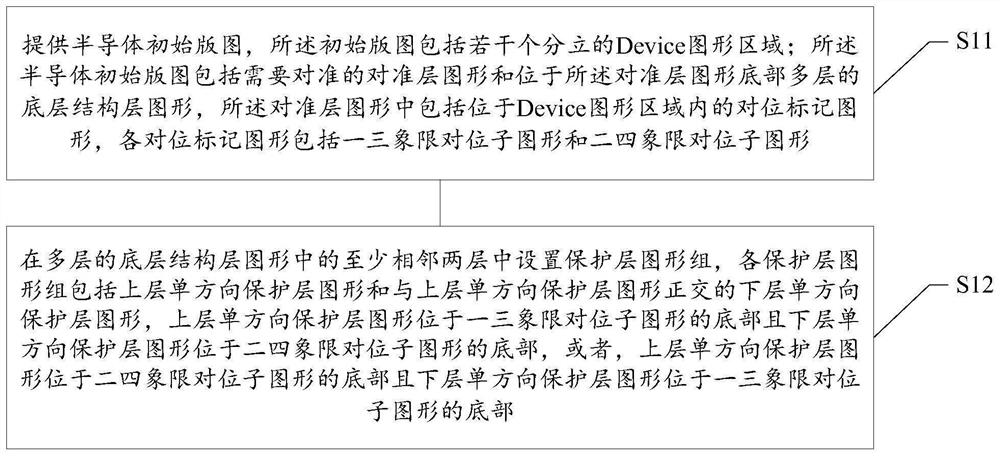

[0070] It can be seen from the background art that corresponding overlay mark patterns are provided in multiple process layers in a semiconductor structure, so as to achieve alignment between multiple process layers in a photolithography process.

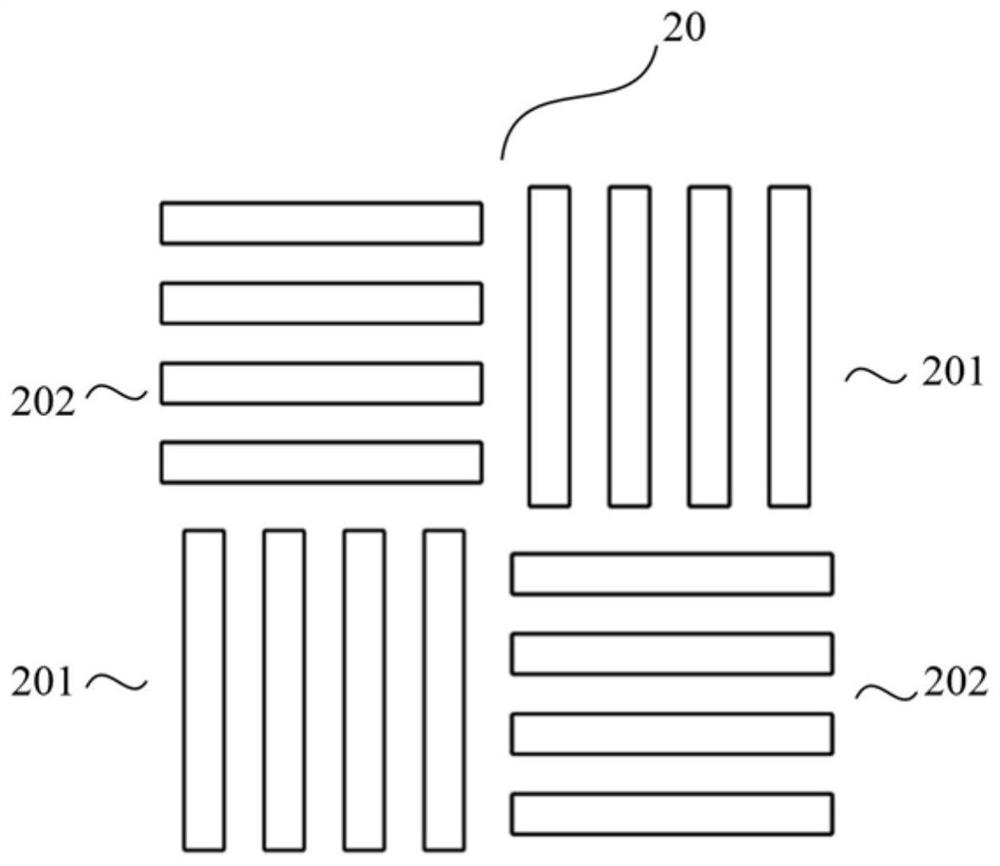

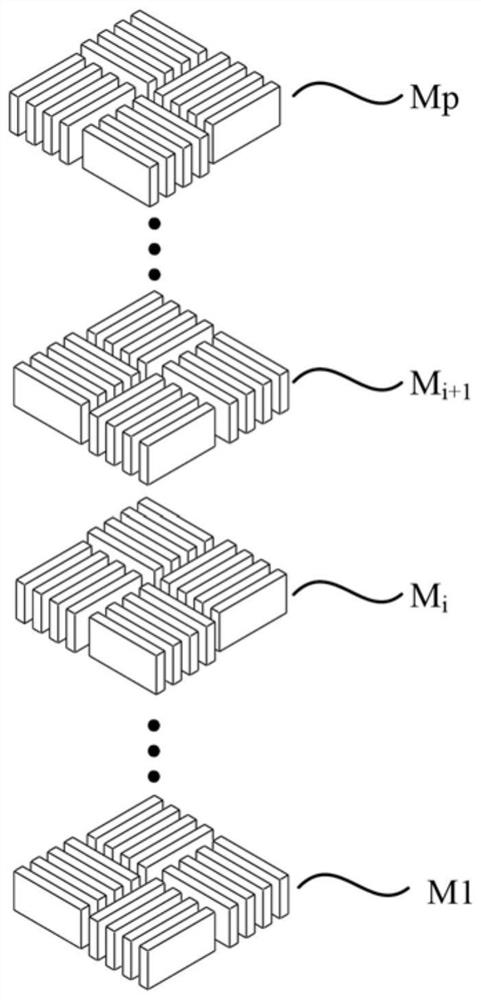

[0071] According to the light diffraction or interference theory, in order not to affect the measurement in the photolithography process, the gap (Pitch) of the protective layer pattern set in the process layer under the bottom alignment layer should be kept below 200nm, and the protection The direction of the layer pattern should be kept orthogonal to the direction of the protective layer pattern on the upper layer, that is, the protective layer pattern set in the multi-layer process layer is orthogonal to each other layer by layer from top to bottom. Since the pattern extension direction of the overlay mark is designed to exist simultaneously in the horizontal and vertical directions, the pattern extension direction of the protecti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com