Cutting method for LED wafer with ITO and aluminum electrode growing on surface

A technology of surface growth and cutting method, applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of limited improvement in cutting quality, internal damage to the wafer, hidden dangers of increasing cutting quality, etc., to reduce the difficulty of high-pressure cleaning and improve electrical conductivity. performance, the effect of avoiding electrochemical corrosion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

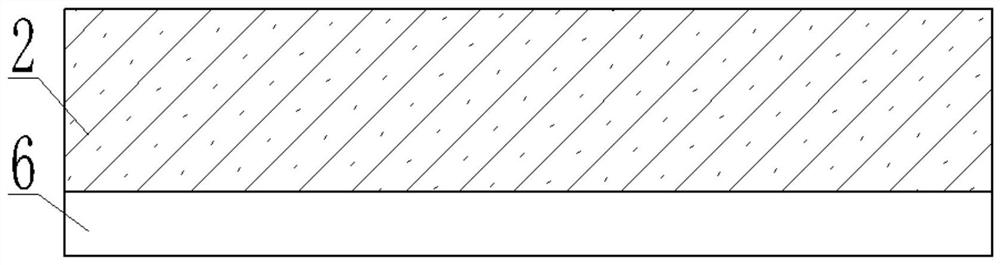

[0060] S1: Growth of epitaxial layer 2: Prepare the growth materials for epitaxial layer 2, and check the operation of each device; then take GaAs substrate 6, and grow epitaxial buffer layer, N-type gallium arsenide layer, MQW quantum A well layer, a P-type AlGaInP layer, a P-type GaAs layer, and a GaP window layer to obtain a wafer with an epitaxial layer 2;

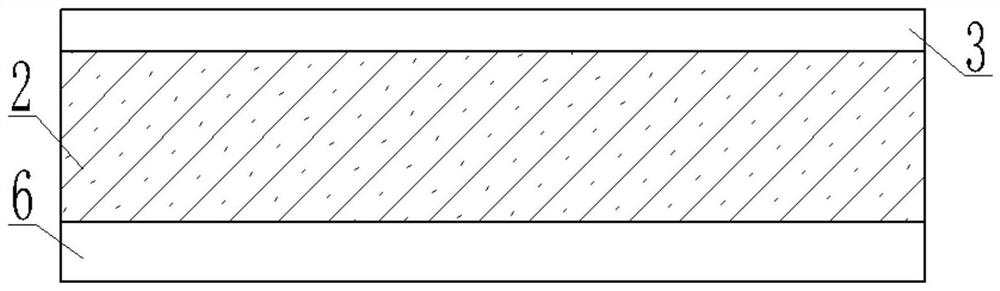

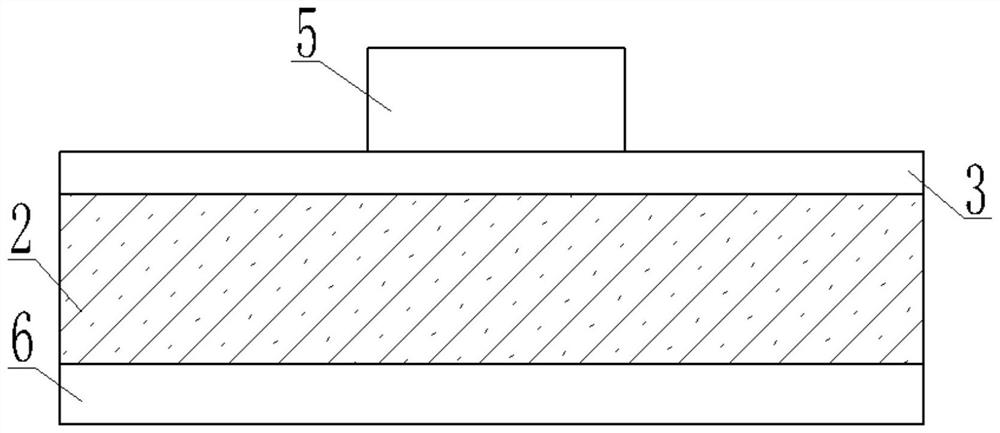

[0061] S2: grow the ITO film layer 3, and then prepare the P-face electrode structure 5: take the wafer with the epitaxial layer 2, grow the ITO film layer 3 on the surface of the epitaxial layer 2, and the ITO film layer 3 covers the entire surface of the epitaxial layer 2, wherein the ITO The thickness of the film layer 3 is The growth temperature is 270°C; and then a photoresist mask pattern is made on the surface of the ITO film layer 3 to grow the P-face electrode structure 5;

[0062] S3: Prepare N-face electrode 1: take the wafer with P-face electrode structure 5, thin the GaAs substrate 6 of the wafer, and gr...

Embodiment 2

[0068] S1: Growth of epitaxial layer 2: Prepare the growth materials for epitaxial layer 2, and check the operation of each device; then take GaAs substrate 6, and grow epitaxial buffer layer, N-type gallium arsenide layer, MQW quantum A well layer, a P-type AlGaInP layer, a P-type GaAs layer, and a GaP window layer to obtain a wafer with an epitaxial layer 2;

[0069] S2: grow the ITO film layer 3, and then prepare the P-face electrode structure 5: take the wafer with the epitaxial layer 2, grow the ITO film layer 3 on the surface of the epitaxial layer 2, and the ITO film layer 3 covers the entire surface of the epitaxial layer 2, wherein the ITO The thickness of the film layer 3 is The growth temperature is 300°C; and then a photoresist mask pattern is made on the surface of the ITO film layer 3 to grow the P-side electrode structure 5;

[0070] S3: Prepare N-face electrode 1: take the wafer with P-face electrode structure 5, thin the GaAs substrate 6 of the wafer, and gr...

Embodiment 3

[0076] S1: Growth of epitaxial layer 2: Prepare the growth materials for epitaxial layer 2, and check the operation of each device; then take GaAs substrate 6, and grow epitaxial buffer layer, N-type gallium arsenide layer, MQW quantum A well layer, a P-type AlGaInP layer, a P-type GaAs layer, and a GaP window layer to obtain a wafer with an epitaxial layer 2;

[0077] S2: grow the ITO film layer 3, and then prepare the P-face electrode structure 5: take the wafer with the epitaxial layer 2, grow the ITO film layer 3 on the surface of the epitaxial layer 2, and the ITO film layer 3 covers the entire surface of the epitaxial layer 2, wherein the ITO The thickness of the film layer 3 is The growth temperature is 330°C; and then a photoresist mask pattern is made on the surface of the ITO film layer 3 to grow the P-face electrode structure 5;

[0078] S3: Prepare N-face electrode 1: take the wafer with P-face electrode structure 5, thin the GaAs substrate 6 of the wafer, and gr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com