Monocrystalline silicon wafer with pyramid superposition structure and preparation method

A single crystal silicon wafer and pyramid technology, which is applied in the field of solar cells, can solve the problems of insufficient contact between the small pyramid suede and the conductive grid lines, increase the contact resistance, and reduce the welding tension of the grid lines, so as to achieve good welding reliability, The effect of high short-circuit current and low reflectivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

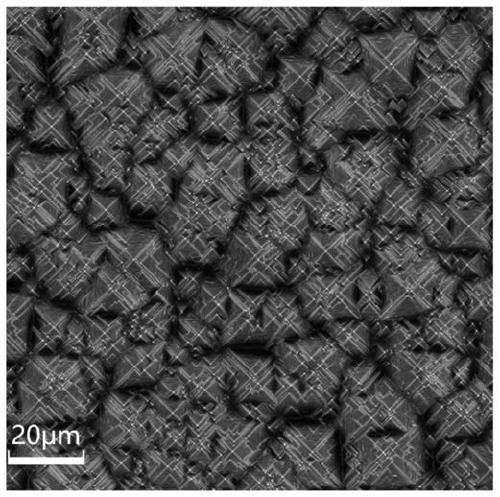

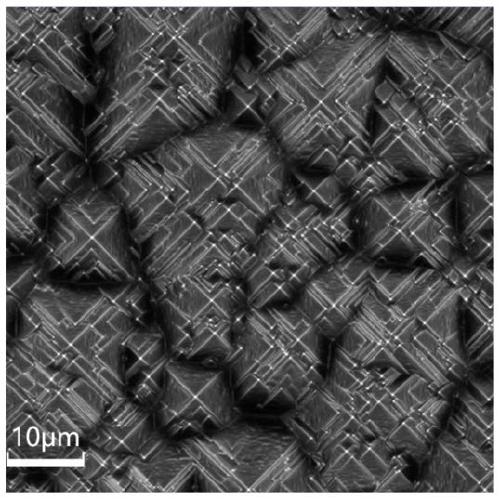

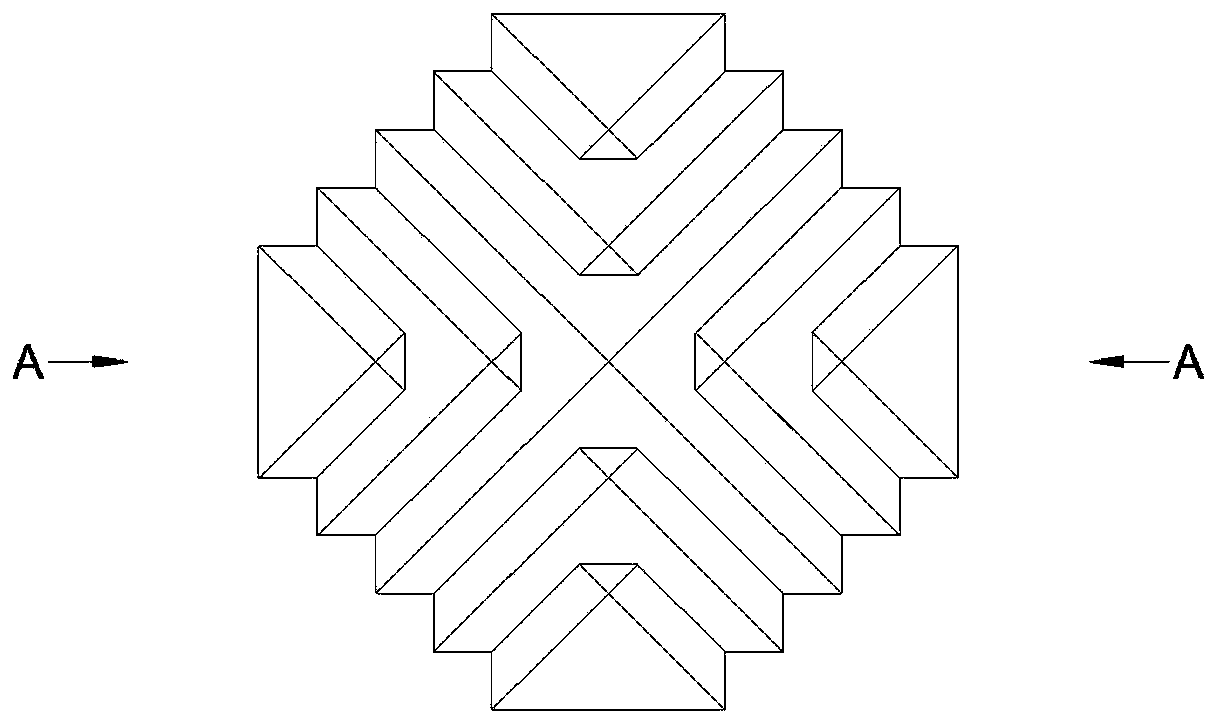

[0029] refer to Figure 1~6 , a single crystal silicon wafer with a pyramid superposition structure, including a silicon wafer whose surface is covered with pyramid units after textured.

[0030] As a preferred manner, the pyramid unit includes a large pyramid, and the surface of the large pyramid is sequentially stacked with small pyramids from top to bottom.

[0031] As a preferred manner, the length of the base of the small pyramid is less than half of that of the large pyramid.

[0032] As a preferred manner, the bottom area of the pyramid units is 1-500 square microns.

[0033] As a preferred manner, the number of pyramids included in the pyramid unit is 5-500.

[0034] The above-mentioned method for preparing a single crystal silicon wafer with a pyramid superposition structure is characterized in that it comprises the following steps:

[0035] A. Pre-cleaning to remove the surface contamination of the original silicon wafer. Use one or more of ammonia water, sodiu...

Embodiment 2

[0044] refer to Figure 1~6 , in this embodiment, optional but not limited to using the texture additive of Nippon Hayashi pure HPC to prepare the texture of the pyramid superposition structure, the specific steps are as follows:

[0045] (1) Pre-cleaning

[0046] Clean the original silicon chip in a mixed solution of ammonia water and hydrogen peroxide, the mass concentration of ammonia water in the solution is 3%, the mass concentration of hydrogen peroxide is 3%, the temperature is 65° C., and the cleaning time is 5 minutes. After cleaning, rinse the silicon wafer in pure water at room temperature for 3 minutes.

[0047] (2) The first step of cashmere

[0048] Use Nippon Hayashi pure HPC texture additive, the mass concentration of each component in the solution: potassium hydroxide is 7.5%, TK81 is 4%, TT72C13 is 0.6%, the temperature is 85°C, and the time is 15min. Rinse the silicon wafer in pure water at room temperature for 3 minutes after texturing.

[0049] (3) The...

Embodiment 3

[0066] refer to Figure 1~6 , in this embodiment, optional but not limited to using the texture additive of ICB of Germany to prepare the texture of the pyramid superposition structure, the specific steps are as follows:

[0067] (1) Pre-cleaning

[0068] Clean the original silicon chip in a mixed solution of potassium hydroxide and hydrogen peroxide, the mass concentration of potassium hydroxide in the solution is 1.5%, the mass concentration of hydrogen peroxide is 3%, the temperature is 65° C., and the cleaning time is 5 minutes. After cleaning, rinse the silicon wafer in pure water at room temperature for 3 minutes.

[0069] (2) The first step of cashmere

[0070] Use the German ICB texturing additive, the mass concentration of each component in the solution: potassium hydroxide is 4.5%, ICBUltra M is 0.8%, the temperature is 85°C, and the time is 10min. Rinse the silicon wafer in pure water at room temperature for 3 minutes after texturing.

[0071] (3) The second ste...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com