A method for reducing the voltage of a 3D through-hole superstructure LED chip by anaerobic dry etching in a hole

An LED chip, dry etching technology, applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of passivation layer corrosion failure, inability to progress, LED chip voltage increase, etc., to achieve improved current distribution uniformity, good quality The effect of rate improvement and light efficiency improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

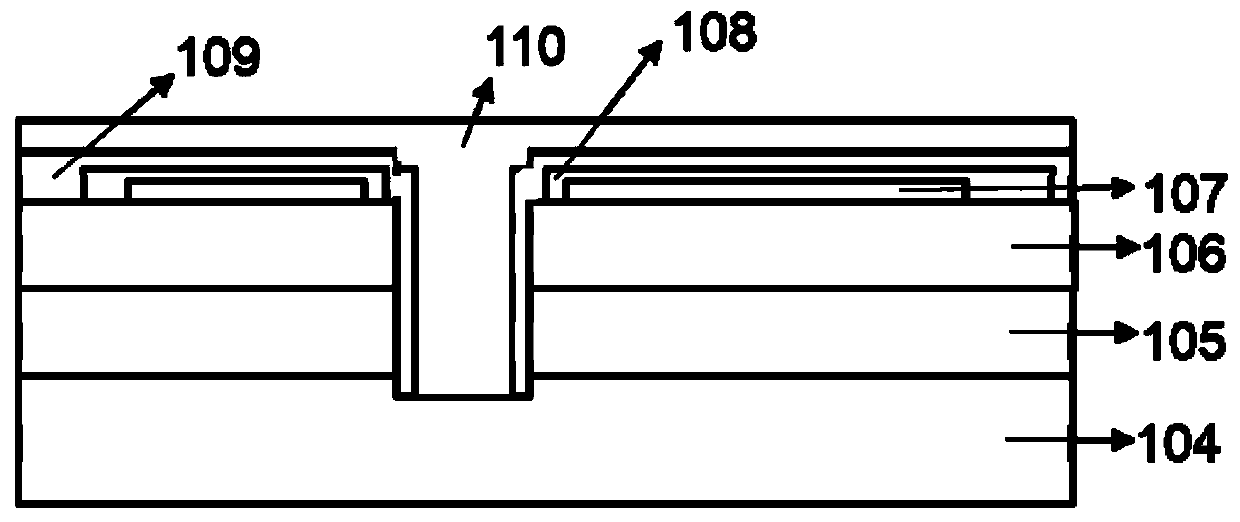

[0053] A method for reducing the voltage of a 3D through-hole superstructure LED chip by anaerobic dry etching in a hole, comprising the following preparation steps:

[0054] (1) Provide a silicon substrate, and epitaxially grow LED epitaxial wafers on the silicon substrate, including n-type doped GaN films grown on silicon substrates, and InGaN / GaN multiple quantum wells grown on n-type doped GaN films , p-type doped GaN films grown on InGaN / GaN multiple quantum wells. The Si substrate has a (111) plane as an epitaxial plane. The thickness of the n-type doped GaN film is 1.8um; the InGaN / GaN multi-quantum well is 10 cycles of InGaN well layer / GaN barrier layer, wherein the thickness of the InGaN well layer is 5nm, and the thickness of the GaN barrier layer is 14nm; The thickness of the p-type doped GaN film is 250nm;

[0055] (2) Use the magnetron sputtering process to sputter nano-Ag-based reflectors on the surface of the LED epitaxial wafer, the sputtering power is 4.5kW,...

Embodiment 2

[0070] A method for reducing the voltage of a 3D through-hole superstructure LED chip by anaerobic dry etching in a hole, comprising the following preparation steps:

[0071] (1) Provide a Cu substrate, and epitaxially grow LED epitaxial wafers on the Cu substrate, including n-type doped GaN films grown on Cu substrates, and InGaN / GaN multiple quantum wells grown on n-type doped GaN films , p-type doped GaN films grown on InGaN / GaN multiple quantum wells. The Cu substrate has a (111) plane as an epitaxial plane. The thickness of the n-type doped GaN film is 3.5um; the InGaN / GaN multi-quantum well is 6 cycles of InGaN well layer / GaN barrier layer, wherein the thickness of InGaN is 6nm, and the thickness of GaN barrier layer is 11nm; The thickness of the p-type doped GaN film is 400nm;

[0072] (2) Nano-Ag-based reflectors were evaporated on the surface of the LED epitaxial wafer by electron beam evaporation process, the evaporation rate was 2 Å / s, and the evaporation temperat...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com