Semiconductor device

A semiconductor, conductive type technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of applying a large electric field, insulation breakdown of the gate insulating film, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

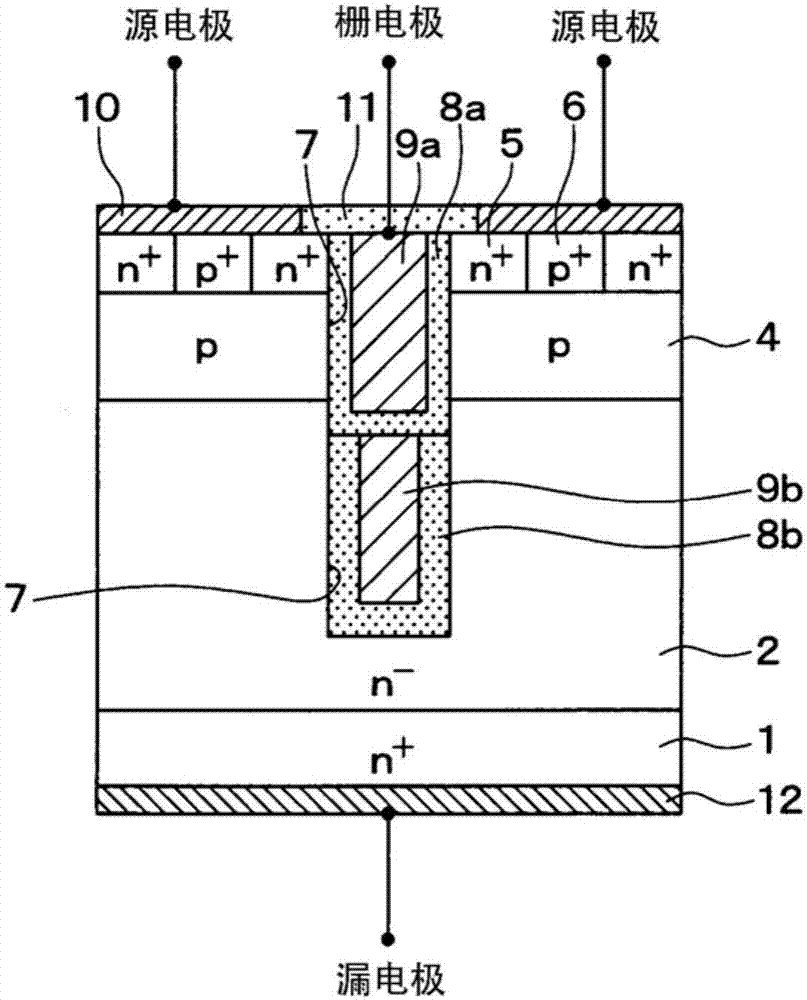

[0020] A first embodiment of the present disclosure will be described. Here, although a SiC semiconductor device in which the semiconductor device is formed of SiC is taken as an example and described, the semiconductor device may be formed of other semiconductor materials such as Si.

[0021] First, refer to figure 1 A SiC semiconductor device having a vertical MOSFET with an inverted trench gate structure according to this embodiment will be described. Also, while in figure 1 Only one cell with a vertical MOSFET is documented, but with figure 1 Semiconductors having the same structure as the illustrated vertical MOSFETs are arranged so that a plurality of cells are adjacent to each other. A unit mentioned here refers to the p + The center of the type contact region 6 starts from the p + The center of the type contact area 6.

[0022] Such as figure 1 As shown, using a SiC single crystal composed of n + type semiconductor substrate 1 to form a SiC semiconductor device...

no. 2 approach

[0043] A second embodiment of the present disclosure will be described. This embodiment has a structure capable of further increasing the breakdown voltage compared to the first embodiment, and since other points are the same as the first embodiment, only the parts different from the first embodiment will be described.

[0044] Such as figure 2 As shown, in the SiC semiconductor device of this embodiment, the p-type deep layer 3 is formed on both sides of the trench gate structure so as to be separated from the trench 7 by a predetermined distance. In the case of this embodiment, the p-type deep layer 3 is set parallel to the trench 7, that is, parallel to the figure 2 The direction perpendicular to the paper surface is a short grid shape in the longitudinal direction, and a plurality of p-type deep layers 3 are arranged in stripes, and trenches 7 are arranged between each p-type deep layer 3 . Specifically, on both sides of the position where the trench 7 is formed, a par...

no. 3 approach

[0048] A third embodiment of the present disclosure will be described. This embodiment also has a structure that can further increase the withstand voltage compared to the first embodiment, and since other points are the same as the first embodiment, only the parts that are different from the first embodiment will be described.

[0049] Such as image 3As shown, in the SiC semiconductor device of this embodiment, the p-type underlayer 20 is formed on the surface layer portion of the n-type drift layer 2 at the bottom of the trench gate structure. In the case of this embodiment, the p-type underlayer 20 is formed over the entire area of the bottom of the trench 7, that is, in a image 3 The direction perpendicular to the paper surface is a short grid shape in the length direction. For example, p-type underlayer 20 is formed by ion-implanting p-type impurities in a state where the portion other than trench 7 is covered with a mask after trench 7 is formed. The p-type impuri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com