SOI substrate-based La-based high-dielectric constant gate dielectric structure and manufacturing method thereof

A high-dielectric-constant, high-dielectric-constant material technology, applied in nanotechnology, circuits, electrical components, etc. for materials and surface science, can solve problems that do not conform to the development of the thermal budget of the semiconductor industry and the poor step coverage of gate dielectrics. It can reduce the mobility of sodium ions, improve the anti-radiation performance, and improve the performance of the film.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

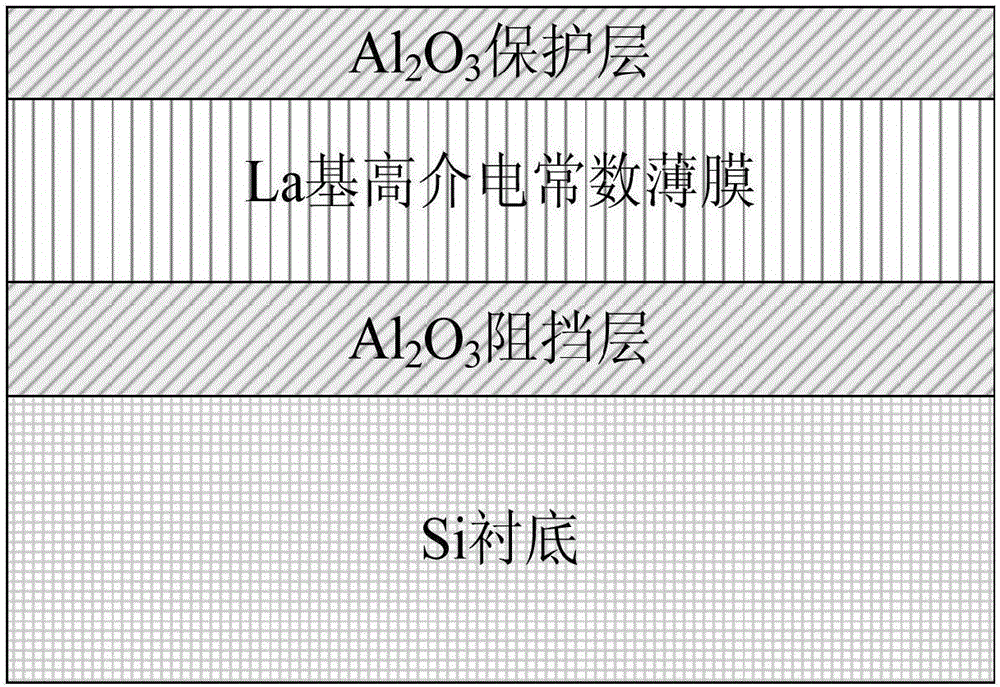

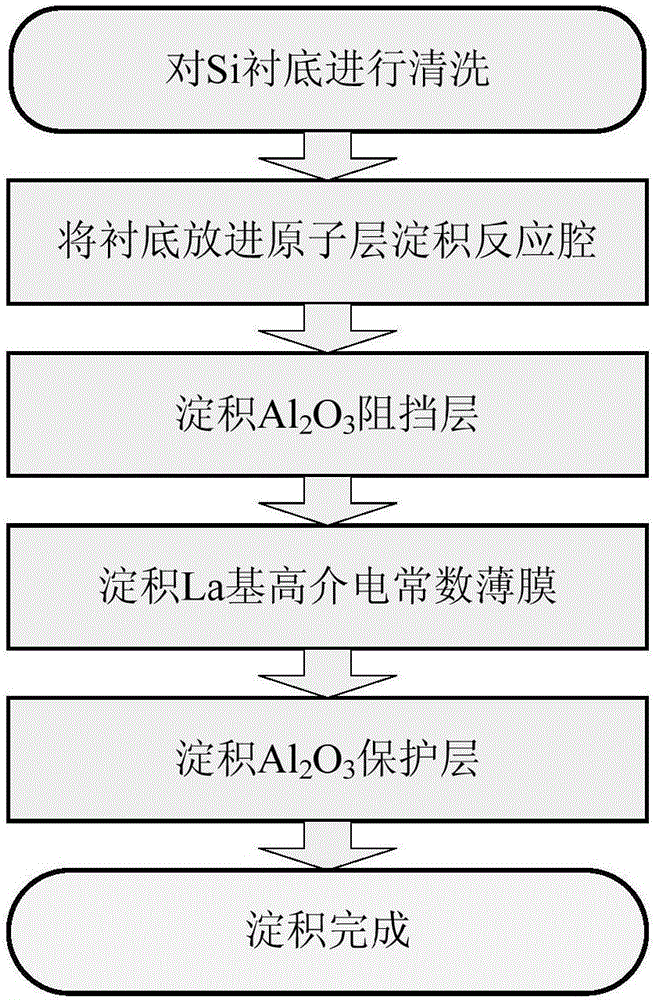

[0033] Example 1, Preparation of Al 2 O 3 \La 2 O 3 \Al 2 O 3 \SOI structure of high dielectric constant material gate dielectric.

[0034] Step 1. Clean the SOI substrate.

[0035] 1a) Soak the SOI substrate in the SC-1 solution heated to 75℃ for 10 minutes. The composition of the solution is NH 4 OH, H 2 O 2 And H 2 O, the ratio is 5:1:1, used to remove organic pollutants or attached particles on the SOI substrate;

[0036] 1b) Rinse the soaked SOI substrate in deionized water for 2 minutes to remove the residual SC-1 solution, and then take it out;

[0037] 1c) Wash the SOI substrate in an HF solution for 60 seconds before taking it out. The components of the solution are HF and H 2 O, the ratio is 1:50. The main function of this cleaning is to remove the natural oxide layer SiO on the surface of the SOI substrate 2 ;

[0038] 1d) Rinse the SOI substrate in deionized water to remove the residual HF solution, and then take it out;

[0039] 1e) Put the SOI substrate in deionized water a...

example 2

[0060] Example 2, Preparation of Al 2 O 3 \LaAlO 3 \Al 2 O 3 \SOI structure of high dielectric constant material gate dielectric.

[0061] Step one, cleaning the SOI substrate.

[0062] The specific implementation of this step is the same as step 1 of Example 1.

[0063] Step 2: Put the cleaned SOI substrate into the reaction chamber of the atomic layer deposition equipment, and deposit Al on the blow-dried substrate using the atomic layer deposition method 2 O 3 Barrier layer.

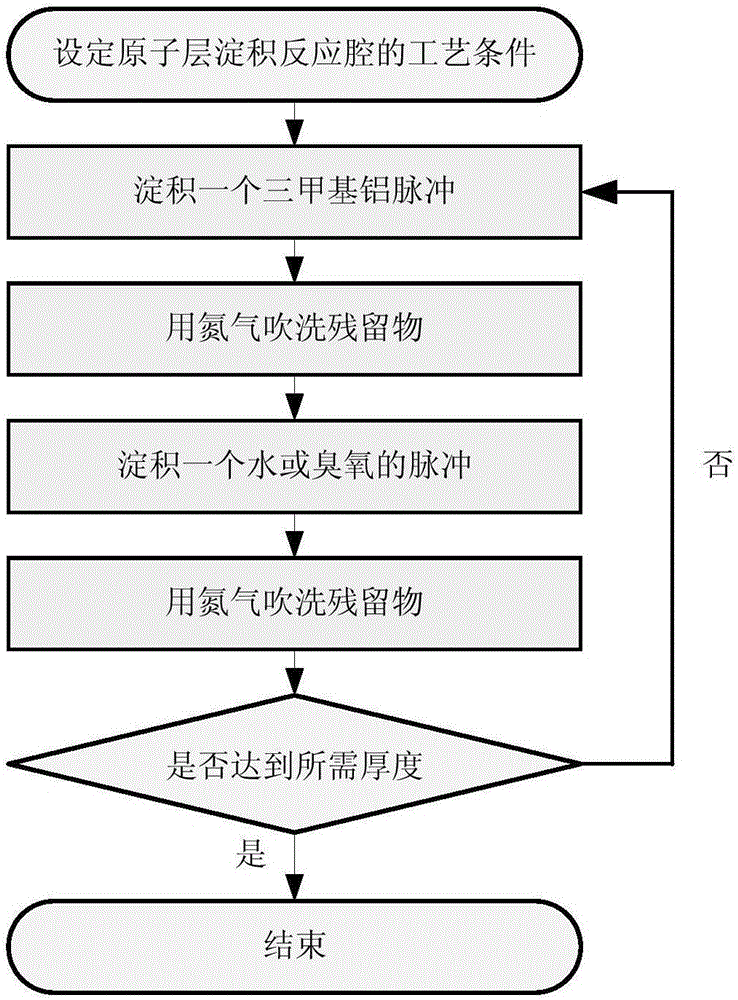

[0064] Reference image 3 , The specific implementation of this step is as follows:

[0065] 2.1) Evacuate the pressure of the atomic layer deposition equipment cavity to 12hPa, heat the temperature to 350°C, and set the nitrogen flow rate for purging to 250sccm;

[0066] 2.2) Deposit a pulse of trimethylaluminum for 0.3 seconds on the SOI substrate, such as Figure 5 As shown in t1, Al-O-Al-CH is generated 3 *And CH 4 ;

[0067] 2.3) Use nitrogen to treat the trimethylaluminum that was not successfully deposite...

example 3

[0084] Example 3. Preparation of Al 2 O 3 \HfLaO\Al 2 O 3 \SOI structure of high dielectric constant material gate dielectric

[0085] Step A, cleaning the SOI substrate.

[0086] The specific implementation of this step is the same as step 1 of Example 1.

[0087] Step B: Put the cleaned SOI substrate into the reaction chamber of the atomic layer deposition equipment, and deposit Al on the blow-dried substrate using the atomic layer deposition method 2 O 3 Barrier layer.

[0088] Reference image 3 , The specific implementation of this step is as follows:

[0089] B1) Evacuate the pressure of the atomic layer deposition equipment cavity to 20hPa, heat the temperature to 300°C, and set the nitrogen flow rate for purging to 200sccm;

[0090] B2) Deposit a pulse of trimethylaluminum for 0.1 second on the SOI substrate, such as Figure 5 As shown in t1, Al-O-Al-CH is generated 3 *And CH 4 ;

[0091] B3) Use nitrogen to treat the trimethylaluminum that was not successfully deposited on the S...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com