Composite double-gate high-speed PMOS device based on Ga2O3 material and production method of composite double-gate high-speed PMOS device

A compound, high-speed technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as insufficient hole transport rate, low thermal conductivity, and affecting device performance, and achieve the reduction of short channel effect, high transconductance, and high carrier mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

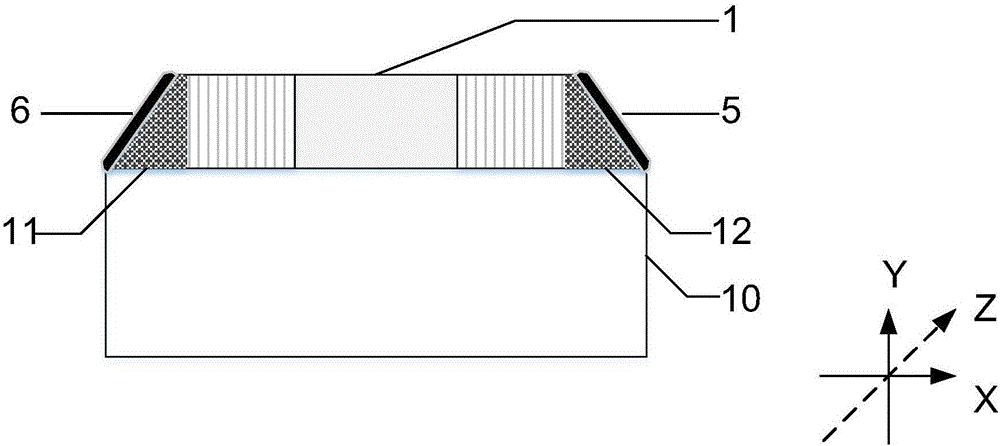

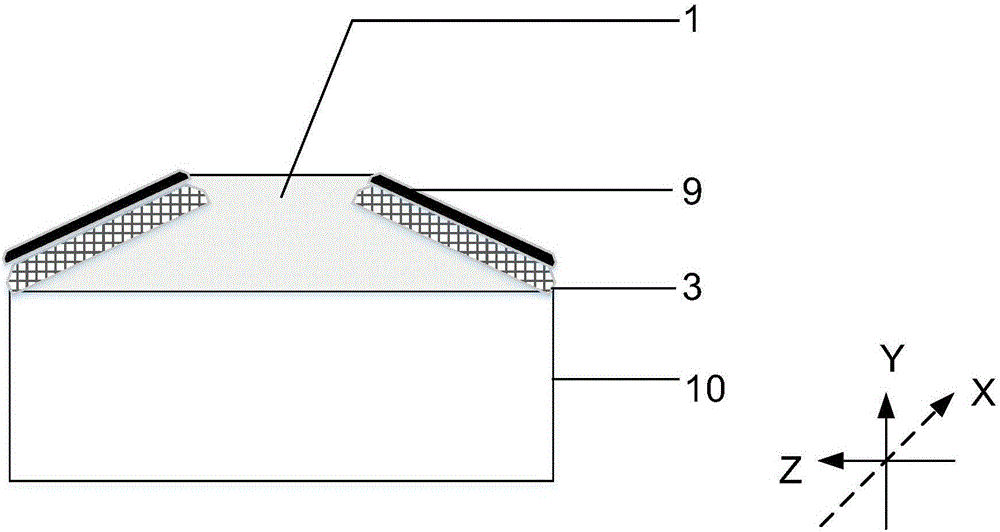

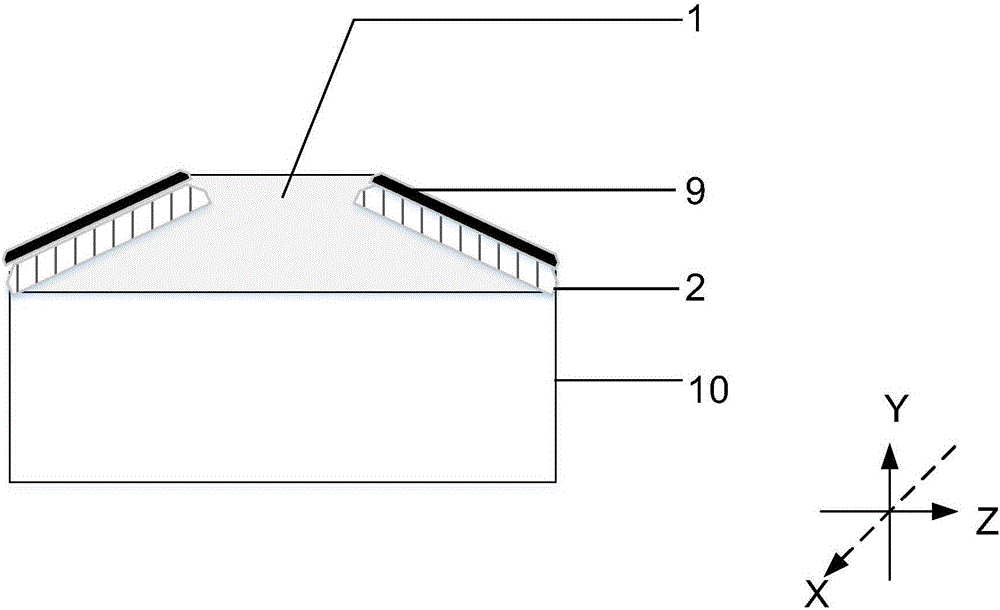

[0047] See figure 1 , figure 2 , image 3 and Figure 4 , figure 1 A Ga-based 2 o 3 The first cross-sectional schematic diagram of the composite double-gate high-speed PMOS device of the material (taken along the plane formed by the XY axis), figure 2 A Ga-based 2 o 3 The second cross-sectional schematic diagram of the compound double-gate high-speed PMOS device of the material (intercepted along the plane formed along the ZY axis, and the viewing angle is: the direction of the drain electrode → source electrode), image 3 A Ga-based 2 o 3 The third cross-sectional schematic diagram of the composite double-gate high-speed PMOS device of the material (taken along the plane formed along the ZY axis, and the viewing angle is: the direction of the source electrode → the drain electrode), Figure 4 A Ga-based 2 o 3 A schematic top view of a composite double-gate high-speed PMOS device made of materials. The composite double-gate high-speed PMOS device includes a gall...

Embodiment 2

[0076] Please also see Figure 6a-6j , Figures 7-10, Figure 6a-6j A Ga-based 2 o 3 A schematic diagram of the preparation method of a composite double-gate high-speed PMOS device; FIG. 7 is a schematic structural diagram of a first mask set provided by an embodiment of the present invention; FIG. 8 is a second mask provided by an embodiment of the present invention Figure 9 is a schematic structural view of a third mask provided by an embodiment of the present invention; Figure 10 is a schematic structural view of a fourth mask provided by an embodiment of the present invention; and Figure 11a-Figure 11d A schematic structural diagram of a fifth mask set provided by an embodiment of the present invention. On the basis of the above-mentioned embodiments, this embodiment is based on the Ga 2 o 3 The preparation method of the composite double-gate high-speed PMOS device of the material is described in detail as follows:

[0077] Step 1: See Figure 6a , prepare a semi-in...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com