Delay line capable of automatically balancing technological deviations and temperature influences

A technology of process deviation and automatic balance, applied in the direction of automatic power control, pulse processing, electrical components, etc., can solve the problems of delay-locked loop unable to lock, small dynamic range of operating frequency, large deviation of output signal, etc., to save chips Area and cost, improved frequency dynamic range, reduced latency effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The specific implementation of a delay line that automatically balances process deviation and temperature effects in the DLL disclosed in the present invention will be described in detail below with reference to the accompanying drawings, which is not intended to limit the scope of the present invention.

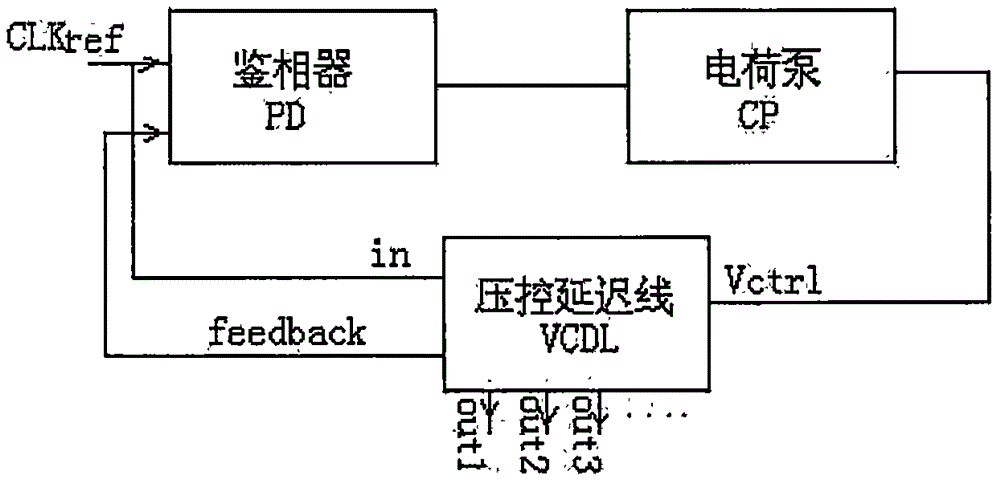

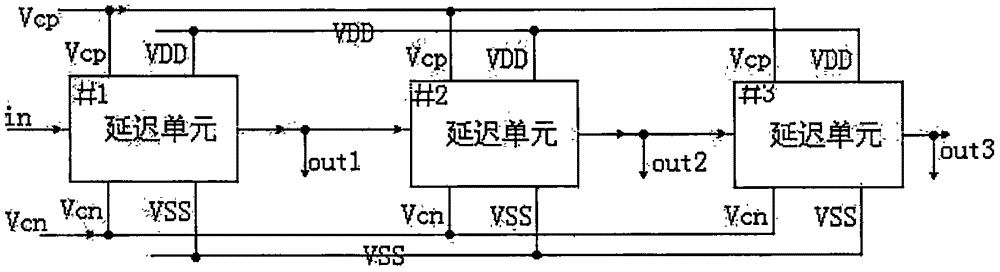

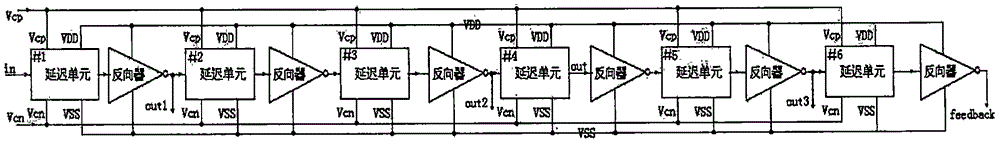

[0022] figure 1 The structure diagram of the delay locked loop is shown, which is composed of three parts: a phase detector PD, a charge pump CP, and a voltage-controlled delay line VCDL. The phase detector CLKref signal is the input reference clock signal, and the output signal feedback of the delay line VCDL is the output signal of the last stage on the delay line, which is sent to the phase detector to compare with the phase of the CLKref signal, and the obtained phase difference is sent to the charge pump, the charge pump outputs a VCTRL voltage control signal according to the phase difference information, and this voltage control signal is used to control the del...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com