Fabrication method of three-dimensional capacitively coupled interconnect structure based on through-silicon capacitor

A technology of capacitive coupling and interconnection structure, applied in the field of microelectronics, can solve the problems of complex manufacturing process, performance and yield reduction, large occupied area, etc., and achieve shortening of process, reduction of process equipment, and influence of device performance and yield Reduced effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

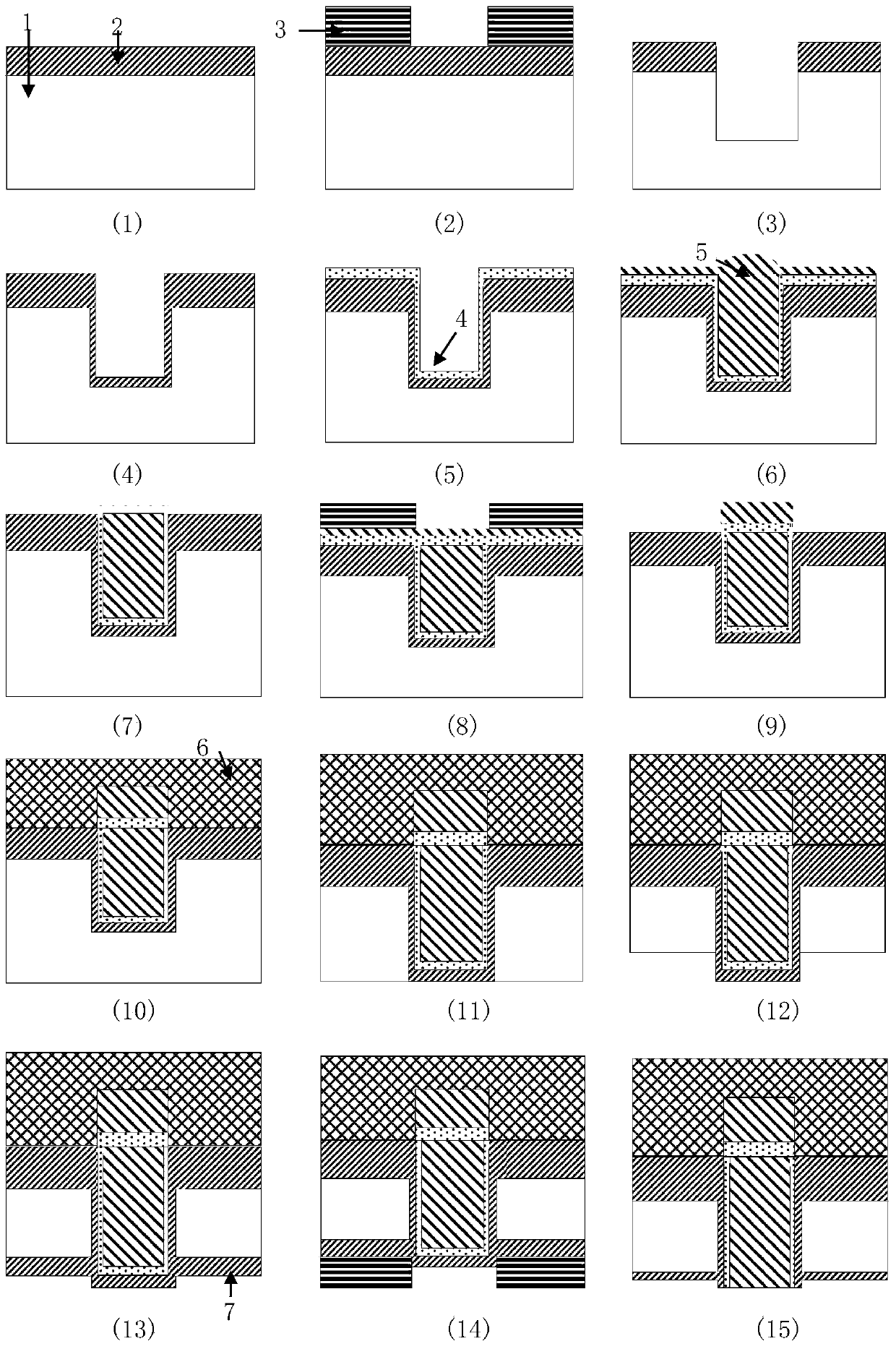

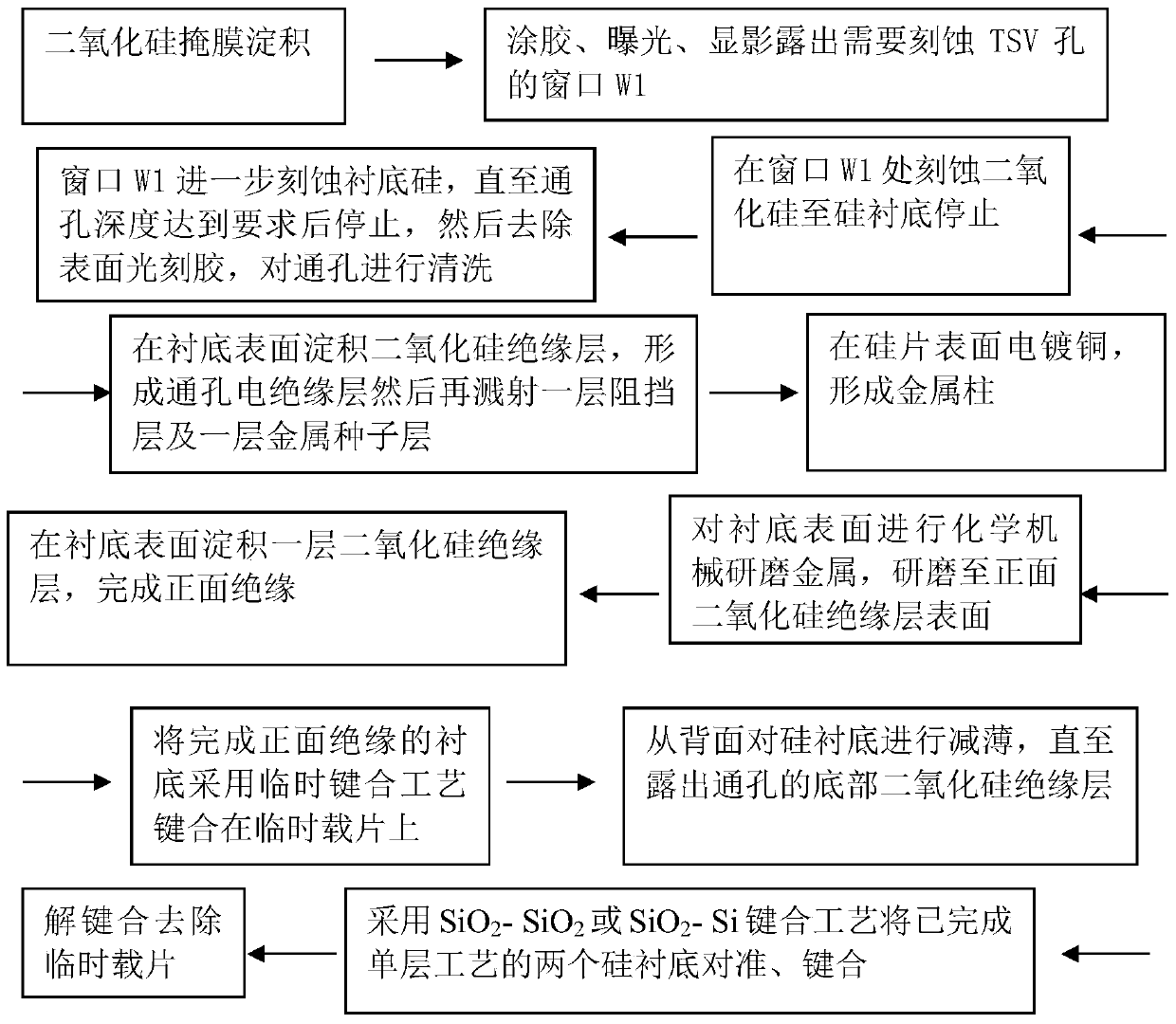

[0046] A method for manufacturing a three-dimensional capacitively coupled interconnection structure based on a through-silicon capacitor of the present invention, the wafer substrate used is P-type silicon, and the thickness of the silicon substrate is 675 μm, specifically comprising the following steps:

[0047] (1) growing a silicon dioxide mask layer 2 on the surface of the silicon substrate 1, the thickness of the mask layer is 2 μm;

[0048] (2) Coating photoresist 3 on the surface of silicon dioxide mask layer 2 Expose and develop to expose the window W1 that needs to be etched on the top layer of silicon. This window is circular with a diameter of 5 μm;

[0049] (3) Etch the silicon dioxide mask layer 2 at the window W1 until the silicon substrate 1 stops, and the etching depth is 2 μm; further etch the silicon substrate 1 at the window W1, and stop forming when the etching depth is 30 μm Through holes, then remove the surface photoresist 3, and clean the through hol...

Embodiment 2

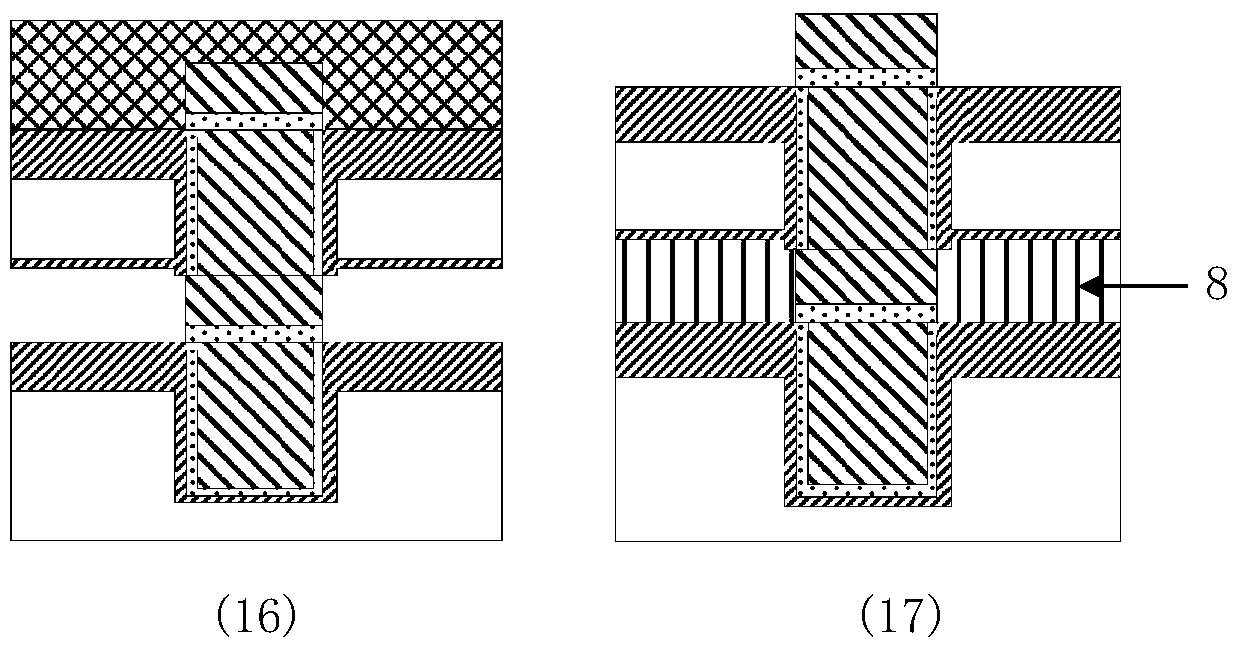

[0061] A manufacturing method of a three-dimensional capacitively coupled interconnection structure based on through-silicon capacitors in the present invention adopts the SOI wafer substrate as P-type silicon, and the thickness of the buried oxide layer is Top Silicon Thickness Specifically include the following steps:

[0062] (1) Coating photoresist on the surface of SOI substrate Expose and develop to expose the window W1 that needs to be etched on the top layer of silicon. This window is circular with a diameter of 5 μm;

[0063] (2) Etch the top layer of silicon at the window W1 until the silicon dioxide buried oxide layer stops forming a through hole, and the etching depth is Then remove the surface photoresist and clean the through holes (deionized water + IPA + EKC);

[0064] (3) Use PECVD (Ion Enhanced Chemical Vapor Deposition) method to deposit a layer of silicon dioxide insulating layer with a thickness of 1 μm on the surface of the substrate, so that the t...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com