Method of forming semiconductor device

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve the problems of dielectric layer dishing, affecting the reliability of semiconductor devices, etc., and achieve the effect of avoiding dishing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

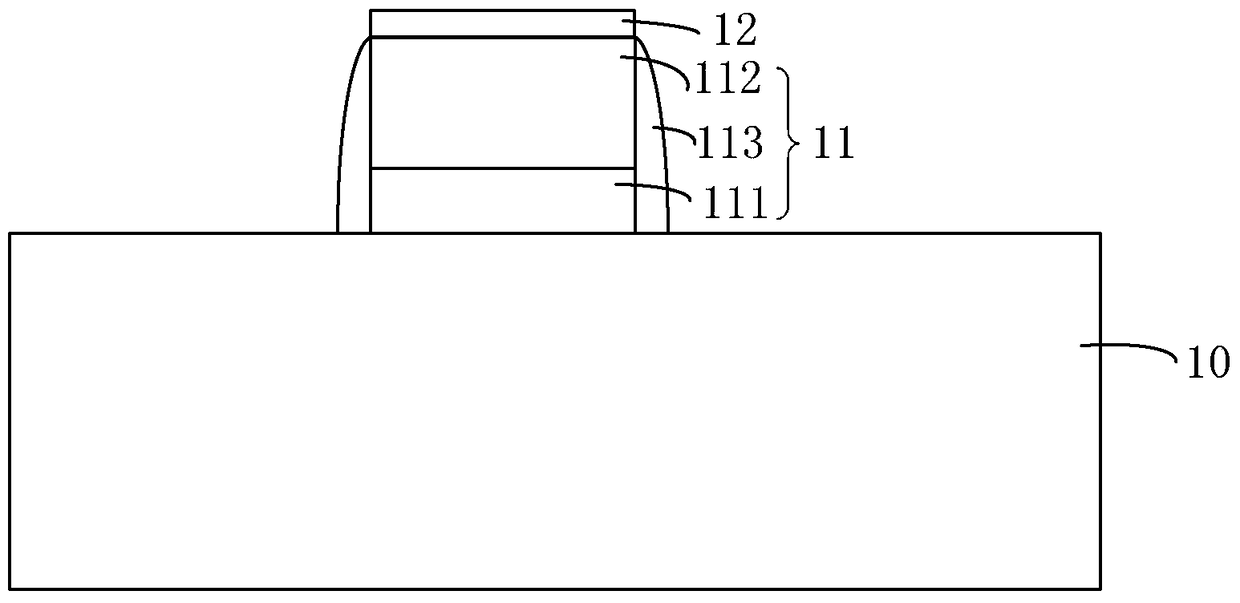

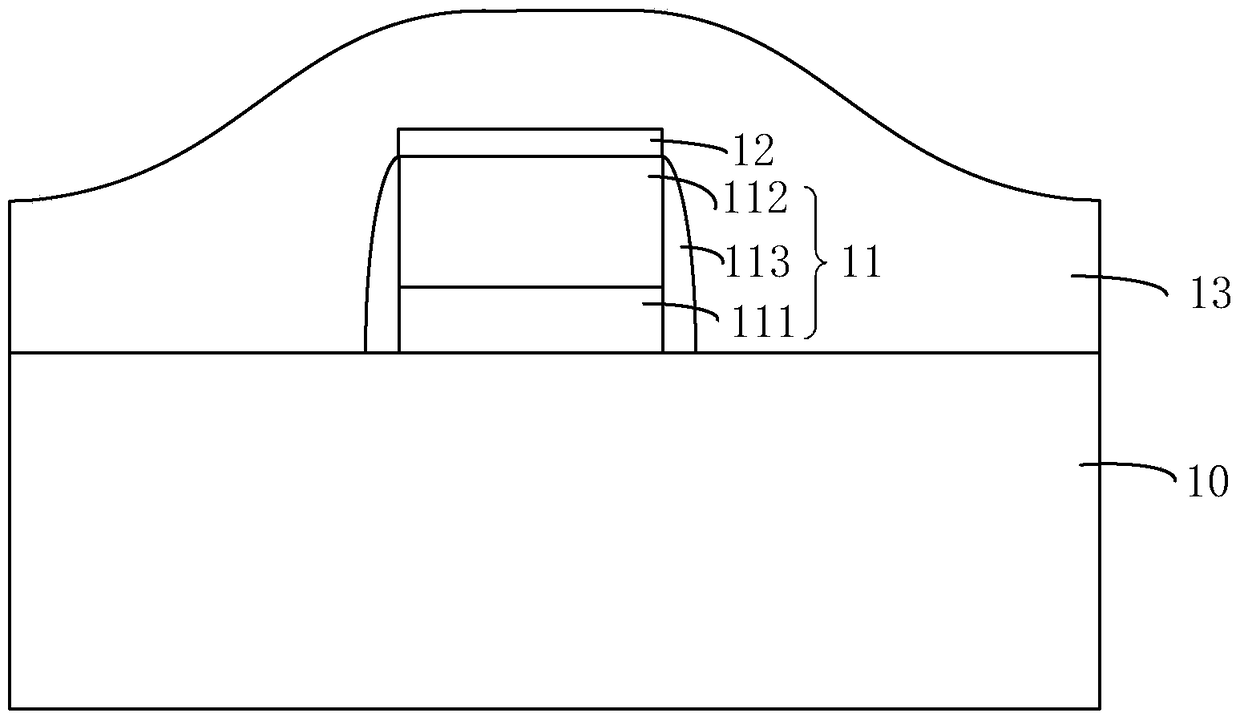

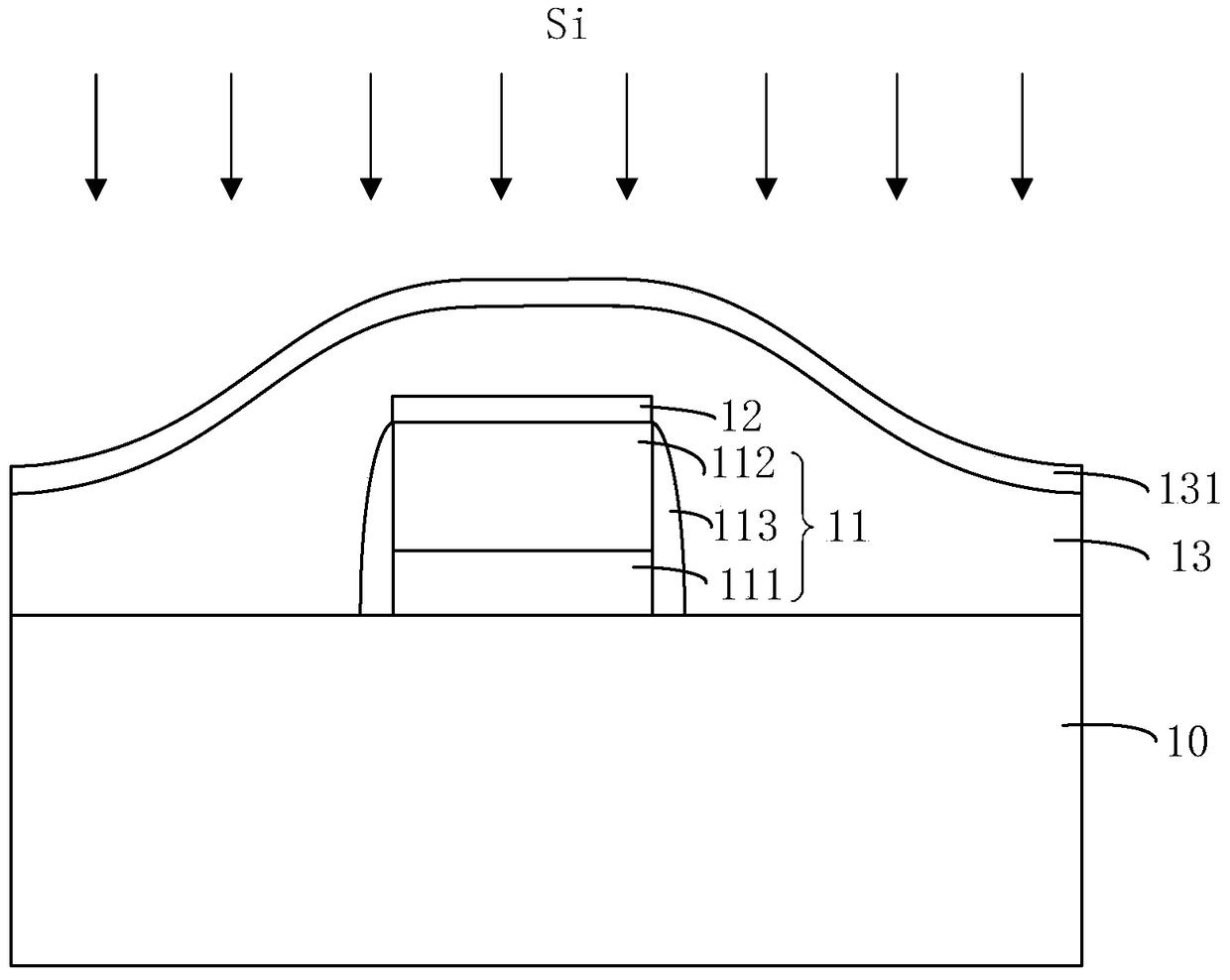

[0030] As mentioned in the background art, in the prior art, when the dielectric layer and surrounding hard materials are simultaneously ground, dish-shaped depressions are prone to appear in the dielectric layer. If the above-mentioned dish-shaped depressions are filled with conductive materials, it will affect the semiconductor device reliability. In view of the above technical problems, the present invention proposes to form a first dielectric layer and a second dielectric layer on a semiconductor substrate having a gate structure and an active region in two stages, wherein, after the formation of the first dielectric layer is completed, Implant silicon ions in it to form a silicon-doped layer, and then form a second dielectric layer on the silicon-doped layer; then grind the second dielectric layer and the first dielectric layer in two stages, the first stage is based on the gate structure The silicon-doped layer on the top is the grinding end point. For the second dielect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com