Preparation method of semiconductor structure

A semiconductor and reactive gas technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of excessive grinding time, different grinding rates, active area damage, etc., to reduce the amount of grinding and improve the surface Uniformity, the effect of reducing the damage of the active area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

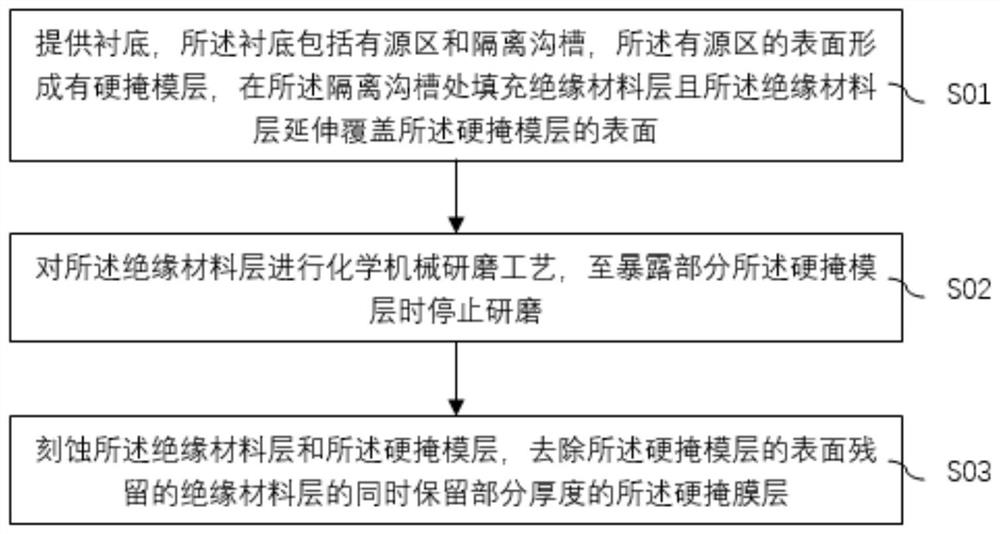

[0027] image 3 For a preparation method of a semiconductor structure provided by an embodiment of the present invention, refer to image 3 It can be seen that the method for preparing the semiconductor structure provided in this embodiment includes:

[0028] Step S01: providing a substrate, the substrate includes an active region and an isolation trench, a hard mask layer is formed on the surface of the active region, an insulating material layer is filled at the isolation trench, and the insulating material a layer extending over a surface of the hard mask layer;

[0029] Step S02: performing a chemical mechanical polishing process on the insulating material layer, and stopping polishing when a part of the hard mask layer is exposed;

[0030] Step S03: Etching the insulating material layer and the hard mask layer, removing the remaining insulating material layer on the surface of the hard mask layer while retaining a partial thickness of the hard mask layer.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com