Bulk silicon processing technology based on silicon wafer scribing

A processing technology, a technology of silicon wafers, applied in the process of producing decorative surface effects, metal material coating process, decorative arts, etc., can solve the problem of difficulty in obtaining sidewall roughness and verticality, staying, processing difficulties, etc. To eliminate the load effect, increase the sensitive mass, and improve the selection ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0044] Silicon wafer thickness: 500μm, equal line width design groove width 100μm.

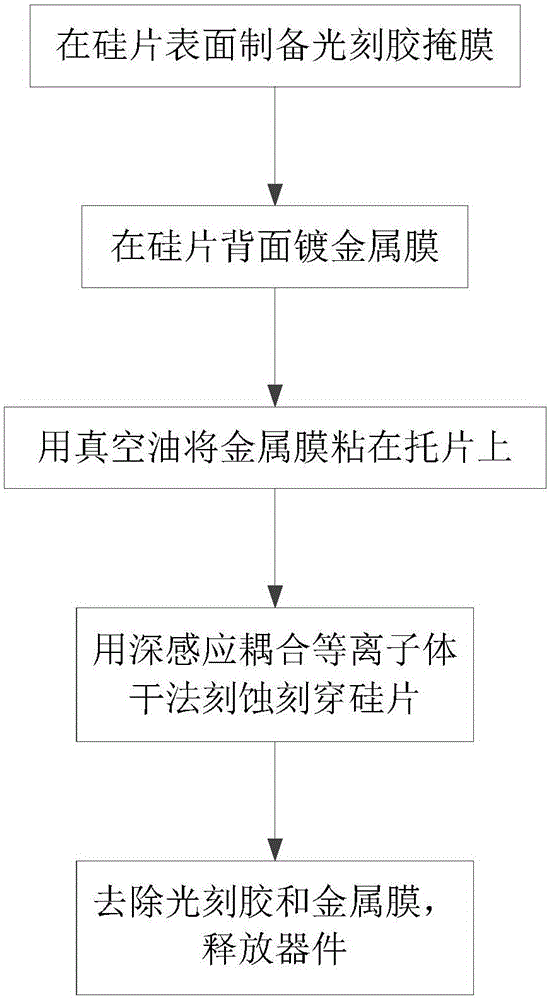

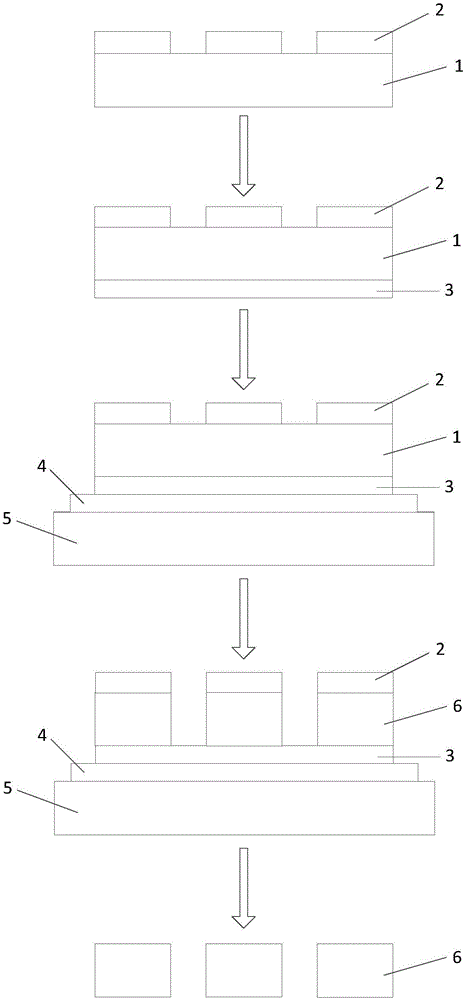

[0045] The bulk silicon processing technology based on silicon wafer lithography includes the following steps:

[0046] (1) Design equal etching groove width for the mask pattern of the device to be processed, and prepare a patterned photoresist mask on the surface of the silicon wafer. Further include the following steps:

[0047] (1-1) Carry out organic washing and pickling on the silicon wafer.

[0048] (1-2) After drying the water on the hot plate, evenly distribute the Az9260 photoresist, the rotation speed is 1500r / min, and the thickness of the photoresist is 8μm.

[0049] (1-3) Pre-bake at 120°C for 3 minutes.

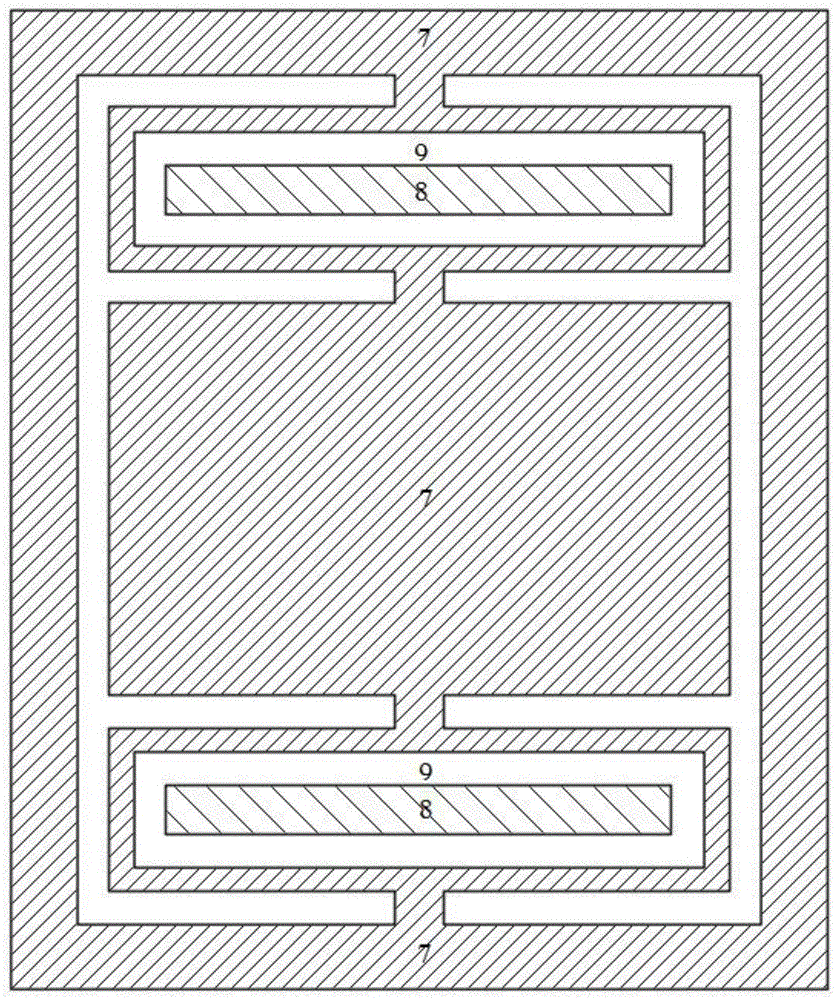

[0050] (1-4) Use a laser direct writing lithography machine to perform photolithography, equal to the width of the etching groove, such as image 3 As shown, the dose is 3000mj / cm 2 , the defocus amount is -0.006mm.

[0051] (1-5) Develop with a mixture of Az400k developer...

Embodiment 2

[0074] Silicon wafer thickness: 350μm, equal line width design slot width: 50μm.

[0075] The bulk silicon processing technology based on silicon wafer lithography includes the following steps:

[0076] (1) Design equal etching groove width for the mask pattern of the device to be processed, and prepare a patterned photoresist mask on the surface of the silicon wafer. Further include the following steps:

[0077] (1-1) Carry out organic washing and pickling on the silicon wafer.

[0078] (1-2) After drying the water on the hot plate, evenly distribute the Az9260 photoresist, the rotation speed is 2500r / min, and the thickness of the photoresist is 5μm.

[0079] (1-3) Pre-bake at 120°C for 3 minutes.

[0080] (1-4) Use a laser direct writing lithography machine to perform photolithography, equal to the width of the etching groove, such as image 3 Shown, the dose is 2300mj / cm 2 , the defocus amount is -0.006mm.

[0081] (1-5) Develop with a mixture of Az400k developer and ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com