Passivation layer dry etching method

A dry etching and passivation layer technology, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of increased leakage current of gate oxide layer, damage of gate oxide layer, increase of turn-on voltage and current, etc. , to achieve the effect of reducing PID and reducing physical bombardment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

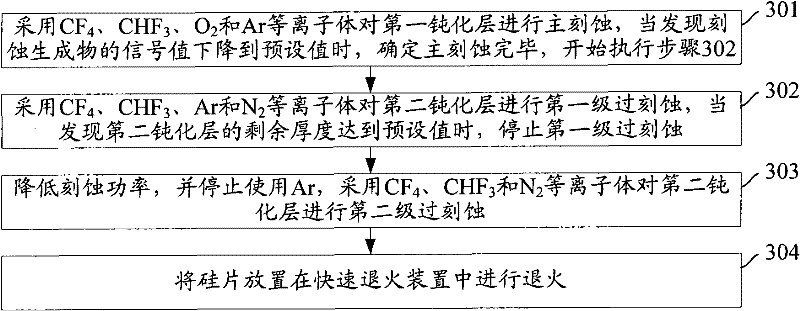

[0043] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

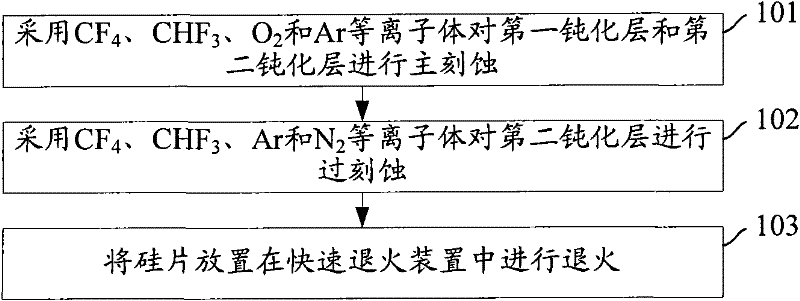

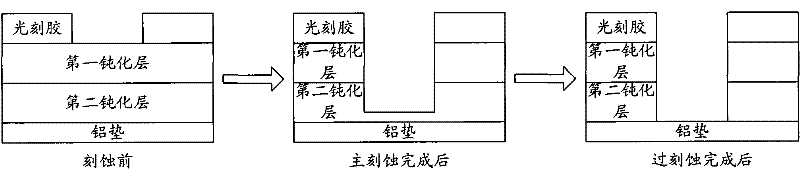

[0044] image 3 The flow chart of the passivation layer dry etching method provided by the embodiment of the present invention, in this embodiment, the first and second passivation layers are located above the aluminum pad, and the second passivation layer is located below the first passivation layer, as shown in image 3 As shown, the specific steps are as follows:

[0045] Step 301: Adopt CF 4 、CHF 3 , O 2 Perform main etching on the first passivation layer with Ar plasma, and when it is found that the signal value of the etching product drops to a preset value, it is determined that the main etching is completed, and step 302 is started.

[0046] Among them, the pressure of the etching chamber is usually: 15-250mt, the etching power is usually: 500-3500w, CF 4The flow rate is usually: 20-300sccm, CHF 3 The flow rate is usuall...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com