High-reliability TSV (Through Silicon Via) technique based on SOI (Silicon-On-Insulator) substrate

A process method and reliability technology, applied in the field of microelectronics, can solve the problems affecting the performance and reliability of SOI three-dimensional integrated devices, difficult metallization of through holes, and increased leakage, so as to achieve high reliability, improve performance, and increase reliability. sexual effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

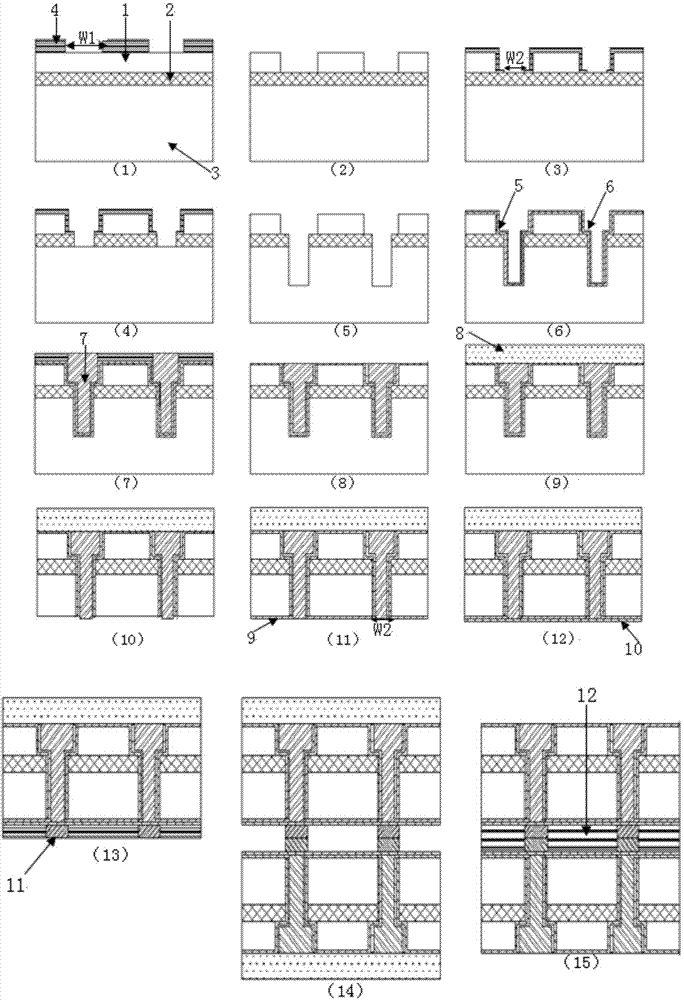

Embodiment 1

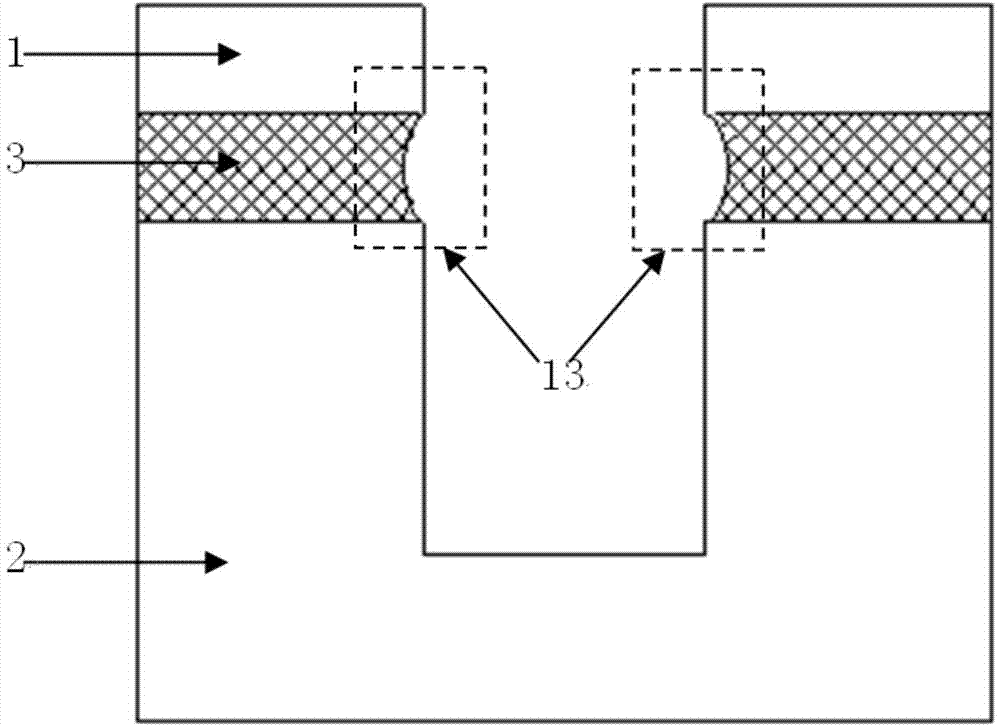

[0033] The SOI wafer substrate used is P-type silicon, and the silicon dioxide buried oxide layer is 3 thick Top Silicon 1 Thickness

[0034] (1) Coating on the surface of SOI substrate The photoresist 4 is exposed and developed to expose the window that needs to be etched on the top layer of silicon 1. The window is circular and the diameter W1 is 30 μm;

[0035] (2) Etching the top layer silicon 1 to the silicon dioxide buried oxide layer 3 stops at the window W1, and the etching depth is Then use SPM (H2SO4:H2O2:H2O=5:1:1) solution to clean and remove the photoresist 4 on the surface of the SOI wafer;

[0036] (3) Re-coat the surface of the SOI wafer with a thickness of The photoresist 4 is exposed and developed to expose the window where the silicon dioxide buried oxide layer 3 needs to be etched. The window is circular and the diameter W2 is 15 μm;

[0037] (4) Etch the silicon dioxide buried oxide layer 3 at the diameter W2 window until the upper surface of the...

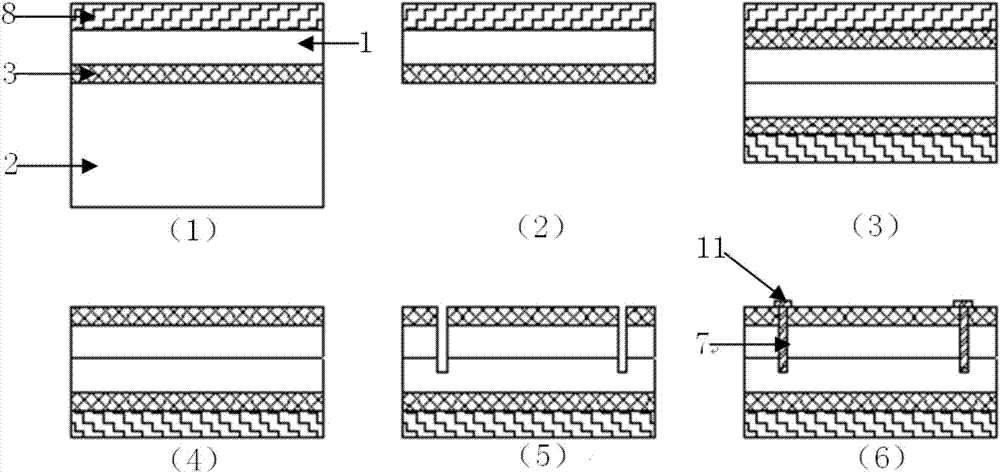

Embodiment 2

[0050] The SOI wafer substrate used is P-type silicon, and the silicon dioxide buried oxide layer is 3 thick Top Silicon 1 Thickness

[0051] (1) Coating on the surface of SOI substrate The photoresist 4 is exposed and developed to expose the window that needs to be etched on the top layer of silicon 1. The window is circular and the diameter W1 is 15 μm;

[0052] (2) Etching the top layer silicon 1 to the silicon dioxide buried oxide layer 3 stops at the window W1, and the etching depth is Then use SPM (H2SO4:H2O2:H2O=5:1:1) solution to clean and remove the photoresist 4 on the surface of the SOI wafer;

[0053] (3) Re-coat the surface of the SOI wafer with a thickness of The photoresist 4 is exposed and developed to expose the window where the silicon dioxide buried oxide layer 3 needs to be etched. The window is circular and the diameter W2 is 15 μm;

[0054] (4) Etch the silicon dioxide buried oxide layer 3 at the diameter W2 window until the upper surface of the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com