Volume rendering on shared memory systems with multiple processors by optimizing cache reuse

A shared memory and processor technology, applied in the field of image processing, can solve the problem that the drawing load will not be evenly distributed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0212] refer to figure 1 , describes a volume rendering system, which includes an image acquisition system, such as a CT system or an MRT system, etc., and the image acquisition system is in figure 1 Indicated with the reference character CT. The modality is coupled to a server system via a network NW for images or volumetric rendering to be displayed on a monitor M.

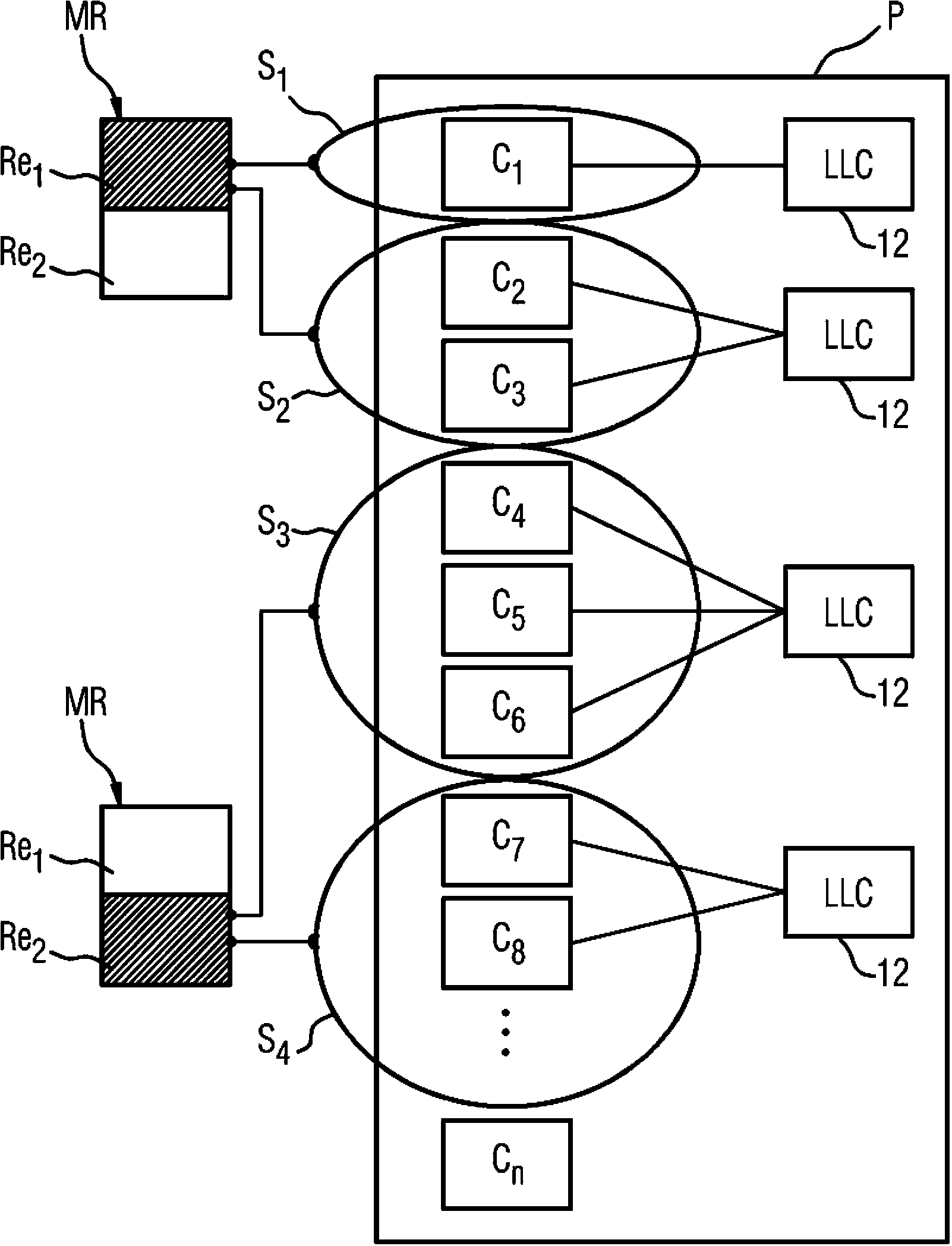

[0213] figure 2 Shown is a rendering system 10 comprising several processors P 1 ,P 2 ,...P n . Generally, each processor P may include one or more processor cores C 1 、C 2 ,... C n , so it is called a multi-core system. Each core C accesses a cache 12 or a cache hierarchy having several caches 12 with different access properties. As multi-core processors become common and the number of on-die cores increases, a key processor design issue is for the on-die last-level cache LLC and thus for the algorithm with an efficient cache hierarchy in mind Hierarchy and strategy to reduce off-chip data misses an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com