Graphene field effect transistor

A field-effect transistor and graphene technology, which is applied in the direction of transistors, semiconductor devices, electrical components, etc., can solve the problems of reduced mobility, difficult performance, and low device efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

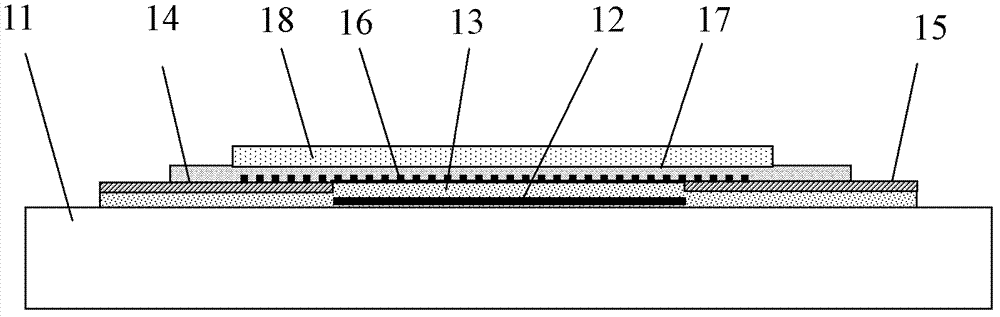

[0028] Bottom gate structure, the substrate is a semi-insulating silicon wafer, on which the metal chromium-palladium composite thin film gate is first prepared, and then the aluminum oxide / strontium barium fluoride insulating layer is prepared, wherein the thickness of aluminum oxide is 50 nanometers, and the thickness of strontium fluoride is 10 nanometers . Barium strontium fluoride is lattice-matched with graphene, and a single layer of graphene is deposited on it by CVD method, and the source and drain are prepared simultaneously. Graphene is passivated in an isochlorine plasma, and then a semiconductor layer of zirconium nitride and a protective layer of aluminum oxide are deposited on it to form a complete device.

Embodiment 2

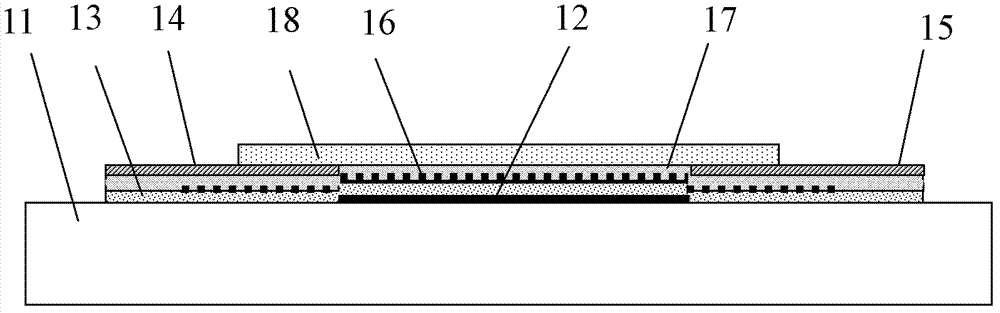

[0030] Bottom gate structure, the substrate is a semi-insulating silicon wafer, on which a metal chromium-gold composite thin film gate is first prepared, and then an aluminum oxide / hafnium oxide insulating layer is prepared, wherein the thickness of aluminum oxide is 20 nanometers, and the thickness of hafnium oxide is 10 nanometers. Single-layer graphene is deposited on hafnium oxide by CVD method, and the source and drain are prepared simultaneously. Graphene was passivated in a bromine plasma, and then a semiconductor layer of cadmium sulfide and a protective layer of aluminum oxide were deposited on it to form a complete device.

Embodiment 3

[0032] Top-gate structure, the substrate is an insulating silicon carbide wafer, on which an n-type silicon semiconductor layer is first prepared, and a single-layer graphene is prepared on a copper foil by CVD, and then transferred to the n-type silicon semiconductor layer and subjected to hydrogenation treatment. After the metal source and drain are prepared, a hafnium oxide / alumina insulating layer is prepared, wherein the thickness of aluminum oxide is 20 nanometers, and the thickness of hafnium oxide is 6 nanometers. Finally, the top gate is prepared to form a complete device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com