Air gap forming method between integrated circuit (IC) interconnector and interlevel dielectric layer

A technology of interlayer dielectric layer and air space, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as limiting operating speed, and achieve the effect of reducing RC delay, speeding up signal transmission, and reducing the effect of capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

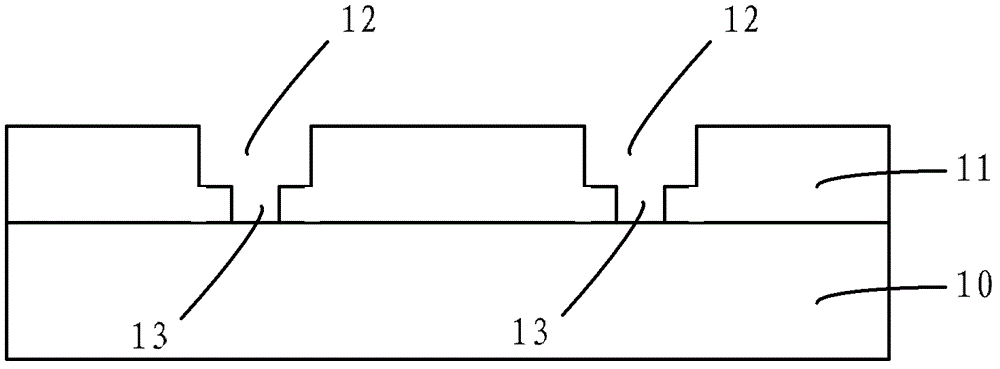

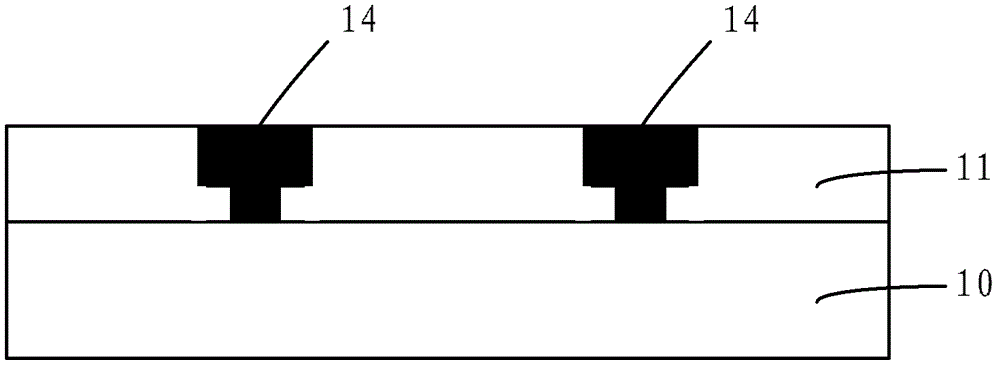

[0035] The steps of the content of the present invention are as Figure 4 shown, refer to Figure 4 and Figure 5 to Figure 13 As shown, the implementation process of the specific embodiment includes the following contents.

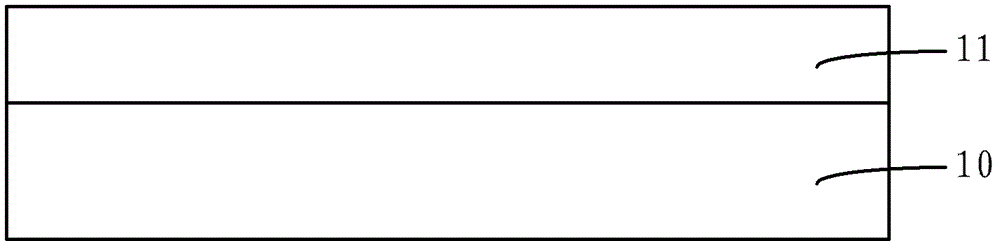

[0036] Step 1: If Figure 5 As shown, a semiconductor device 10 such as CMOS is provided, and a first dielectric barrier layer (dielectric barrier) 15 and an interlayer dielectric layer 11 are sequentially formed on the semiconductor device 10 .

[0037] Wherein, the first dielectric barrier layer 15 is made of silicon nitride carbide material, and the thickness can be It is formed by plasma enhanced chemical vapor deposition (PECVD, Plasma Enhanced Chemical Vapor Deposition). The functions of the first dielectric barrier lay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com