Electrostatic discharge protection device

An electrostatic discharge, ESD protection technology, applied in circuit devices, emergency protection circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, etc., can solve problems such as affecting RF input matching and reducing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

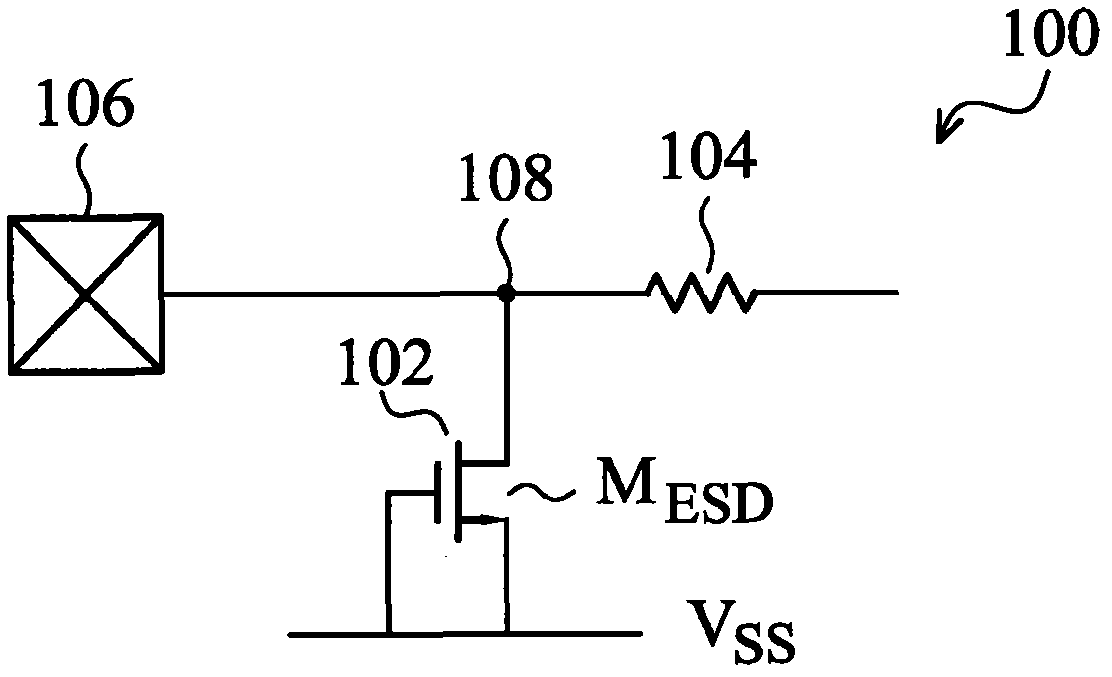

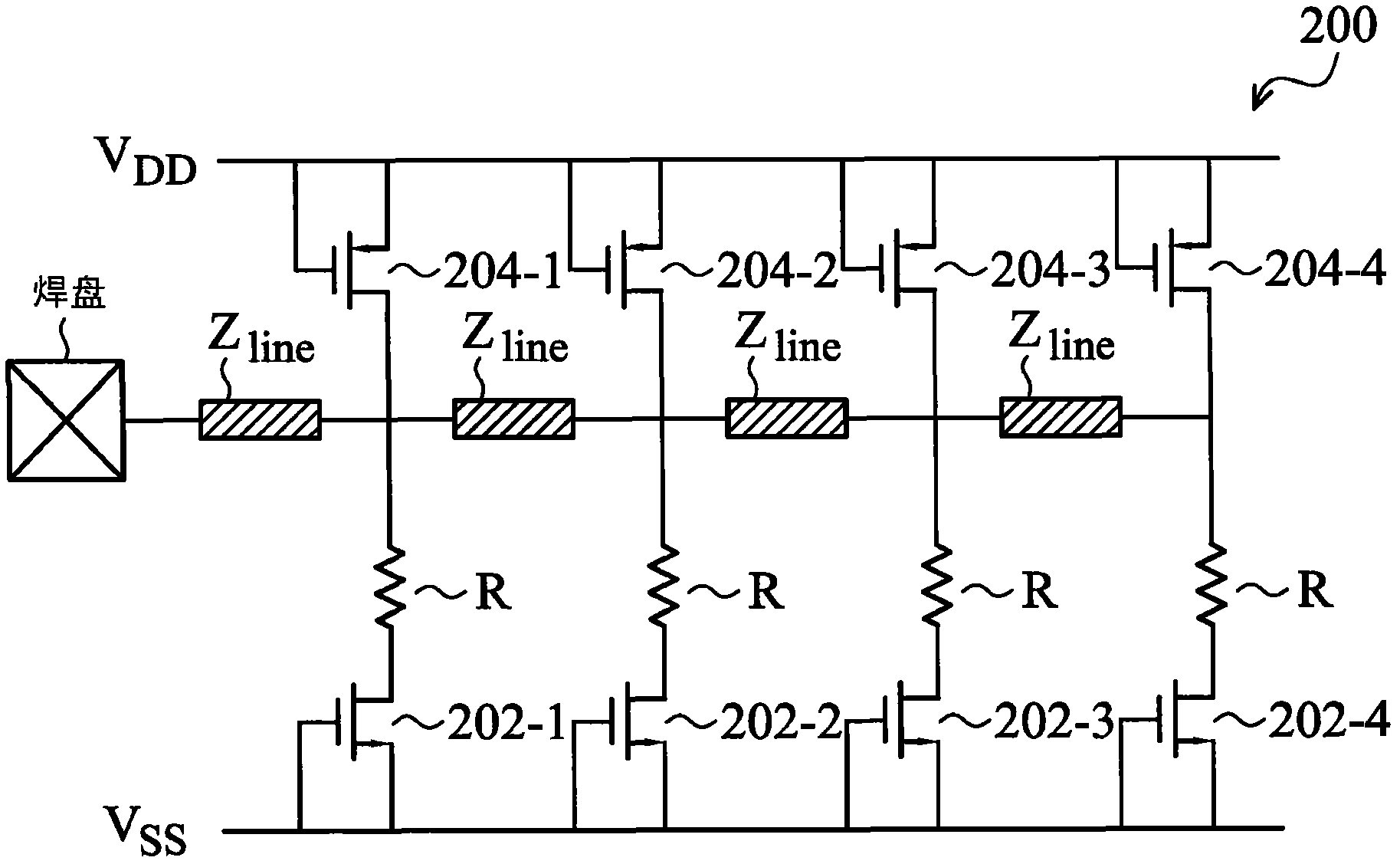

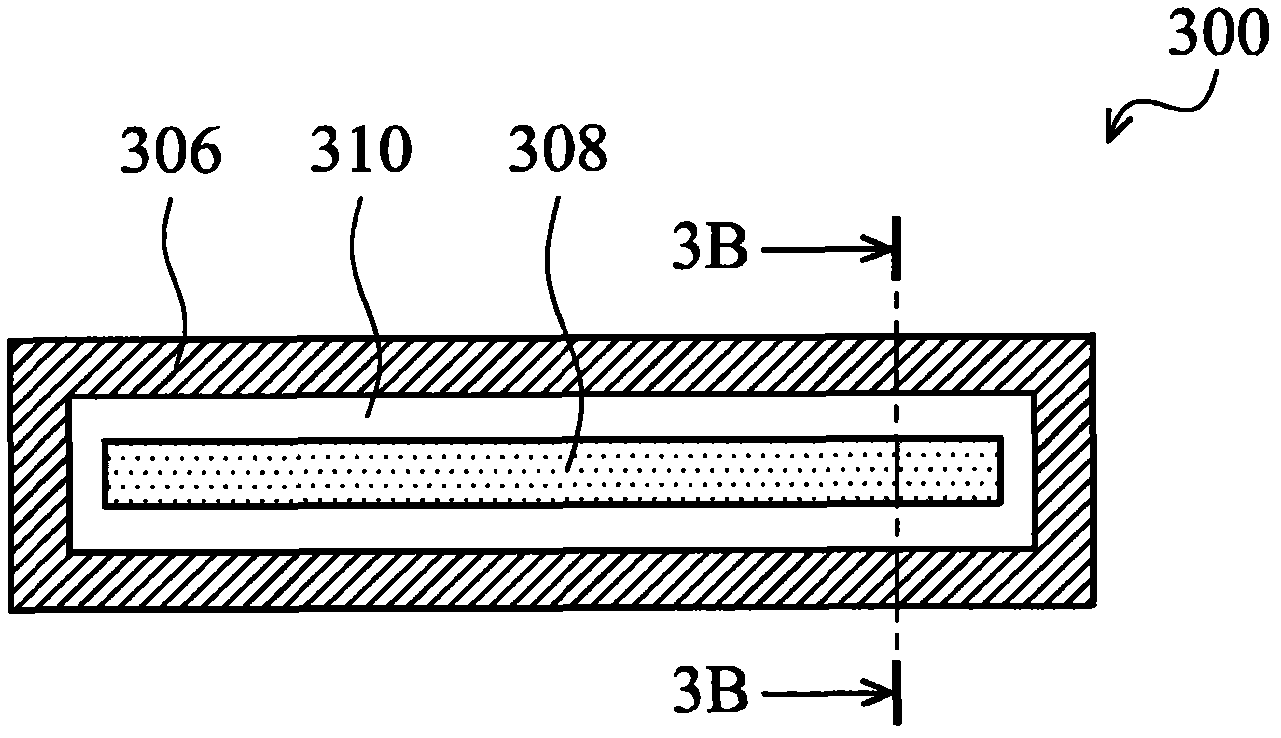

[0048] The invention discloses an improved electrostatic discharge (ESD) protection device for radio frequency applications. ESD protection devices include junction varactors that act as voltage-dependent capacitors when reverse biased. The bias voltage of the junction varactor may be optimized to minimize capacitance to reduce the capacitive effects of network matching during normal RF operation. During an ESD event, the junction varactor is forward biased and acts as an ESD protection diode to shunt the ESD current. In addition, the junction varactor provides sufficient metal width and a sufficient amount of vias and contacts to avoid electromigration, and has a length-to-width (L / W) ratio that allows alignment with the bond pad edge, Compared with traditional ESD protection devices, it has improved circuit layout.

[0049] Figure 4A is a cross-sectional view of a junction varactor 400A for ESD protection for RF applications. like Figure 4A As shown, junction varactor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com