Wafer level chip size packaging structure and manufacturing method thereof

A wafer-level chip and size packaging technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of unfavorable chip cost reduction, complex packaging structure, and long production cycle, so as to increase market competition Capability, simple and easy manufacturing method, and cost-saving effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

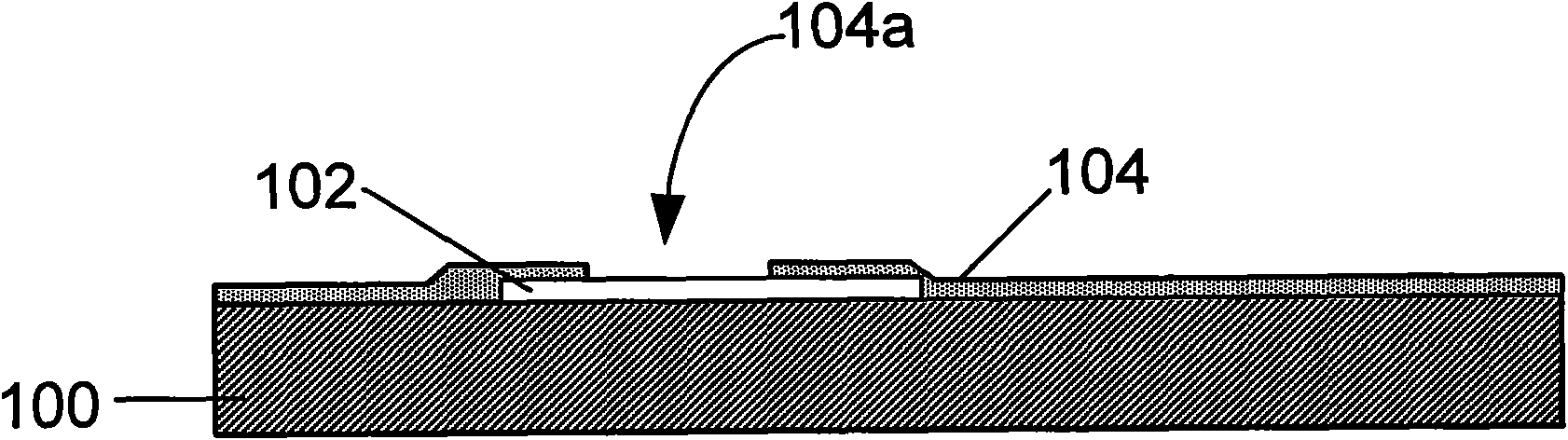

[0058] Figure 2A to Figure 2DIt is a schematic diagram of each step of the manufacturing method of the WLCSP structure according to an embodiment of the present invention.

[0059] The manufacturing method of the wafer-level chip size packaging structure of this embodiment includes:

[0060] Firstly, a wafer is provided, the wafer has pads thereon;

[0061] Such as Figure 2A As shown, the wafer includes: a substrate 200, a pad 202 located on the substrate 200, and a substrate passivation layer 204 partially covering the pad 202, and the substrate passivation layer 204 has an exposed portion The substrate passivation layer through hole 204a of the pad 202; wherein the material of the substrate 200 is silicon, and the material of the pad is aluminum; the substrate passivation layer 204 can be made of epoxy polymer ;

[0062] Secondly, the optical process of the redistribution layer 208 is performed;

[0063] Preferably, the material of the rewiring layer 108 is copper (Cu...

Embodiment 2

[0080] This embodiment illustrates another preferred method for manufacturing a wafer-level chip-scale package structure, including:

[0081] Step 1: provide the wafer;

[0082] The wafer includes: a substrate 200, a pad 202 located on the substrate 200, and a substrate passivation layer 204 partially covering the pad 202, and the substrate passivation layer on the pad 202 204 has a substrate passivation layer through hole 204a to expose part of the pad 202; wherein the material of the substrate 200 is silicon, and the material of the pad is aluminum;

[0083] Step 2: Preprocessing the wafer;

[0084] Step 3: performing photo-processing of the first passivation layer 206 on the wafer;

[0085] The first passivation layer 206 can be polyimide (PI), poly-p-phenylene benzobisoxazole (PBO) or photosensitive benzocyclobutene, and the photo process can be yellow light process;

[0086] Step 4: Etching the first passivation layer 206 to form a first passivation layer through hole ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com