Multi-pitch scatterometry targets

a scatterometry and target technology, applied in the field of substrate processing, can solve the problems of conventional metrology targets and techniques that do not provide the necessary parameter sensitivity required

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

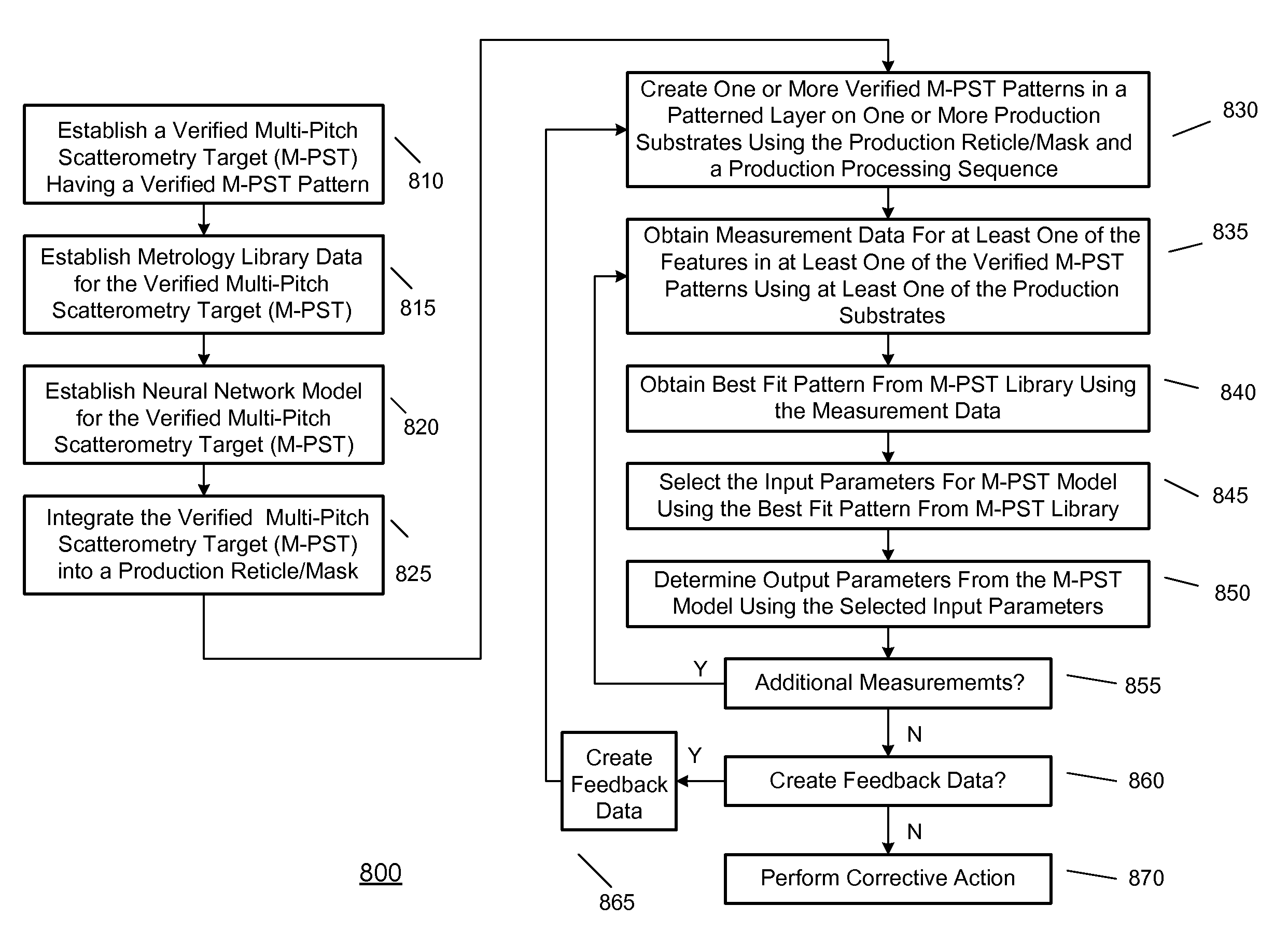

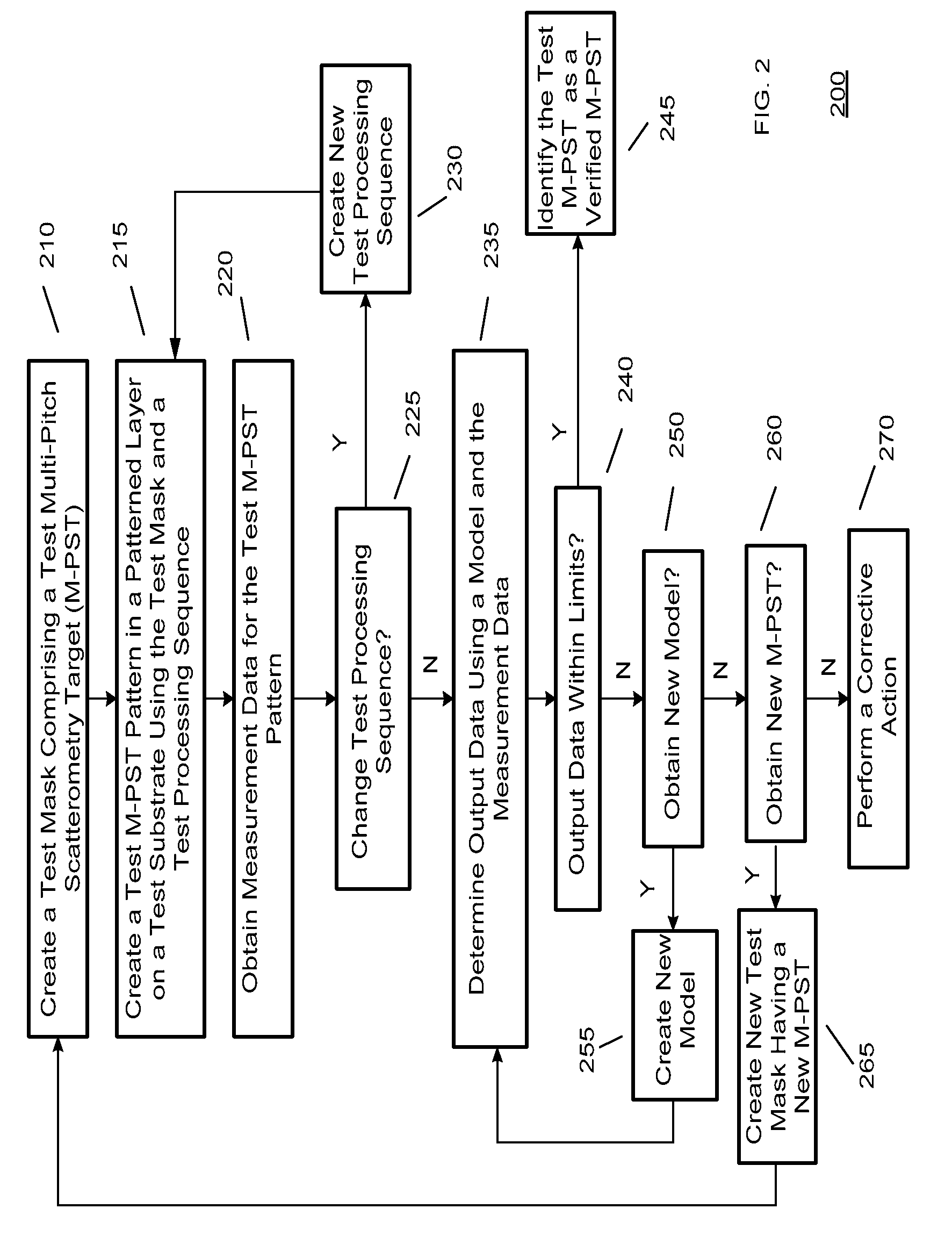

[0021]The invention can provide apparatus and methods of processing a substrate using multi-pitch scatterometry targets (M-PSTs) that have critical dimension (CD) and sidewall angle (SWA) sensitivity to exposure focus variations, exposure dose variations, and post exposure bake (PEB) temperature variations. In addition, the CD and SWA data can be de-convolved so that the individual measurement process variable contributors can be identified. The M-PSTs can be used in Double-Patterning (D-P) processing sequences, Double-Exposure (D-E) processing sequences, or Single-Patterning (S-P) processing sequences, or any combination thereof to control transistor structures. The S-P, D-P, and / or D-E processing sequences can include one or more lithography-related procedures, one or more scanner-related procedures, one or more etch-related procedures, one or more deposition-related procedures, one or more measurement-related procedures, or one or more inspection-related procedures, or any combin...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| sizes | aaaaa | aaaaa |

| wavelength | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com