Cleaning solution formulations for substrates

a technology of cleaning solution and substrate, which is applied in the direction of detergent composition, cleaning using liquid, inorganic non-surface active detergent composition, etc., can solve the problems of dielectric breakdown (tddb), copper (cu) wire interface, and the inability to obtain reliable semiconductor devices, etc., to achieve the effect of improving device reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example 1

[0076]A patterned wafer is exposed to cleaning solution to remove copper oxide from the surface then rinsed and dried. Subsequently, the wafer is exposed to toluene trimethoxy silane vapor for 300 seconds at room temperature, followed by i-propanol and DI rinse. After these steps, the wafer either undergoes further cleaning step(s) or subjected to electroless deposition followed by post-clean, if needed, then rinse and dry. The surface obtained in this manner retains a strongly hydrophobic character even after the entire deposition process. In most cases, the contact angle of the surface is higher after the full process with silane treatment than the non-processed wafer. In the absence of silane treatment, the contact angle is significantly lower than that of the non-processed wafer. This statement is valid for silicon oxide or other silicon oxide containing dielectric materials such as Black Diamond.

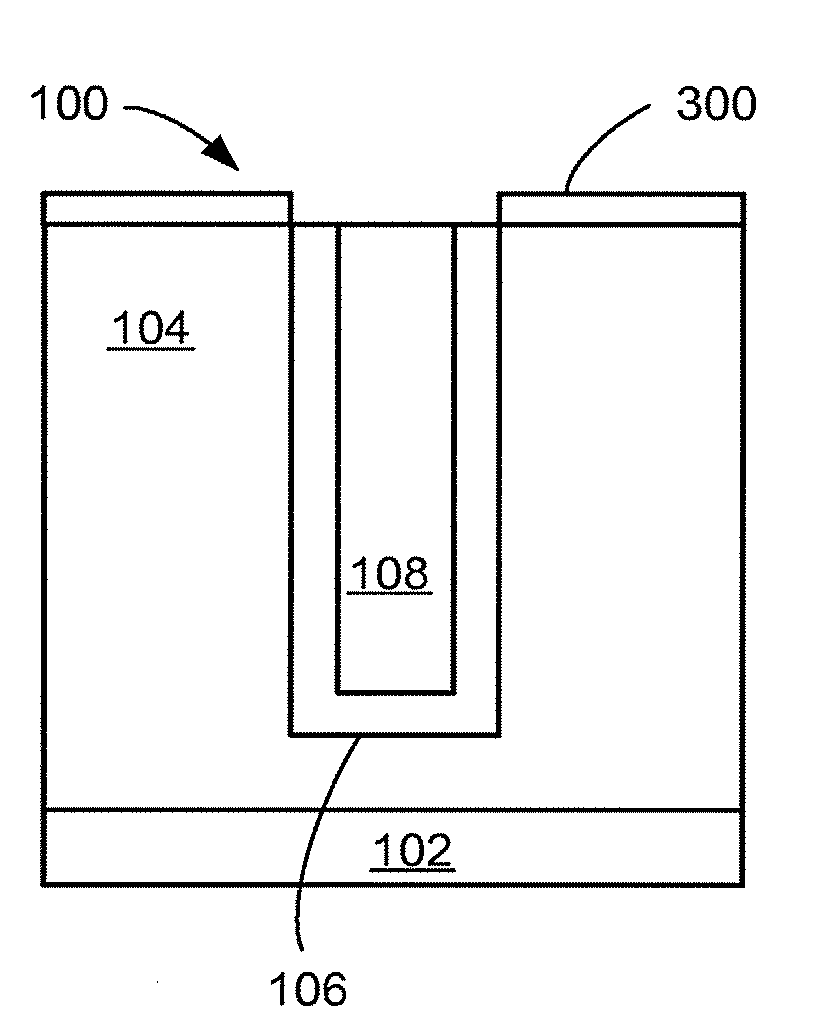

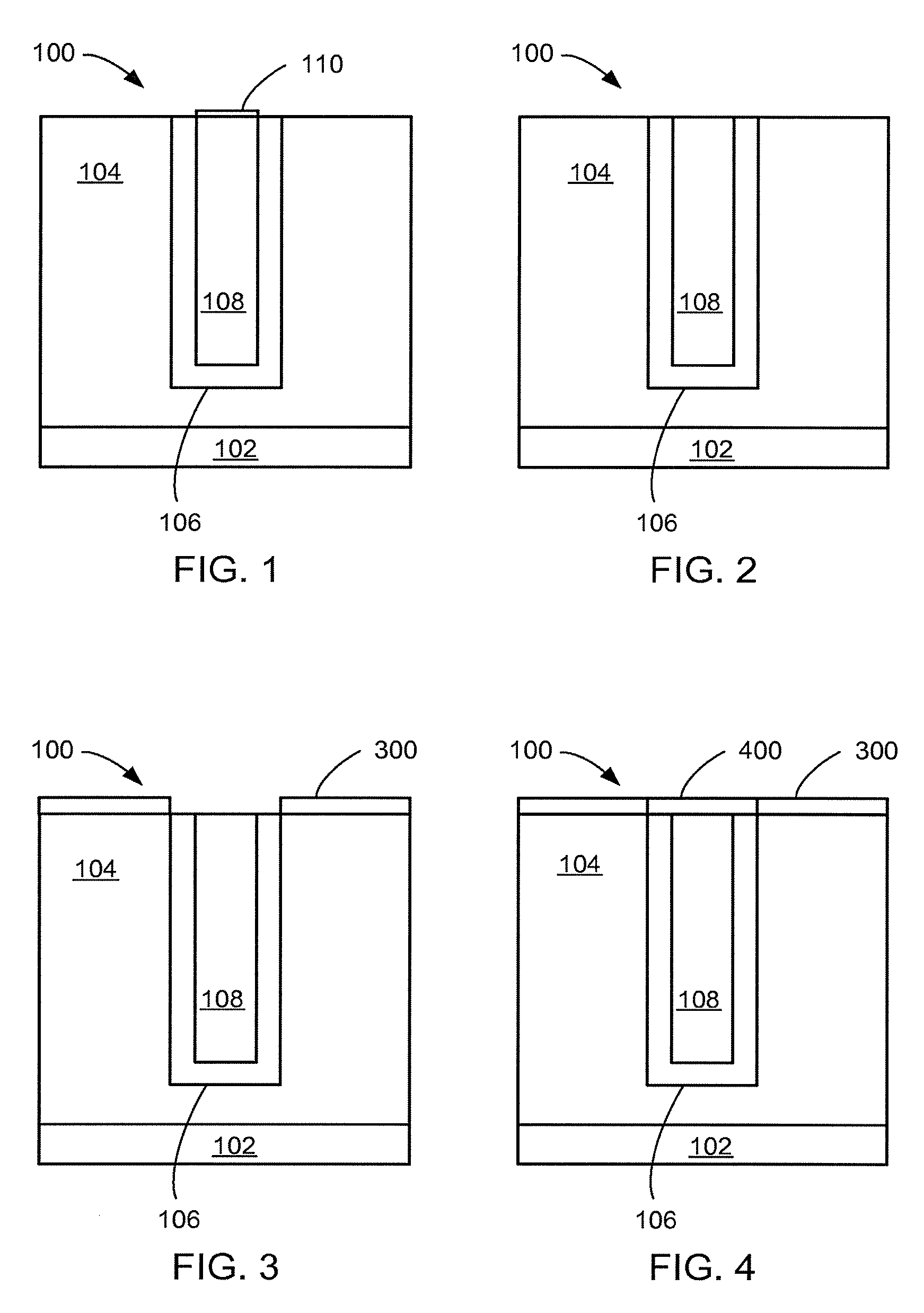

[0077]Referring now to FIG. 1, therein is shown a close up view of a semiconductor ...

example 2

[0089]After depositing the capping layer and rinsing the wafer surface to remove deposition solution the wafer is subjected to scrubbing to remove contaminant from the surface. The scrubbing solution contains a corrosion inhibitor (i.e. a triazole compound such as toluol triazole, benzotriazole) an oxygen scavenger (i.e. L-ascorbic acid), and a complexing agent, which also serve as pH adjustor for the cleaning solution. One such pH adjustor is oxalic acid. The pH of this solution is between 1.5 to 2.0. The concentration of inhibitor is between 0.1 to 10000 ppm, most preferably 100 to 2000 ppm. The oxygen scavenger concentration is between 0 to 10000 ppm, most preferably between 1000 to 5000 ppm. The oxalic acid concentration is between 2 to 50 g / L, most preferably between 5 to 15 g / L.

[0090]The steps of the method in accordance with embodiments of the present invention are:

[0091]1. Moisture removal by different drying methods after forming metal or metal alloy cap on Cu structures:[0...

PUM

| Property | Measurement | Unit |

|---|---|---|

| concentration | aaaaa | aaaaa |

| concentration | aaaaa | aaaaa |

| dielectric constants | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com