Method for producing alignment mark

A technology of alignment marks and manufacturing methods, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of difficult allocation of alignment marks, neglect, and increased wafer area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

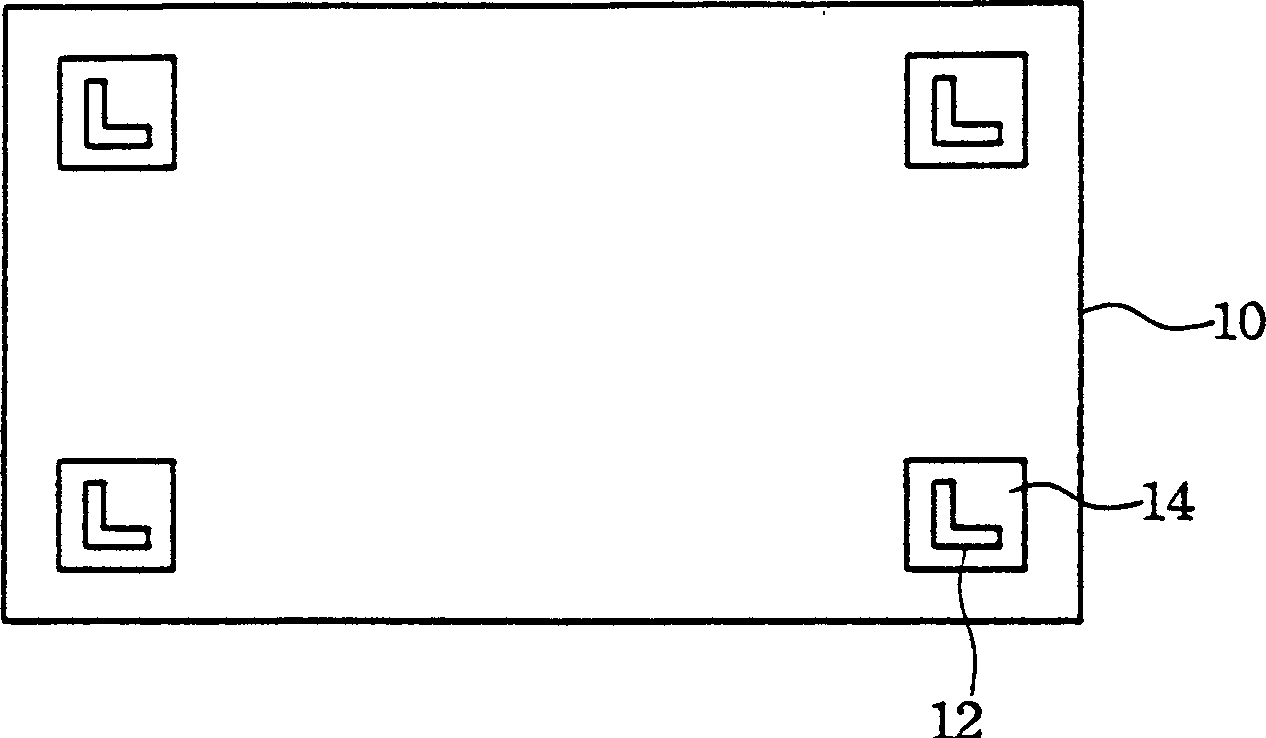

[0026] From the above-mentioned known methods of manufacturing alignment marks for laser repair calibration, it can be seen that the alignment marks are made in the wafer and the area of the wafer will be increased. Lines, optical scales, critical dimension bars, overlay patterns, and lithographic alignment marks overlap, so placement of the alignment marks is limited, creating dispensing headaches.

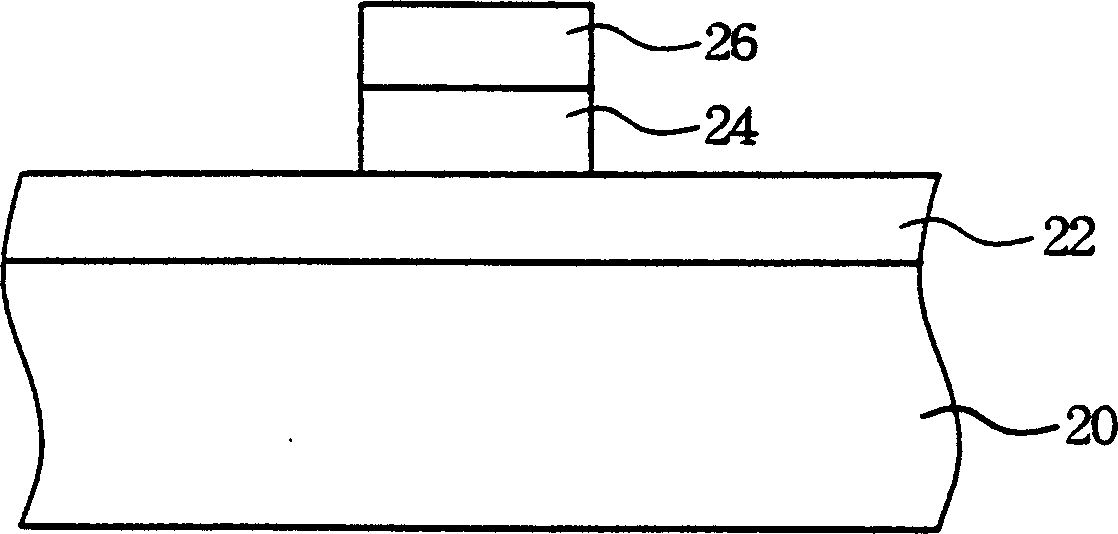

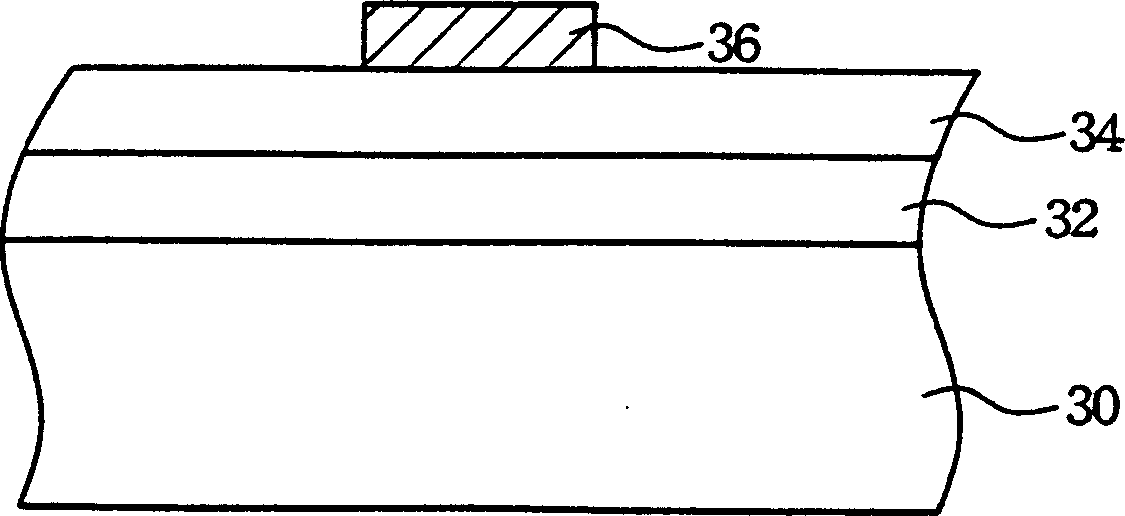

[0027] In order to reduce the wafer area and avoid the trouble caused when assigning the position of the alignment mark, the alignment mark can be made above the upper metal layer, and a dielectric layer is added between the alignment mark and the upper metal layer to prevent The occurrence of electrical short circuit. Please refer to this structure figure 2 , which is covered with a first metal layer 22 on the substrate 20 that has been formed with a plurality of semiconductor material layers, wherein the first metal layer 22 can be, for example, the upper metal layer of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com