Effective critical area parameter vector set reordering method and system

A key area and parameter vector technology, which is applied in the reordering method and system field of the effective key area parameter vector set, can solve the problems of low test efficiency, high integrated circuit test cost, and low test accuracy, so as to reduce test cost and improve Test efficiency and the effect of reducing test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

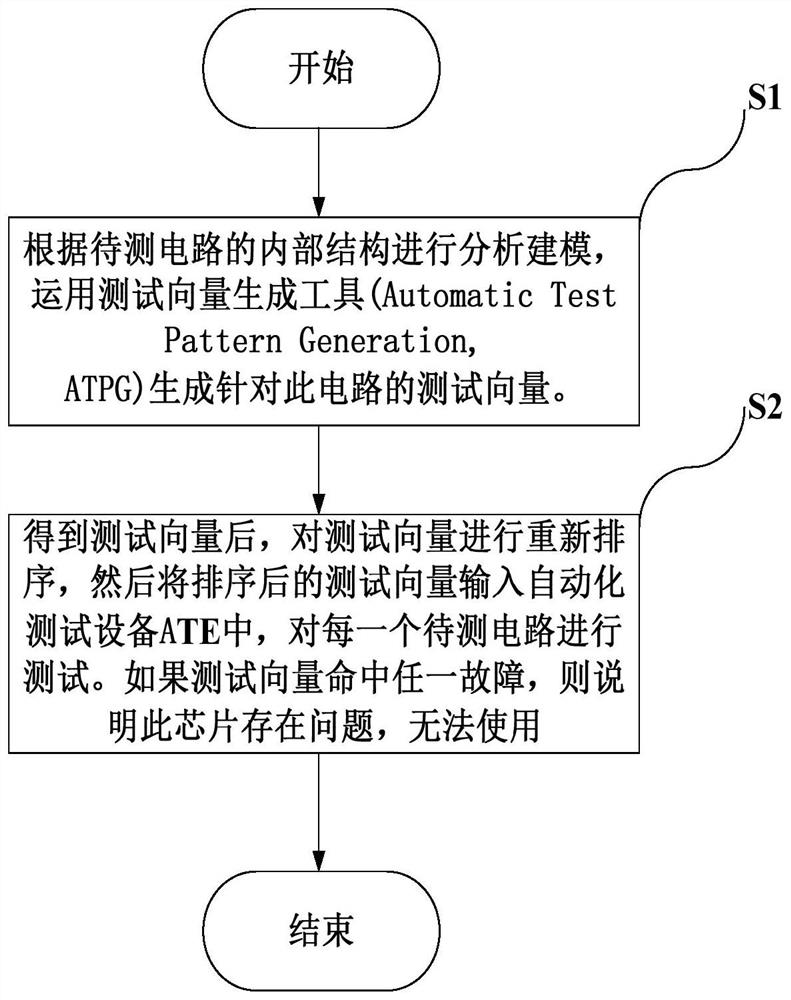

[0056] For integrated circuit testing, the main process is as follows:

[0057] S1. Perform analysis and modeling according to the internal structure of the circuit to be tested, and use a test vector generation tool (Automatic Test Pattern Generation, ATPG) to generate a test vector for the circuit. In this process, try to ensure that the circuit achieves a higher fault coverage rate.

[0058] S2. After the test vector is obtained, refer to the structure diagram of the tested integrated circuit to calculate the total critical area of transistors in different unit circuits relative to the area coverage of the unit circuit. During the test process, each test vector hits the corresponding unit according to the statistics The number of circuit failures is estimated, the test characteristic value of each test vector is estimated, the original test set is reordered, and the sorted test vector set is input into the automated test equipment ATE to test each circuit to be tested. I...

Embodiment 2

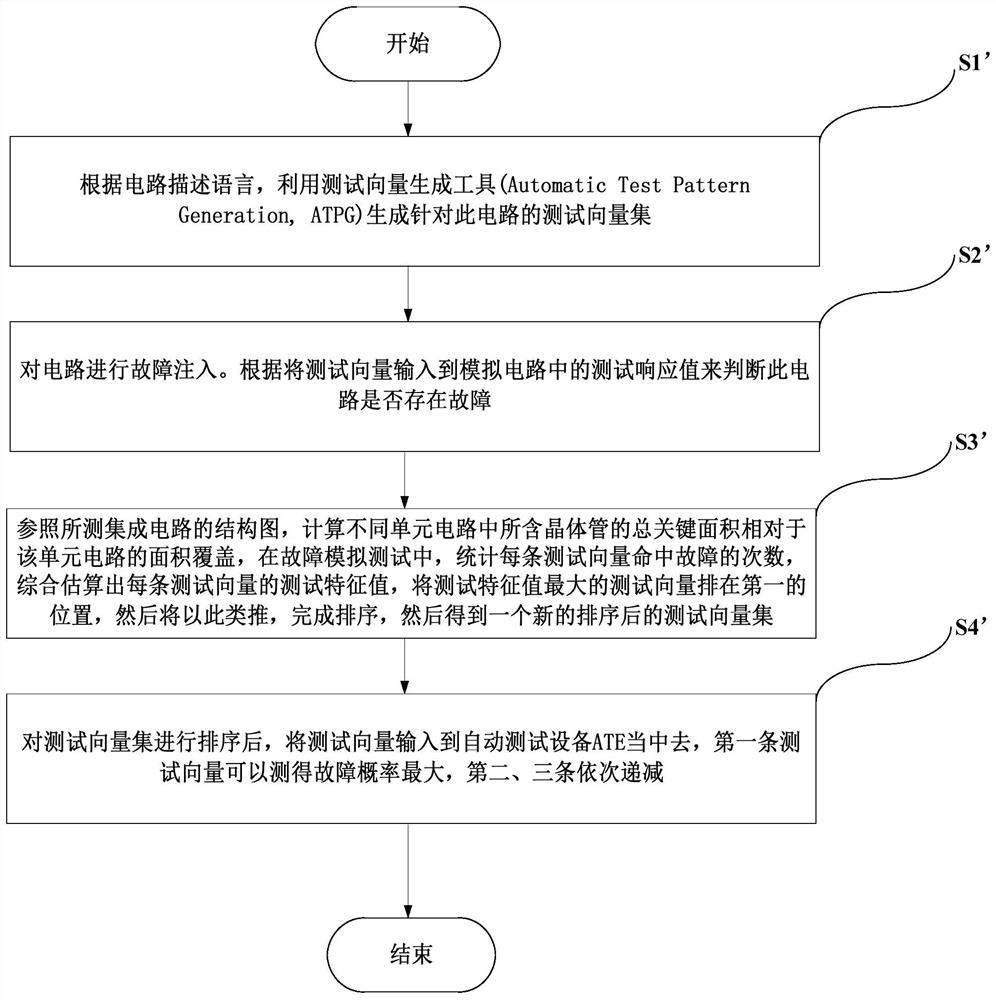

[0064] S1', according to the circuit description language, use a test vector generation tool (Automatic Test Pattern Generation, ATPG) to generate a test vector set for the circuit.

[0065] S2', perform fault injection on the circuit. According to the test response value inputting the test vector into the analog circuit, it is judged whether the circuit has a fault.

[0066] S3', referring to the structure diagram of the tested integrated circuit, calculate the total critical area of the transistors contained in different unit circuits relative to the area coverage of the unit circuit, and in the fault simulation test, count the number of times that each test vector hits the fault, and comprehensively The test eigenvalues of each test vector are estimated, and the test vector with the largest test eigenvalue is ranked first, and then by analogy, the sorting is completed, and a new sorted test vector set is obtained.

[0067] S4'. After sorting the test vector set, input ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com