Insulated gate bipolar transistor

A technology of bipolar transistors and insulated gates, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as weakening device direction recovery performance, difficulty in manufacturing process control, and reducing on-resistance, so as to suppress minority carrier injection and reduce high-frequency power. power consumption and reduce on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

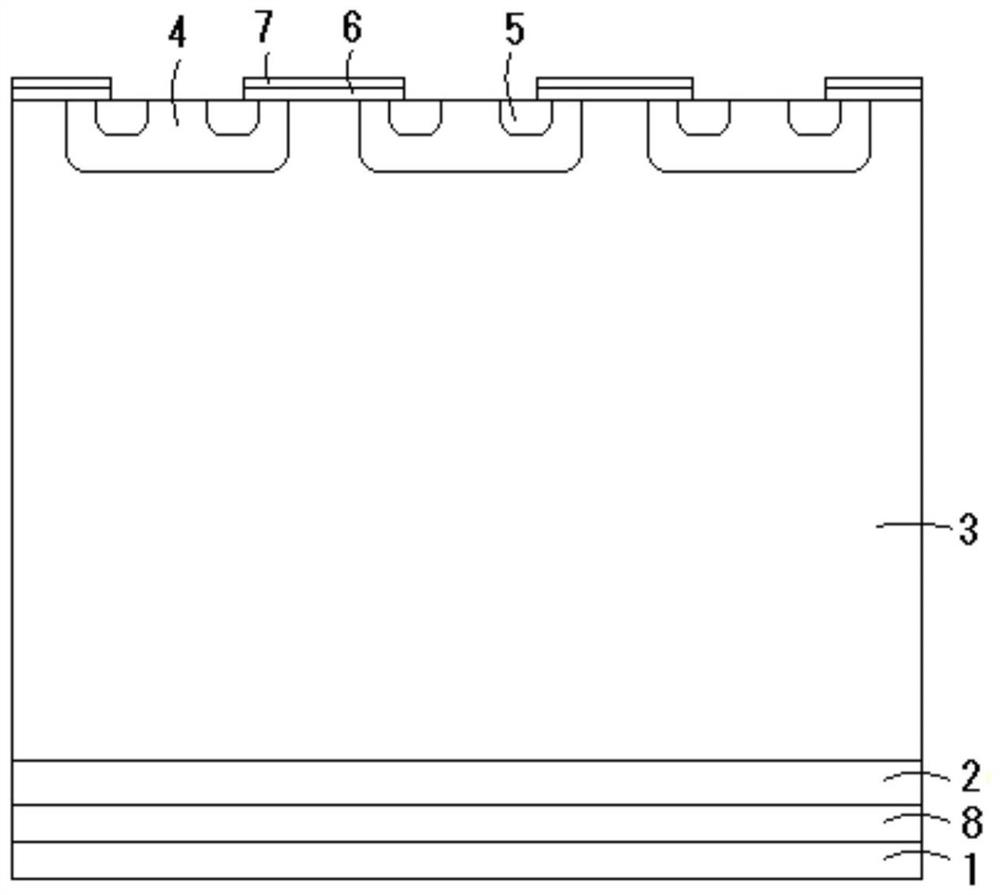

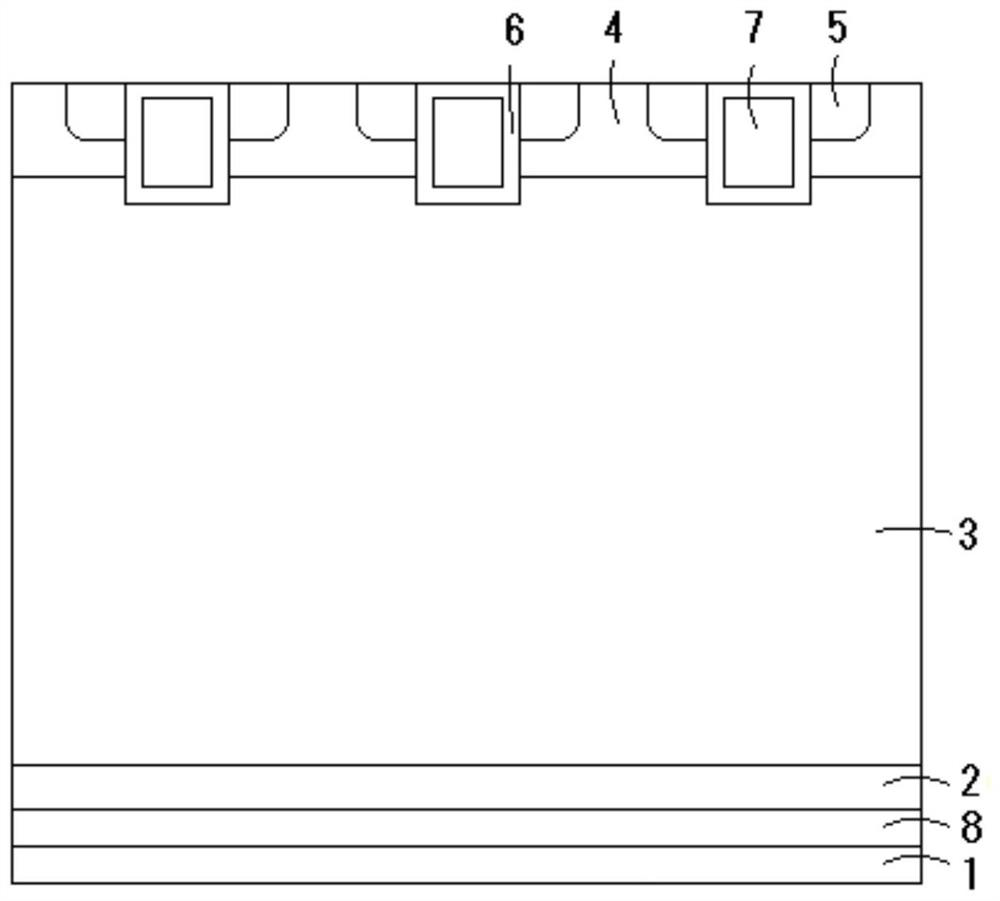

[0032] figure 1 It is a schematic cross-sectional view of the first type of upper surface planar structure insulated gate bipolar transistor of the present invention, combined below figure 1 The semiconductor device of the present invention will be described in detail.

[0033] An insulated gate bipolar transistor, the rear P+ emitter region 1 is made of P conductivity type polysilicon material, the thickness is 0.3-300um, and the doping concentration of boron atoms is 5E17cm -3; The N-type adjustment region 8 is made of N-conduction type polysilicon material with a thickness of 0.3-300um and a doping concentration of phosphorus atoms of 1E17cm -3 , located on the back P+ emitter region; N+ buffer layer 2, located on the N-type adjustment region, is a semiconductor silicon material of N conductivity type, and the doping concentration of phosphorus atoms is 5E13cm -3 ~1E16cm -3 , with a thickness of 10um; N-base region 3, located on the N+ buffer layer 2, is a semiconductor ...

Embodiment 2

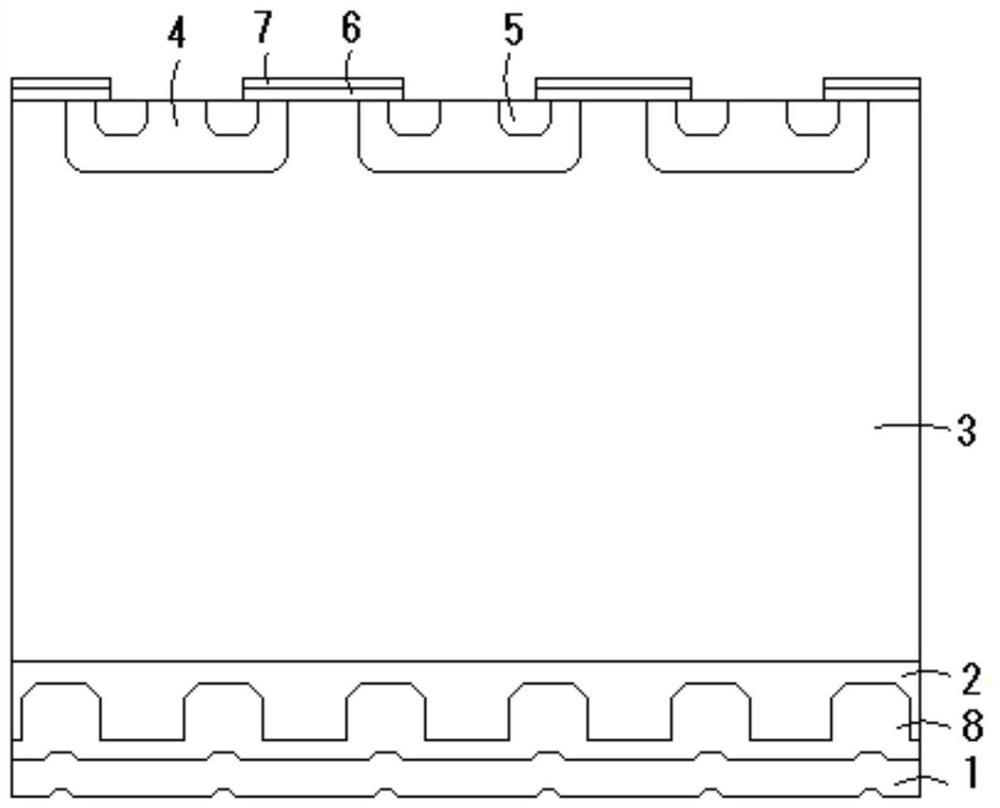

[0038] image 3 It is a cross-sectional view of the second back trench structure insulated gate bipolar transistor of the present invention, combined below image 3 The semiconductor device of the present invention will be described in detail.

[0039] An insulated gate bipolar transistor, the rear P+ emitter region 1 is made of P conductivity type polysilicon material, and the doping concentration of boron atoms is 5E17cm -3 , located on the lower surface of the N-type adjustment region 8; the N-type adjustment region 8 is made of N-conduction type polysilicon material, and the doping concentration of phosphorus atoms is 1E17cm -3 , located in the back trench in the N+ buffer layer 2; the N+ buffer layer 2, located above the N-type adjustment region, is a semiconductor silicon material of N conductivity type, and the doping concentration of phosphorus atoms is 5E13cm -3 ~1E16cm -3 , with a thickness of 30um, multiple trenches are set on the back of the N+ buffer layer; the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com