Formation method of semiconductor structure

A semiconductor and graphics technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical solid-state devices, etc., can solve problems such as circuit connection reliability that greatly affects the normal operation of semiconductor devices, etc., to optimize electrical performance and reduce leakage. The effect of the probability of the current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0010] Currently formed devices still suffer from poor performance. The reasons for the poor performance of the device are analyzed in conjunction with a method of forming a semiconductor structure.

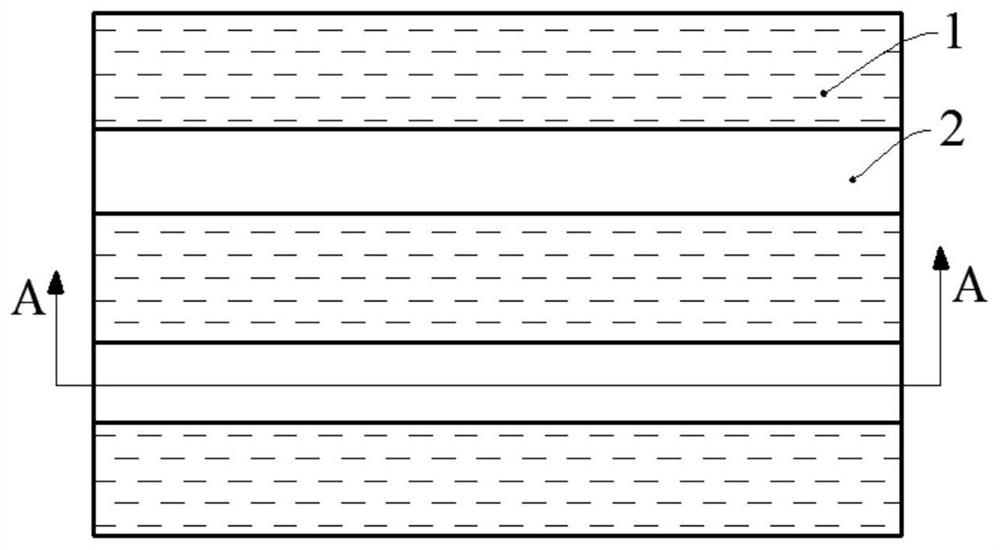

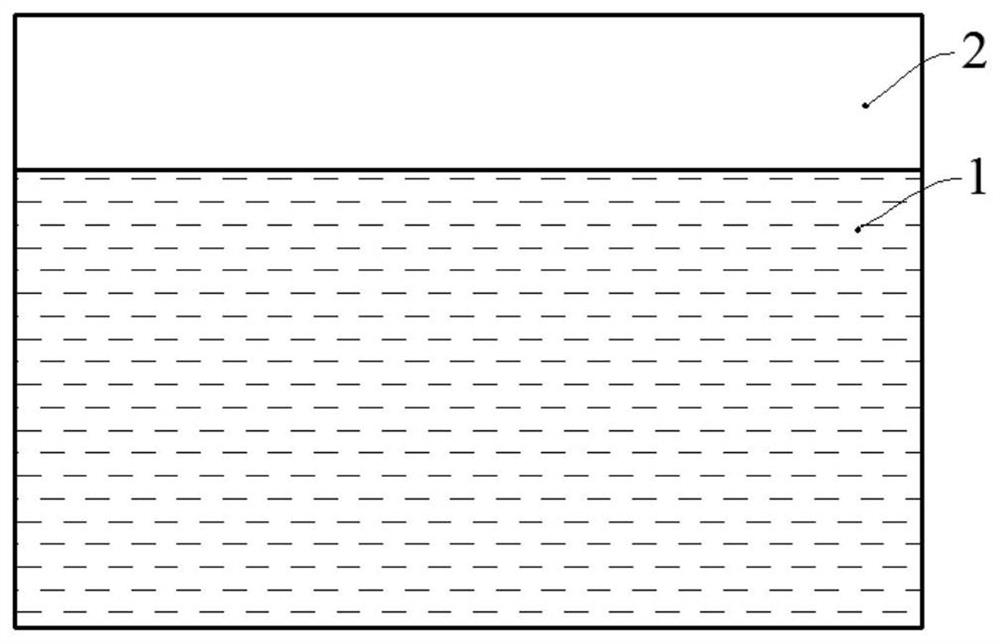

[0011] Figure 1 to Figure 10 , is a structural schematic diagram corresponding to each step in a method for forming a semiconductor structure.

[0012] Such as figure 1 and figure 2 as shown, figure 2 for figure 1 A cross-sectional view in the AA direction provides a base, which includes a substrate 1 and a pattern material layer 2 on the substrate 1 .

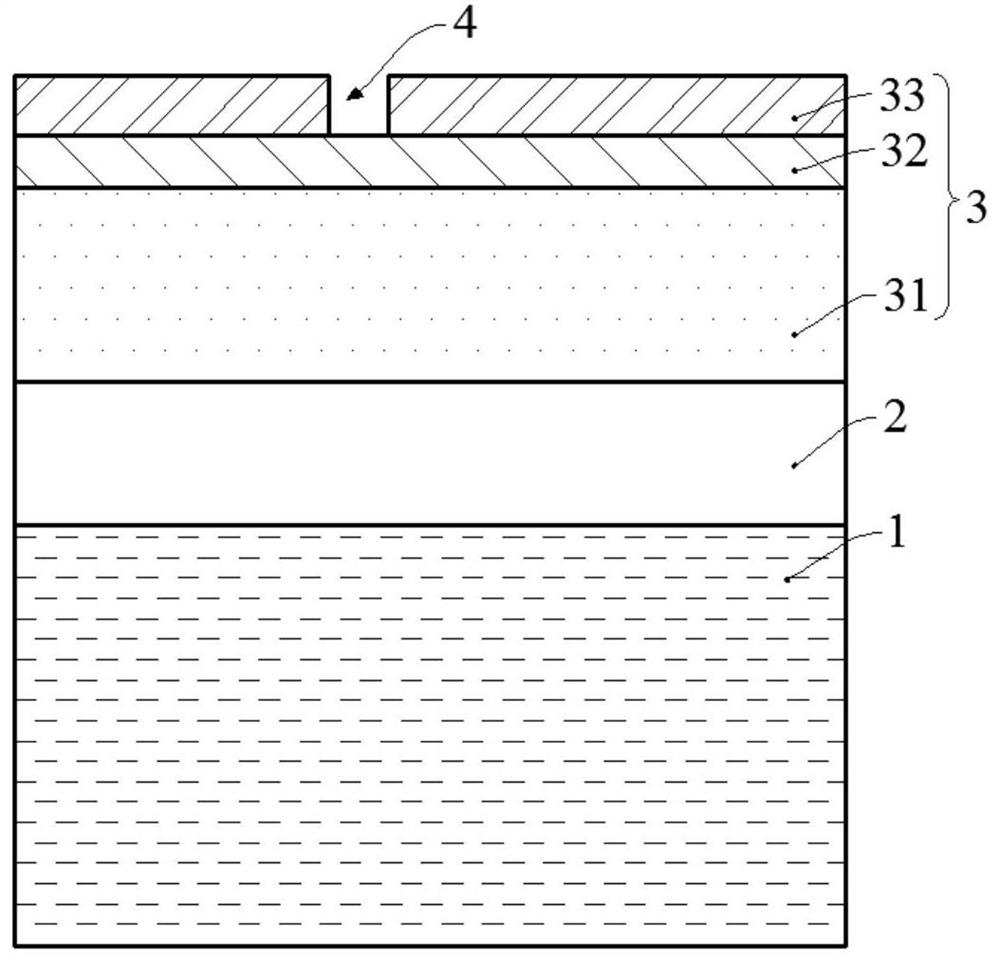

[0013] Such as image 3 As shown, the first mask layer 3 covering the pattern material layer 2 and the substrate 1 is formed, the first mask layer 3 includes a first organic material layer 31, a The first anti-reflection coating 32 and the first photoresist layer 33 on the first anti-reflection coating 32 , the first photoresist layer has an opening 4 therein.

[0014] Such as Figure 4 As shown, the pattern material...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com